随着越来越多的电子设备实现现代生活的智能化/互联化,强烈要求提高这些设备的智能化和计算能力这将敏感的电子元件推向了从未真正打算使用的领域。工业和汽车等领域要求CPU和SoC在高温和高工作负载下长时间完美运行。这些用例给ASIC设计者带来了挑战,这些同时对SIPI提出了更高的需求。

车载芯片和消费类芯片差异

为了满足汽车市场的可靠性、温度、缺陷和安全标准,平台和SoC必须符合比消费级产品更严格的规范。下表是车载芯片与消费类芯片的主要差异,这些高需求下对芯片的物理设计需要有更高的要求,也对SI和PI的设计引入了不小的挑战。

车载芯片SIPI tradeoff设计

尽管车载芯片的设计对SIPI的设计都会产生重大的影响,其中PI性能的退化程度要大得多。缓解PI性能瓶颈的策略也会产生不利的副作用,会对各种I/O接口的SI性能产生影响。这就造成了在车载芯片设计时一个需要考虑整体系统性能并在SIPI性能之间做出tradeoff。

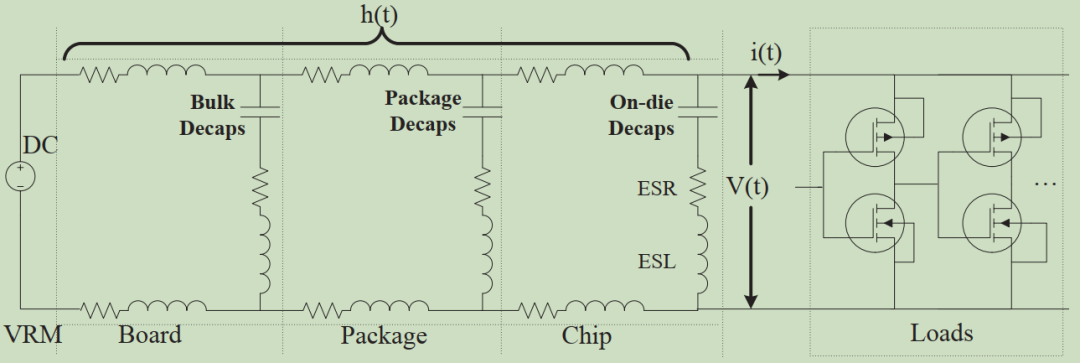

A. PI的恶化

电源PDN网络是从主电源输送到位于ASIC上的有源电路IP。PDN包括PMU/DCDC/LDO、滤波器、去耦电容器和电源平面,PDN网络将功率从电源输送到负载。对于现代CPU和SOC,需要对PDN进行有目的的工程设计,以提供具有可控噪声的稳定电压,从而确保核心逻辑和I/O接口的正确可靠操作。同时汽车芯片上关于封装上电容去耦解决方案的也是满足汽车芯片电源需求的主要解决策略。对于汽车芯片高算力需求,数字IP功耗也越来越大,对PI性能的要求和设计越来越高,而PI主要的无源优化手段就是PDN的电容组合设计,其中对噪声优化明显的时中高频电容也就是封装和DIE侧的电容组合。而封装贴容常见的两种方式,即表贴电容和背贴电容;这两种里面效果比较好的时背贴电容,电容到bump的ESL最小,电容收益影响小,缺点时需要占用BGA资源,可用的空间比较小;而表贴电容虽然到bump ESL比背贴大,但是封装可以利用的电容物理资源比较大,组合会更丰富一些。

B. 贴容需要考虑的几点

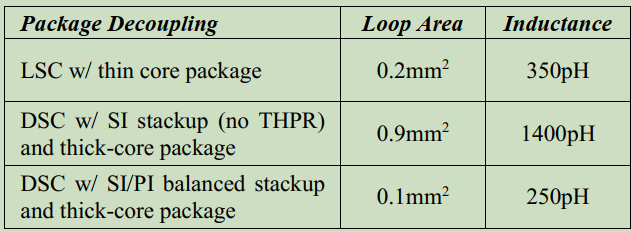

由于电容物理结构容易出现cracking和delamination工程问题,目前BLUF材料的使用帮助了电容的选择,另外加上车规电容的大物理尺寸和温度特性要求,这迫使PI电源设计选择表贴电容作为封装上去耦的常用手段。另一个方面,IHS具有隔离区(KOZ)要求,限制放置并减少可物理摆放的电容总数。AEC-Q200合格电容器的外壳尺寸更大,也降低了可能的总封装电容数量。最后一个方面是关于封装叠层里面的Core层厚度影响,与薄core层或无core层封装相比,厚core层封装需要更大、更长的镀通孔过孔(PTH)。当考虑硅和电容之间的高频去耦路径时,希望避免长的电感性PTH。实现这一点的唯一方法是迫使将硅连接到电容的所有电源平面(和接地回路)位于封装的上半部分。下面显示了各种封装去耦选项的近似回路返回面积和电感值(针对单个电容器测量)。可以看出,具有厚core层且没有THPR的情况由于多个PTH穿过厚core封装材料导致性能降低。

LPDDR4 SIPI tradeoff设计评估例子

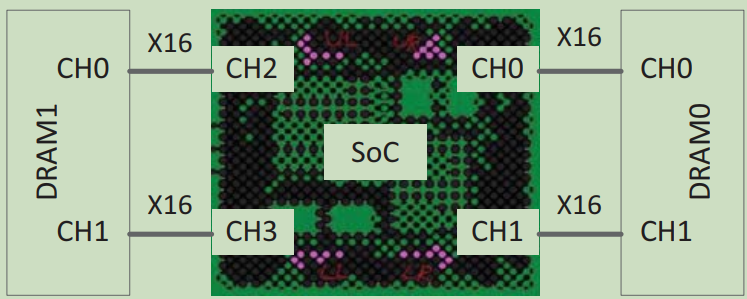

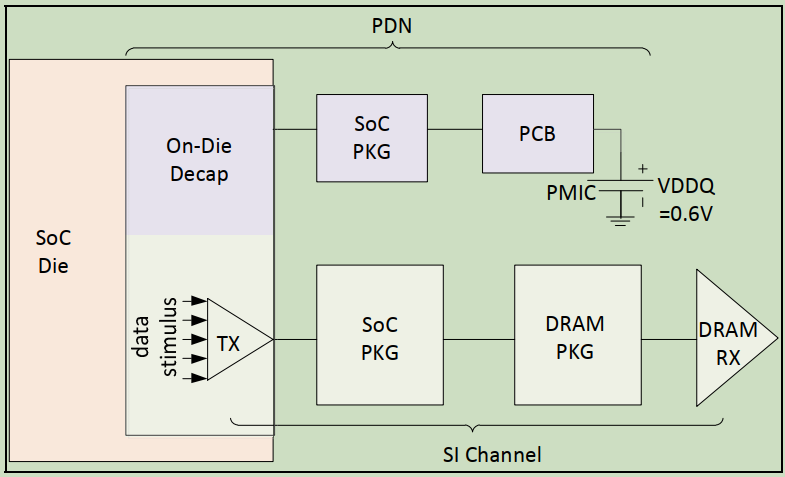

如下是基于LPDDR4的SIPI联合仿真来看下PI对SI的影响,对信号质量的裕量影响,评估链路如下:

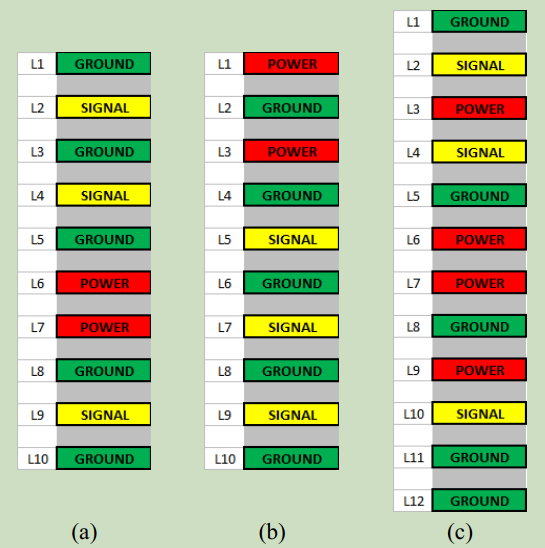

如前所述,汽车芯片的大算力、高功耗使PI性能下降最多,需要改进PDN以满足芯片设计目标。这儿我们考虑了不同封装叠层设计的PDN设计和SI情况,LSC代表封装背贴电容,DSC代表封装表贴电容,同时考虑SI的不同设计做了对比,如下叠层图;并将其与仅针对SI而无THPR优化的堆叠的情况( 绿色) 以及同时针对SI和PI( 包括 THPR)优化的层叠设计情况进行了比较(蓝色)。

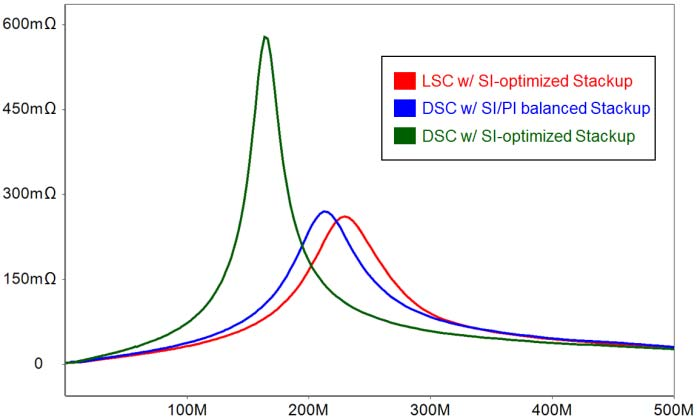

下图显示了上表中不同去耦选项的PDN阻抗与频率的关系。封装背贴电容和考虑好的SI叠层设计时PDN时做好的,而如果为了兼顾SIPI性能,则需要考虑SI性能衰减一点,做到均衡设计。

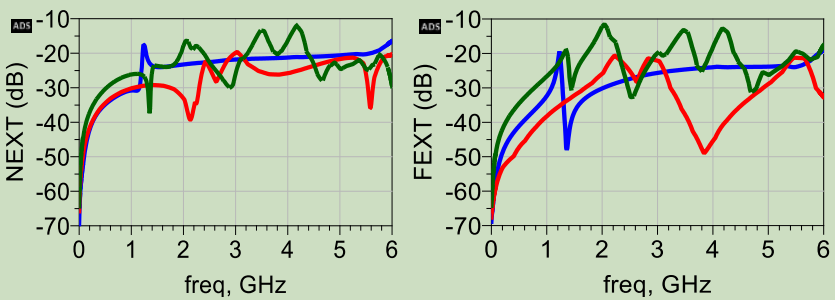

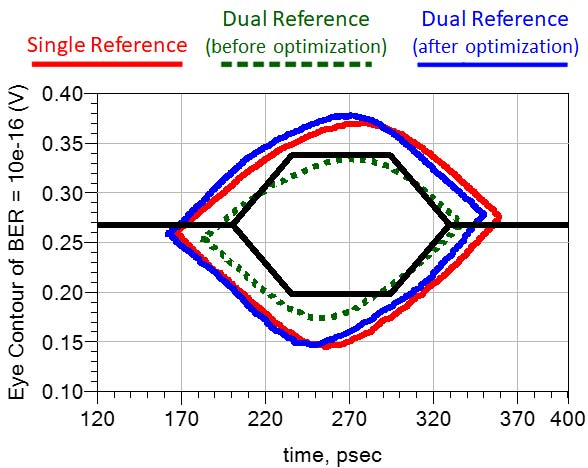

为了评估平衡设计对SI信道性能的影响,在三种不 同的SoC设计上对一个byte通道进行了对比仿真。如下图分别与上图PDN对应。从眼图可以清楚地看到由于在电源平面分裂上共享相同路径的返回电流而导致的更高的串扰和眼睛闭合。LPDDR4 RX掩模(0.55UI/140mV)用于定义timing和幅度裕量。一小部分恶化是由厚core层导致的串扰增加引起的,但大部分恶化是由车载芯片的需求而导致对PI冲击大造成的。双重参考、分裂平面、过孔设计不当等都有可能导致信号眼图质量不好。

总结

在高性能计算平台下对参与产品开发的SI和PI团队提出了独特的更高要求的挑战。这就需要SIPI联合设计以达到最优的系统设计。

1114

1114

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?