一、ARM概述

二、ARM架构

2.1 ARM历史版本

| 内核版本号 | SOC版本号 | 芯片型号(以三星为例) |

| ARMv1 | | |

| ARMv2 | | |

| ARMv3 | | |

| ARMv4 | ARM7、ARM9 | S3C44B0 |

| ARMv5 | ARM9+xScale | S3C2440、S3C2410 |

| ARMv6 | ARM11 | S3C6410 |

|

ARMv7

|

Cortex-M

Cortex-A

Cortex-R

| |

| Cortex-A7 | 联发科MT6589 | |

| Cortex-A8 | S5PV210/S5PC110、高通MSM8255 | |

| Cortex-A9 | Exynos4410、Exynos4412、Tegra2/3 | |

| Cortex-A15 | Exynos5250、Exynos5450 | |

| Cortex-A53、A57 | 高通骁龙815/410 |

2.2 ARM工作模式

| 工作模式 | 触发条件 | CPSR寄存器中的模式位[0~4位](默认状态下) |

|---|---|---|

| User | 非特权模式,大部分任务执行在这种模式 | 10000(0xD0) |

| FIQ | 当一个高优先级(fast)中断产生时将会进入这种模式 | 10001(0xD1) |

| IRQ | 当一个低优先级(normal)中断产生时将会进入这种模式 | 10010(0xD2) |

| Supervisor | 当复位或软中断指令执行时将会进入这种模式 | 10011(0xD3) |

| Abort | 当存取异常时将会进入这种模式 | 10111(0xD7) |

| Undefined | 当执行未定义指令时会进入这种模式 | 11011(0xDB) |

| System | 使用和User模式相同寄存器集的特权模式 | 11111(0xDF) |

其中除用户模式外都称之为特权模式,ARM上电或复位后,默认进入Supervisor工作模式

2.3 ARM寄存器

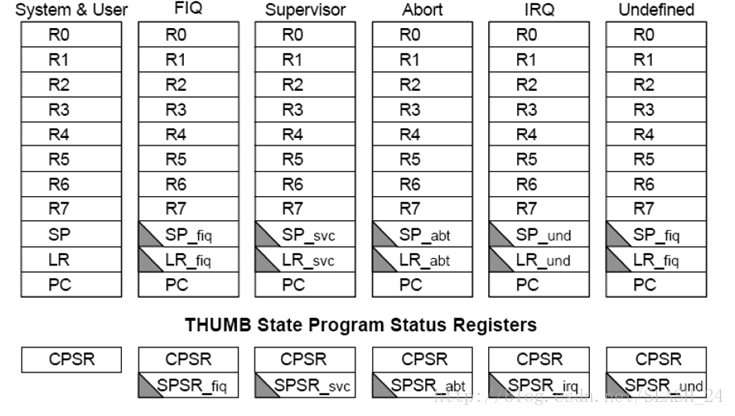

2.3.1 ARM状态下的寄存器组

通用寄存器包括R0~R15,可以分为三类:

1. 未分组寄存器R0~R7

2. 分组寄存器R8~R14

3. 程序计数器R15

未分组寄存器R0~R7:

在所有的运行模式下,未分组寄存器都指向同一个物理寄存器,它们未被系统用作特殊的用途,因此,在中断或异常处理进行运行模式转换时,由于不同的处理器运行模式均使用相同的物理寄存器,可能会造成寄存器中数据的破坏。

分组寄存器R8~R14

对于分组寄存器,它们每一次所访问的物理寄存器与处理器当前的运行模式有关。

对于R8~R12来说,每个寄存器对应两个不同的物理寄存器,当使用fiq模式时,访问寄存器R8_fiq~R12_fiq;当使用除fiq模式以外的其他模式时,访问寄存器R8_usr~R12_usr。

对于R13、R14来说,每个寄存器对应6个不同的物理寄存器,其中的一个是用户模式与系统模式共用,另外5个物理寄存器对应于其他5种不同的运行模式。

采用以下的记号来区分不同的物理寄存器:

R13_<mode>

R14_<mode>

其中,mode为以下几种模式之一:usr、fiq、irq、svc、abt、und。

寄存器R13在ARM指令中常用作堆栈指针,但这只是一种习惯用法,用户也可使用其他的寄存器作为堆栈指针。而在Thumb指令集中,某些指令强制性的要求使用R13作为堆栈指针。

由于处理器的每种运行模式均有自己独立的物理寄存器R13,在用户应用程序的初始化部分,一般都要初始化每种模式下的R13,使其指向该运行模式的栈空间,这样,当程序的运行进入异常模式时,可以将需要保护的寄存器放入R13所指向的堆栈,而当程序从异常模式返回时,则从对应的堆栈中恢复,采用这种方式可以保证异常发生后程序的正常执行。

寄存器R14也称作子程序连接寄存器(Subroutine Link Register)或连接寄存器LR。当执行BL子程序调用指时,R14中得到R15(程序计数器PC)的备份。其他情况下,R14用作通用寄存器。与之类似,当发生中断或异常时,对应的分组寄存器R14_svc、R14_irq、R14_fiq、R14_abt和R14_und用来保存R15的返回值。

寄存器R14常用在如下的情况:在每一种运行模式下,都可用R14保存子程序的返回地址,当用BL或BLX指令调用子程序时,将PC的当前值拷贝给R14,执行完子程序后,又将R14的值拷贝回PC,即可完成子程序的调用返回。R14也可作为通用寄存器。

寄存器R15用作程序计数器(PC)。在ARM状态下,位[1:0]为0,位[31:2]用于保存PC;在Thumb状态下,位[0]为0,位 [31:1]用于保存PC;虽然可以用作通用寄存器,但是有一些指令在使用R15时有一些特殊限制,若不注意,执行的结果将是不可预料的。

R15虽然也可用作通用寄存器,但一般不这么使用,因为对R15的使用有一些特殊的限制,当违反了这些限制时,程序的执行结果是未知的。

由于ARM体系结构采用了多级流水线技术,对于ARM指令集而言,PC总是指向当前指令的下两条指令的地址,即PC的值为当前指令的地址值加8个字节。需要注意的是,当使用指令STR/STM保存R15时,保存的可能是当前指令地址值加8字节,也可能保存的是当前指令地址加12字节。到底是哪种方式,取决于芯片具体设计方式。无论如何,在同一芯片中,要么采用当前指令地址加8,要么采用当前指令地址加12,不能有些指令采用当前指令地址加8,另一些指令采用当前指令地址加12。因此对于用户来说,尽量避免使用STR/STM指令来保存R15的值。当不可避免这种使用方式时,可以先通过一些代码来确定所用的芯片使用的是哪种实现方式。

在ARM状态下,任一时刻可以访问以上所讨论的16个通用寄存器和一到两个状态寄存器。在非用户模式(特权模式)下,则可访问到特定模式分组寄存器,图2.3说明在每一种运行模式下,哪一些寄存器是可以访问的。

程序状态寄存器R16用作CPSR(Current Program Status Register,当前程序状态寄存器),CPSR可在任何运行模式下被访问,它包括条件标志位、中断禁止位、当前处理器模式标志位,以及其他一些相关的控制和状态位。

每一种运行模式下又都有一个专用的物理状态寄存器,称为SPSR(Saved Program Status Register,备份的程序状态寄存器),当异常发生时,SPSR用于保存CPSR的当前值,从异常退出时则可由SPSR来恢复CPSR。由于用户模式和系统模式不属于异常模式,他们没有SPSR,当在这两种模式下访问SPSR,结果是未知的。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?