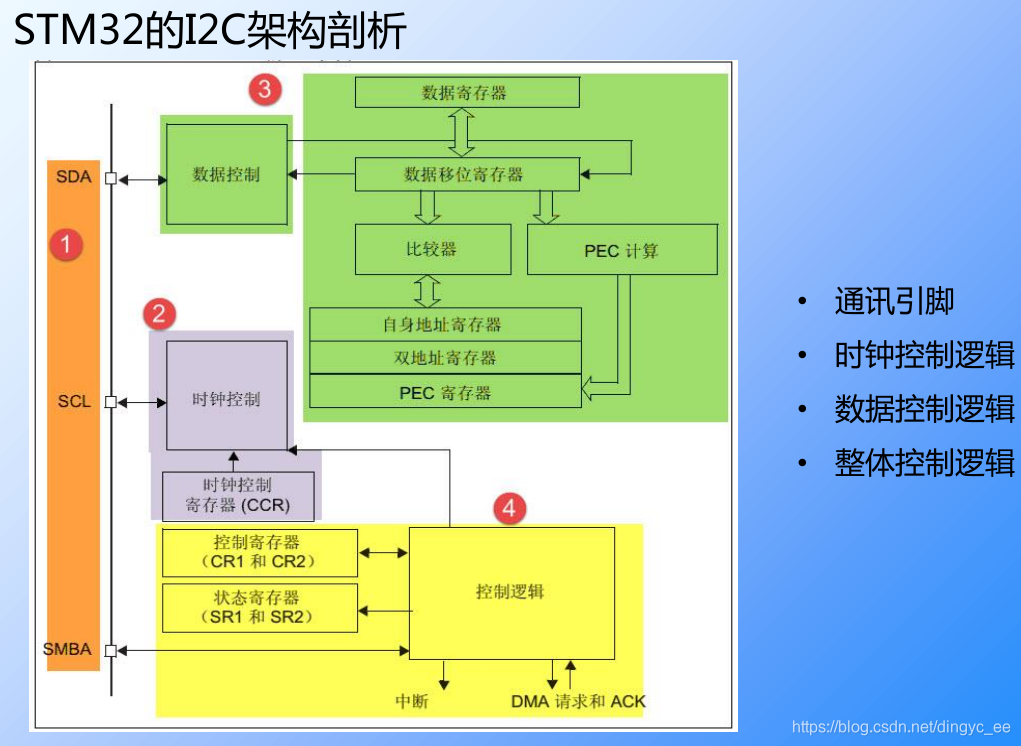

STM32的I2C特性及架构:

1 硬件实现协议:

由STM32的I2C片上外设专门负责实现I2C通讯协议,只要配置好该外设,它就会自动根据协议要求产生通讯信号,收发数据并缓存起来,CPU只要检测该外设的状态和访问数据寄存器,就能完成数据收发。这种由硬件外设处理I2C协议的方式减轻了CPU的工作,且使软件设计更加简单。

stm32的硬件IIC,在某些情况下会出现错误,但也没有必要去纠结这个问题。

2 软件模拟协议:使用CPU直接控制通讯引脚的电平,产生出符合通讯协议标准的逻辑。

STM32的I2C外设可用作通讯的主机及从机,支持100Kbit/s和400Kbit/s的速率,支持7位、10位设备地址,支持DMA数据传输,并具有数据校验功能。

stm32硬件IIC的内部:

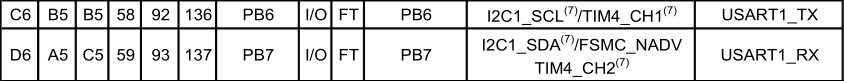

1 通讯引脚

IIC1

IIC2

![]()

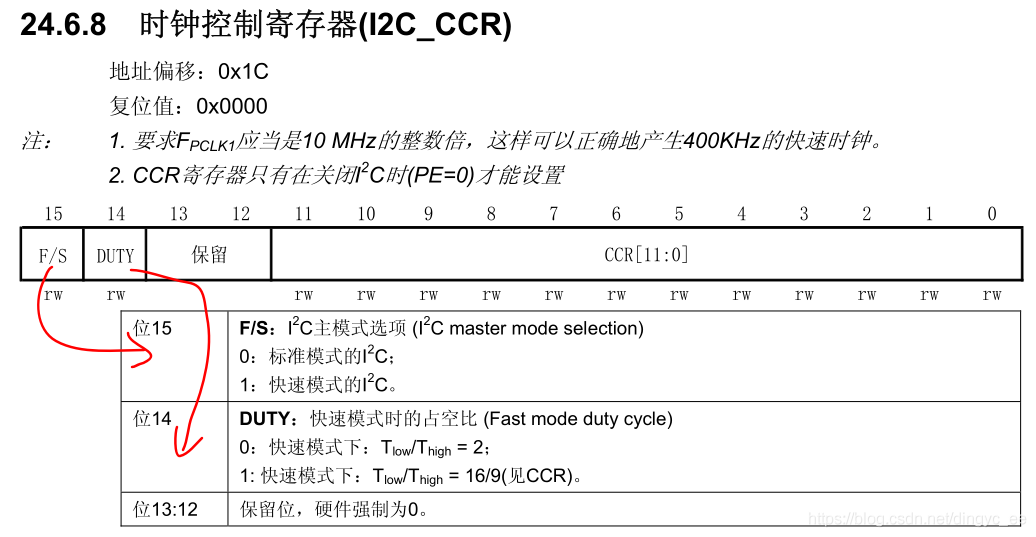

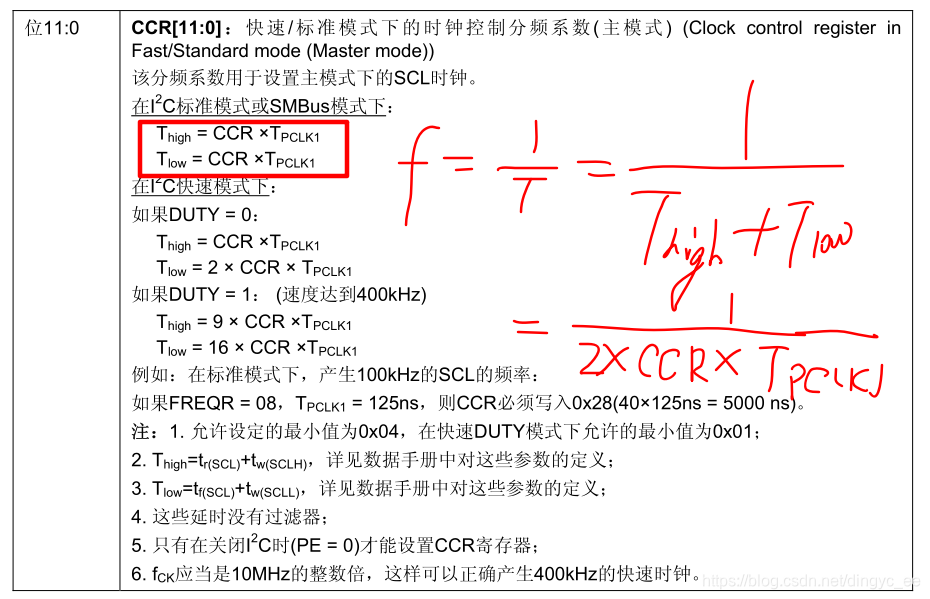

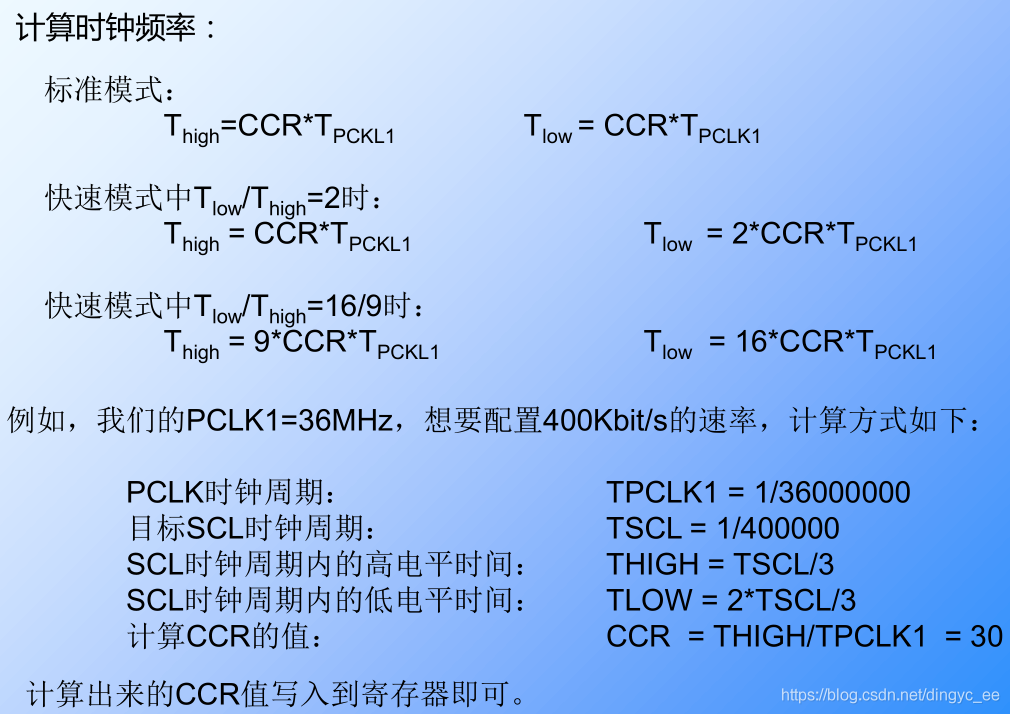

2 时钟控制逻辑

时钟控制逻辑,直接通过一些信号线与SCL引脚相连,通过这些硬件逻辑控制SCL线。时钟控制寄存器CCR,配置了SCL线的模式(标准模式100kHz,快速模式400kHz)、速度、占空比等参数,而实际上,标准库函数会帮我们计算好的,不需要每次都去手动计算。

这里计算分频系数,如何理解?

以标准模式为例,APB1总线的时钟信号PCLK1 = 36M,则T(PCLK1) = (1/36)ns,要产生100kHz的频率,则CCR必须写入的值为:2 * CCR * (1 / 36)ns = 100kHz,计算得到CCR = 180。

3 数据控制逻辑

连接到SDA引脚。

I2C的SDA信号主要连接到数据移位寄存器上,数据移位寄存器的数据来源及目标是数据寄存器(DR)、地址寄存器(OAR)、

PEC(帧校验)寄存器以及SDA数据线。

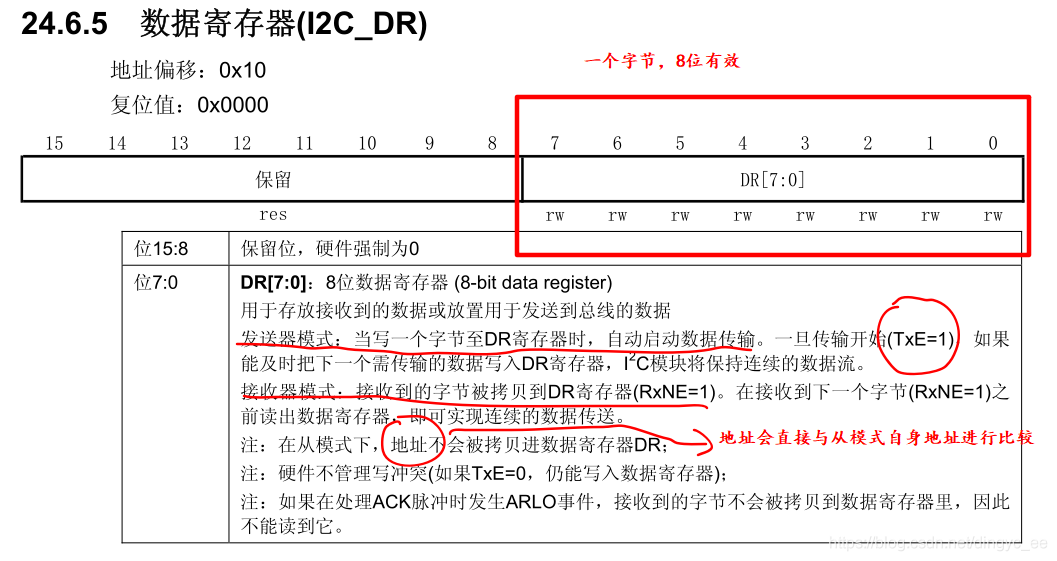

首先来看数据寄存器DR

当向外发送数据的时候,数据移位寄存器以“数据寄存器”为数据源,把数据一位一位地通过SDA信号线发送出去;

当从外部接收数据的时候,数据移位寄存器把SDA信号线采样到的数据一位一位地存储到“数据寄存器”中;

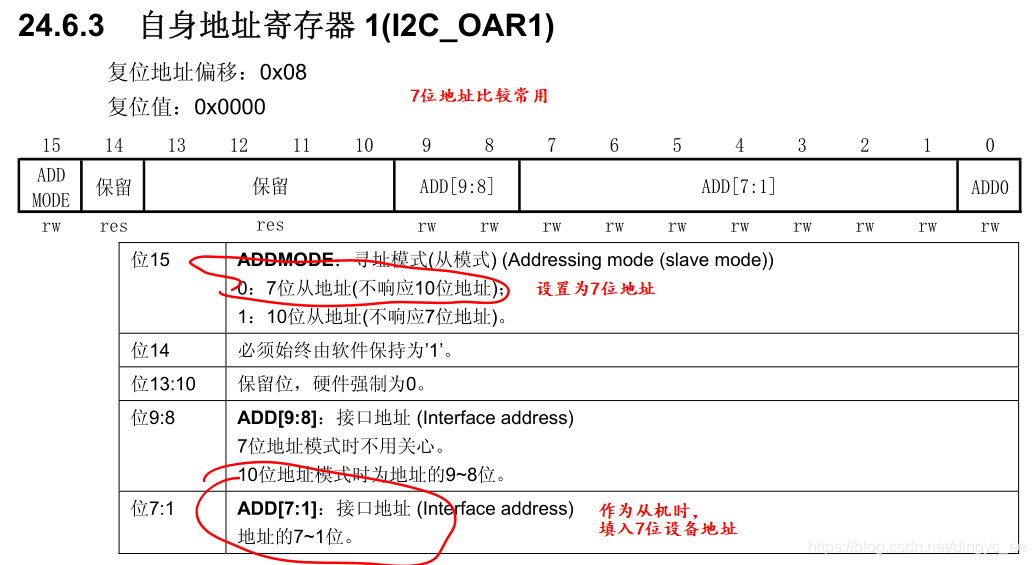

比较器的作用:IIC会有一个自身地址寄存器,用于作为从机。当作为从机时,必须要有IIC设备地址,通过软件配置可以写入到自身地址寄存器内。当主机寻址时,比较器会将地址比较,来确定主机是否在叫自己。

PEC寄存器:用于做数据校验,几乎不用。

4 整体控制逻辑

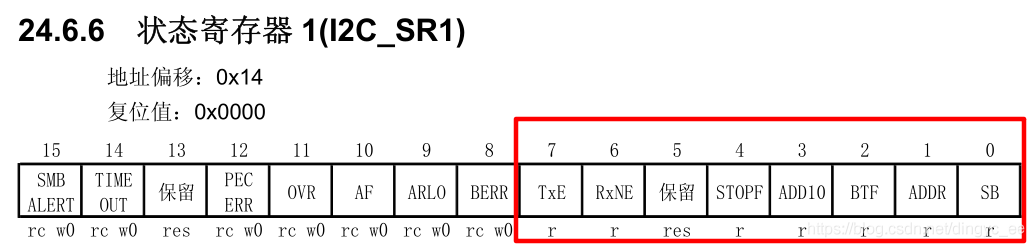

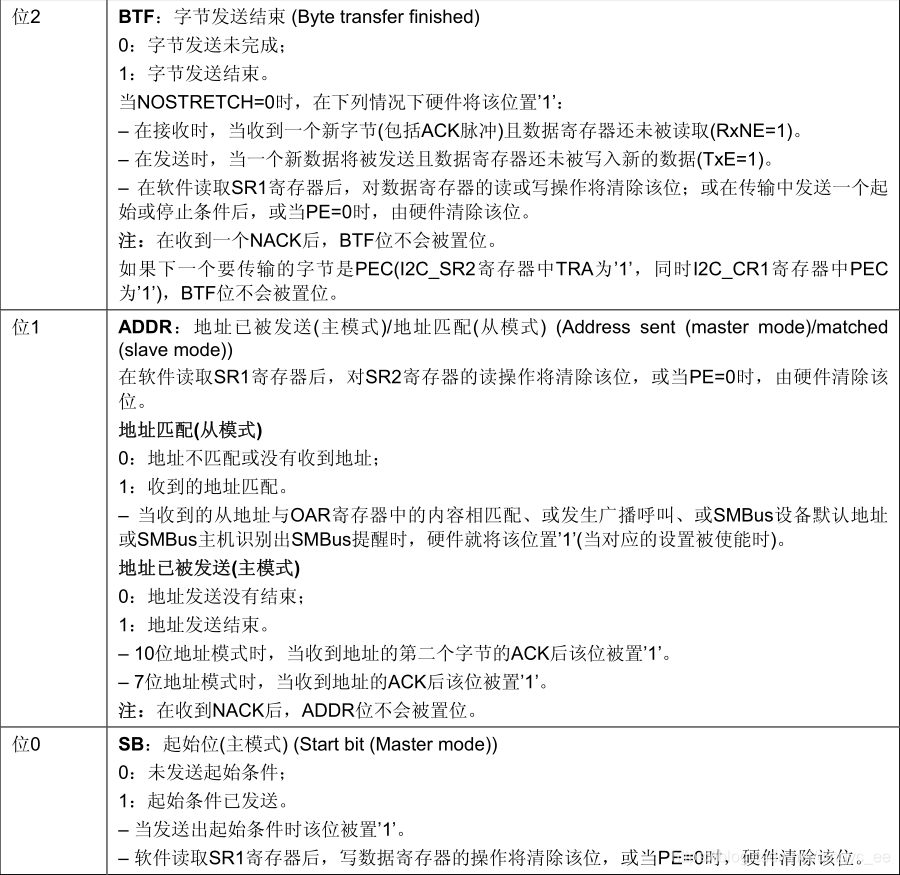

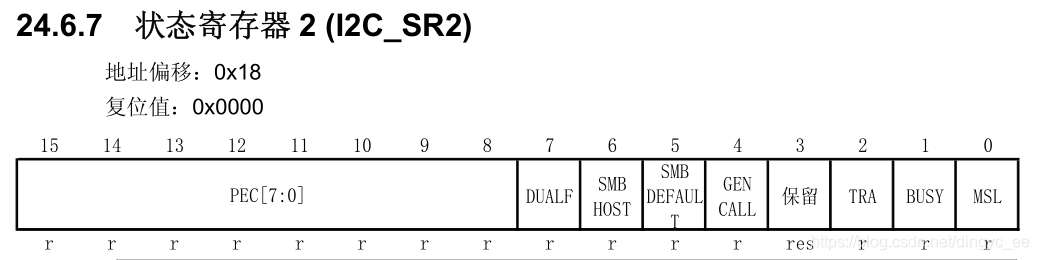

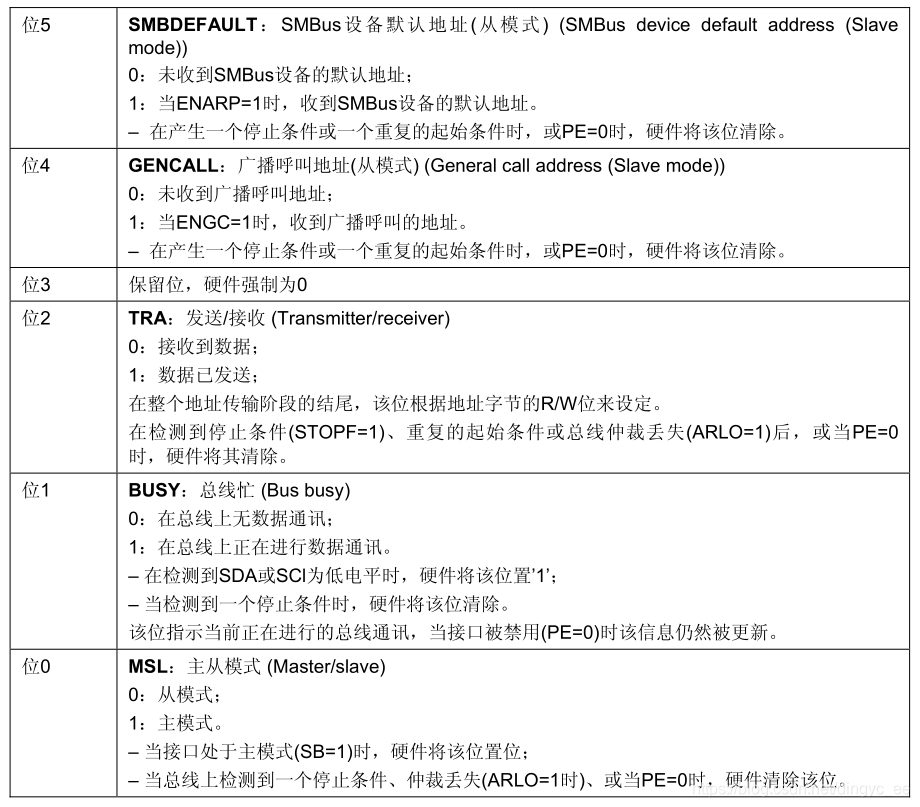

包含控制寄存器CR1 CR2和状态寄存器SR1 SR2。

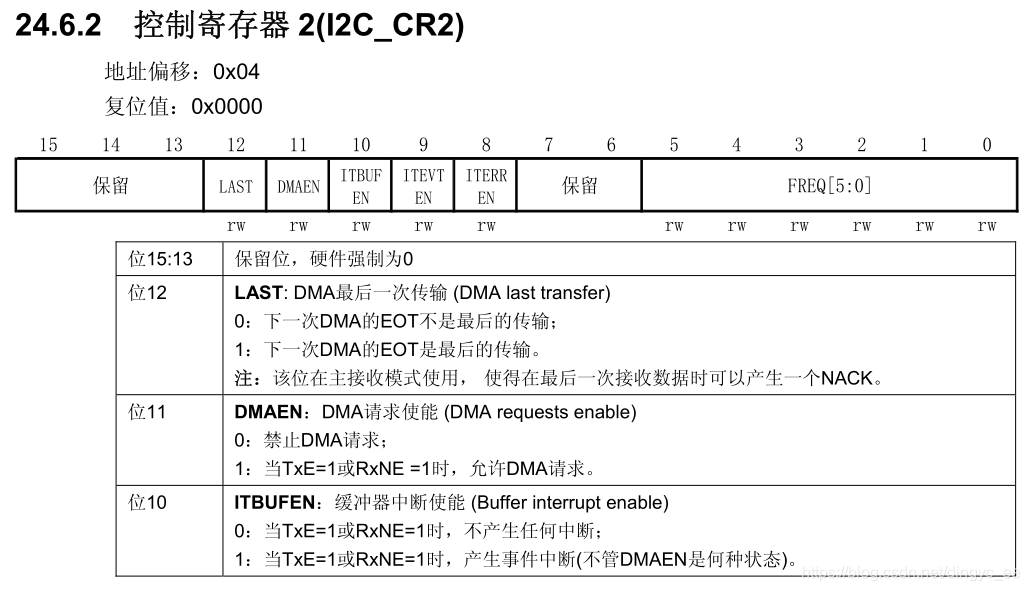

整体控制逻辑负责协调整个I2C外设,控制逻辑的工作模式根据我们配置的“控制寄存器(CR1/CR2)”的参数而改变。其中,CR1寄存器控制各种起始、结束的使能,CR2寄存器管理中断。

还有一个比较重要的地方:

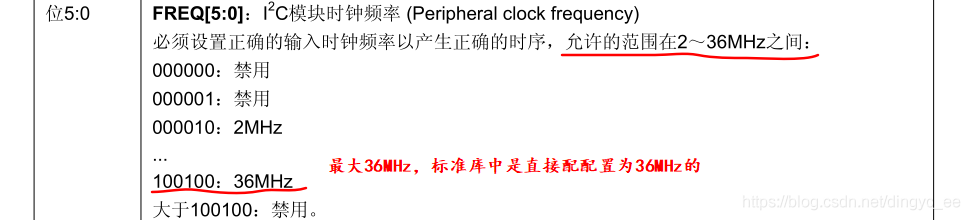

配置的是CR2寄存器的FREQ[5:0]位:

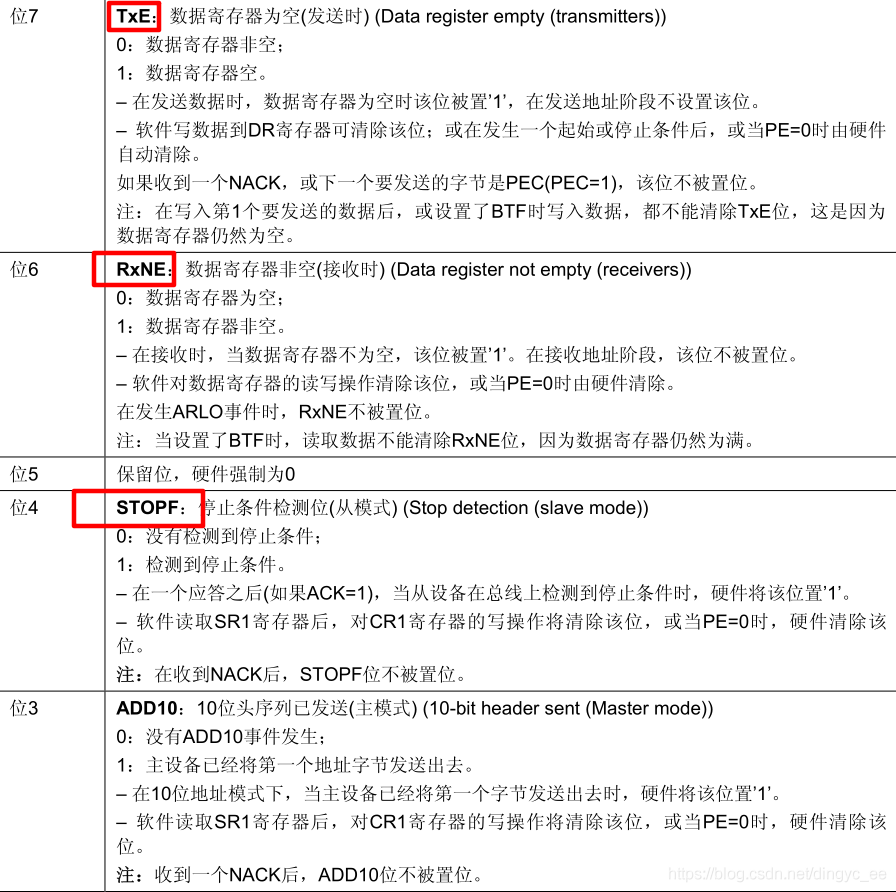

在外设工作时,控制逻辑会根据外设的工作状态修改“状态寄存器(SR1和SR2)”,只要读取这些寄存器相关的寄存器位,就可以了解I2C的工作状态,这个非常重要,我们编程时要参考这些标志位。接下来,详细的看一下每个标志位的意义。

这些标志位,对应了IIC的时序图种,产生的各种事件标志。

然后是状态寄存器CR2

7694

7694

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?