银行接口字段校验

内容:

1.字段非空校验。

2.字段是否符合接口文档规定类型或指定值。

3.判断数据是否是重复的。

作用:

1.防止垃圾数据进入业务系统。

2.接入银行较多,方便银行自己查找原因,减少不必要的工作。

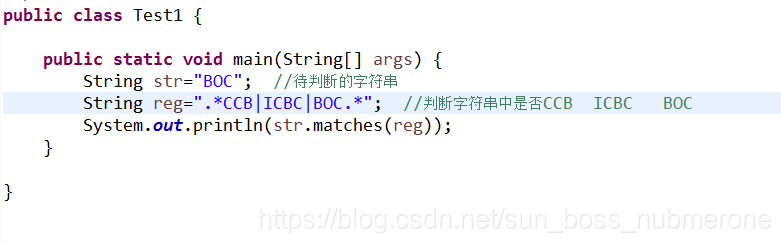

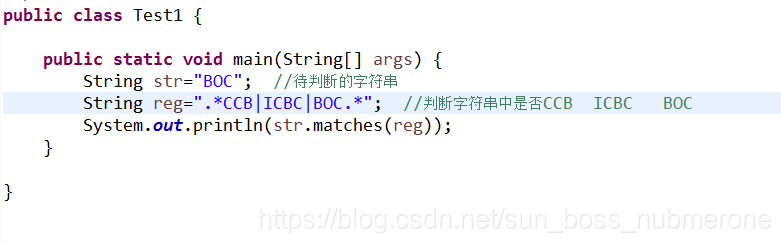

正则表达式:

1.判断是否是指定的值。

接口完整性思路及解决方法

最新推荐文章于 2021-11-11 14:39:11 发布

银行接口字段校验

内容:

1.字段非空校验。

2.字段是否符合接口文档规定类型或指定值。

3.判断数据是否是重复的。

作用:

1.防止垃圾数据进入业务系统。

2.接入银行较多,方便银行自己查找原因,减少不必要的工作。

正则表达式:

1.判断是否是指定的值。

1923

1923

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?