数字电路实验四选一数据选择器行为级模型

1、Verilog HDL的行为级建模主要是描述电路所具有的行为,或者说,是电路在哪些输人信号来临时会有什么样的输出,这种输入和输出的关系可以认为是电路的行为。所以,如果使用Verilog HDL的行为方式来对电路进行建模,那么实际的电路图并没有什么参考价值,因为抽象层次太低。这也是行为级建模的优点:不用过多关心底层电路的实现形式,只需关注该电路应该具有什么样的行为。例如.四选一数据选择器的代码就可以不看电路图,直接编写如下。

module MUX4x1(Y,A,B,C,D,S1,S0,En_);

output Y;

input A,B,C,D;

input S1,S0;

input En_;

reg Y;

always @(A or B or C or D or S1 or S0 or En_)

begin

if(En_==1'b0)

Y=0;

else

begin

case({S1,S0})

2'b00:Y=A;

2'b01:Y=B;

2'b10:Y=C;

2'b11:Y=D;

default:Y=0;

endcase

end

end

endmodule

测试代码如下:

module Test();

reg a, b, c, d, en_;

reg s1, s0;

wire y;

initial

begin

a=1'b0; b=1'b0; c=1'b0; d=1'b0;en_=1'b0;s0=1'b0;s1=1'b0;

#10 a=1'b0; b=1'b0; c=1'b0; d=1'b1;s0=1'b0;s1=1'b1;

#10 a=1'b0; b=1'b0; c=1'b1; d=1'b0;s0=1'b1;s1=1'b0;

#10 a=1'b0; b=1'b1; c=1'b0; d=1'b0;s0=1'b1;s1=1'b1;

#10 a=1'b1; b=1'b0; c=1'b0; d=1'b0;s0=1'b0;s1=1'b0;

#20 $stop;

end

always

#5 en_=~en_;

MUX4x1 mymux(y, a, b, c, d, s1, s0, en_);

endmodule

以上代码主要用了关键词always和if、case语句来完成的代码。

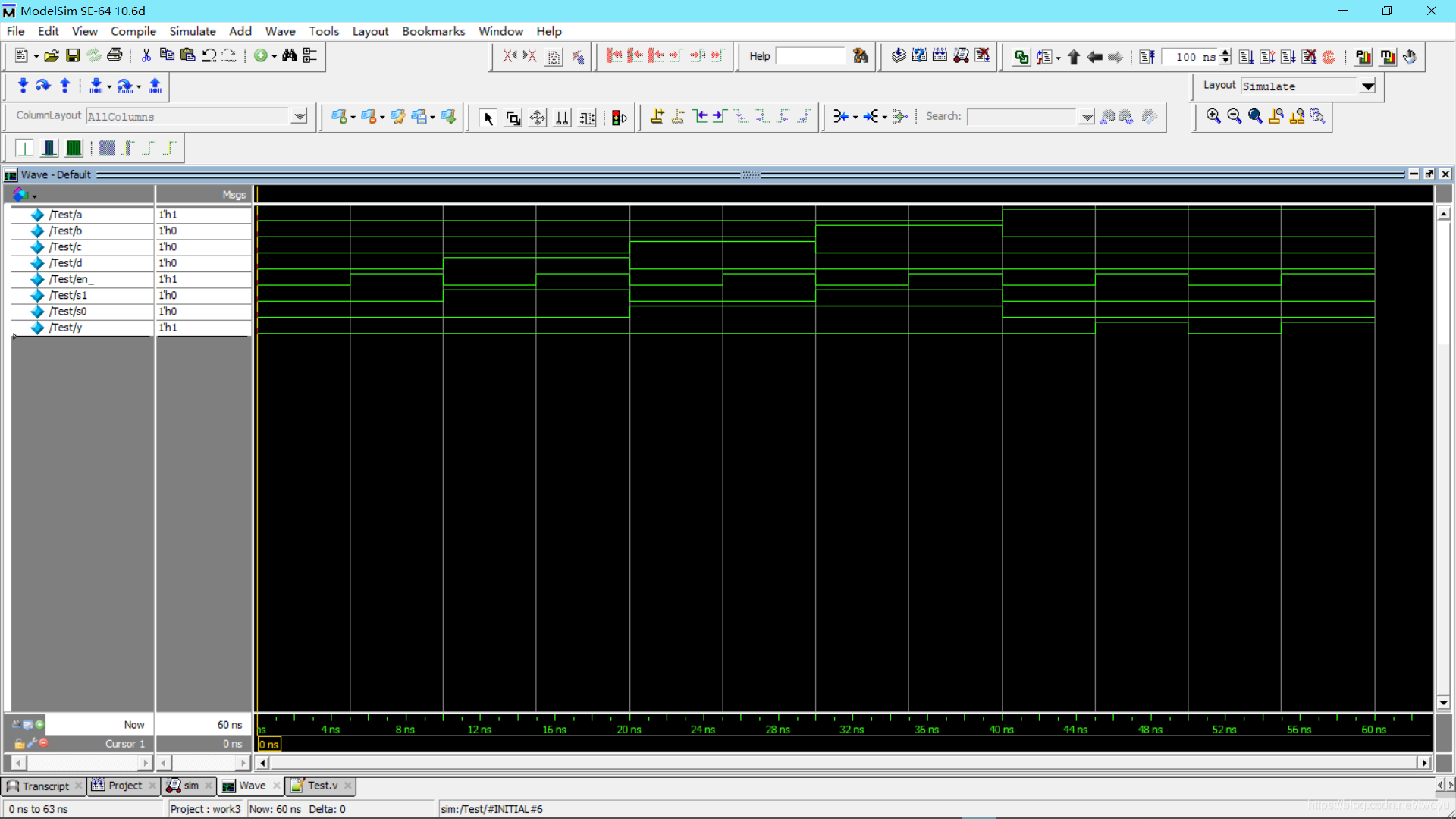

可由下面的仿真图验证其代码正确

2、视频地址

数字电路实验四选一数据选择器行为级模型视频

6732

6732

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?