想来想去还是从亚稳态开始吧,毕竟FPGA开发中不断与触发器打交道。

了解亚稳态首先要知道几个概念:1、同步逻辑、异步逻辑。2、二个词建立时间(Setup)以及保持时间(Hold)。其实时序分析的精华就是要分析每个触发器是否能够满足建立时间以及保持时间的要求。

首先解释:同步逻辑、异步逻辑:

简单的理解:在一个模块中用到的时钟与时钟之间有固定的相位关系 或者说时钟特征是可预测的被称为同步逻辑;在一个模块中用到的时钟彼此之间没有固定的相位关系,也就是时钟特征是不可预测的不知道的,称为异步逻辑。

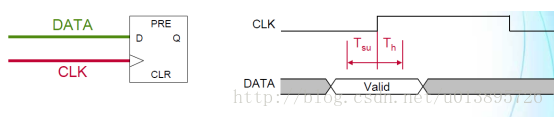

下面首先解释建立时间与保持时间:

建立时间:时钟上升沿到来之间数据所要保持稳定的时间;

保持时间:时钟上升沿到来之后数据所要保持稳定的时间。

好了了解这二个概念,接着就是一个问题什么叫做亚稳态(Metastability)

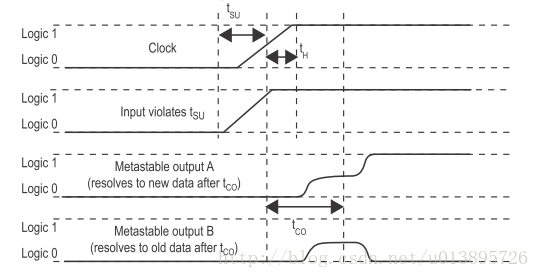

所有的数字器件(如FPGA)中的寄存器都定义了一个信号时序要求,满足这一要求的寄存器才能在输入端捕获数据在输出端输出数据。为了确保可靠的操作,寄存器输入端的数据必须在时钟上升沿到来之间保持一个最小的稳定时间(寄存器的建立时间 tsu)以及在时钟沿之后保持一个最短时间(寄存器保持时间tH)。寄存器在经过一定得时钟到输出延迟(tco)之后输出有效。如果信号传输违反了tsu以及tH的要求,寄存器的输出很可能会进入亚稳态的状态。

意思就是说触发器在时钟上升沿到来采样的时候数据必须在一个时间窗口内保持稳定,才能正确的被采样。如果违反就不能正常输出结果甚至不能输出一个确定的结果。

关于如何理解亚稳态Altera有一篇文章写的比较好

Altera原文链接:https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/wp/wp-01082-quartus-ii-metastability.pdf

下面就要考虑在什么时候带来亚稳态,以及亚稳态会带来哪些危害。

首先在同步逻辑中只要STA分析过了正常是不会遇到亚稳态问题的。由于在同步逻辑中STA分析以及保证了每个触发器都能满足自己的建立时间以及保持时间。那么也就是说亚稳态容易在异步逻辑中出现且不容易发现。

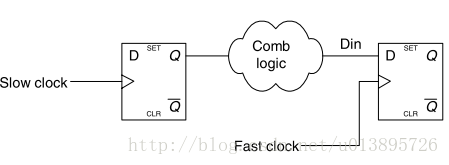

下面就解释为什么在异步逻辑中会发生亚稳态

上图所示是简单的在二个时钟域之间的信号传播。由慢时钟域到块时钟域的过程。

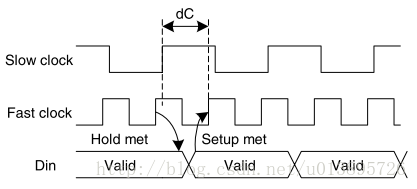

上图所示的时序图中可以看到 时钟沿之间的时钟间隔为dC。在这种情况之下可以发现数据的传播能够满足快时钟域的建立时间以及保持时间的要求。

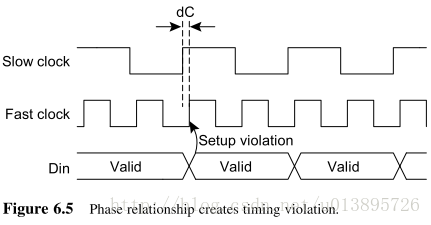

上图所示在此种相位关系的情况下,快时钟沿很难满足建立时间的要求。

由于异步时钟的不确定性所以造成在异步逻辑下很容易出现亚稳态。

至于亚稳态由哪些危害以及如何避免亚稳态的出现在下篇博客中会详细说明。

2076

2076

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?