原文地址:缓存着色技术(Cache Coloring) 作者:welkin

现代的cache设计大都采用set-association方式,即提高利用率又节省硬件。color只能提高这种cache的使用率。如果采用full-association则color没有用处。 而direct-mapped cache是set-association cache的一种特殊情况而已。

简单说来,整个内存被分为n个cache page,每个cache page包含数量固定的cache line。

整个cache被分为m个cache way,每个cache way有相同数量的cache line。

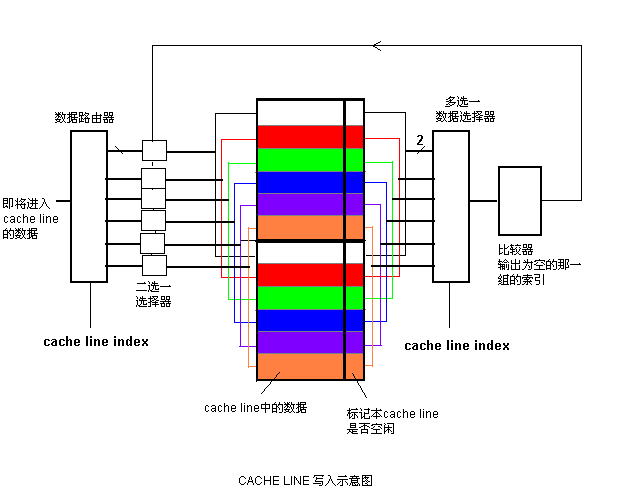

内存中的数据依据自己在内存中的cache line索引[getCacheLineIndex(addr)]只能被放入某一个cache way中相对应的cache line里面。假设已经从地址中提取出cache line的索引i,那么硬件会同时访问所有cache way的第i块cache line,找出一个拥有空闲行i的cache way,随后数据就可以放到这个空闲行中。如果m个cache way中都没有找到空闲的地i行,则启动淘汰策略,淘出一个空行~

整个cache被分为m个cache way,每个cache way有相同数量的cache line。

内存中的数据依据自己在内存中的cache line索引[getCacheLineIndex(addr)]只能被放入某一个cache way中相对应的cache line里面。假设已经从地址中提取出cache line的索引i,那么硬件会同时访问所有cache way的第i块cache line,找出一个拥有空闲行i的cache way,随后数据就可以放到这个空闲行中。如果m个cache way中都没有找到空闲的地i行,则启动淘汰策略,淘出一个空行~

比如一个cache有4个cache way(4路cache),每个cache way有16个cache line。某个数据结构的内存地址的cache line索引为2,则它只能被放入的某个cache way ( one of the 4 cache ways ) 的第2个cache line中。假使所有的cache way的第二个cache line都被使用,则必须换出某一个。

因此如果多个数据地址的cache line相同,即使cache中还有很大的空间,还是竞争激烈。

总结:

(1)多路cache(组相连cache),路间可选,路内固定

(2)对于M路N行Cache,当cache line索引为I(0<=I<N)的地址数超过M时,必然发生冲突,小于M时必然没有冲突

(3)Cache大小一定时,路数越多,发生冲突的概率越小,但电路也越复杂

为了避免Cache替换,不同的数据结构的地址对应的cache line索引最好不要相同,否则冲突的概率增大。

【more】

而使用slab的数据结构都是分配和释放频繁的小的数据结构,而且数目很多,比如dentry,如果没有color,他们在内存中相对于页的偏移量很可能相同,则其cache line索引也相同,对于x86这种2way 的cache结构,即使cache size很大,也一样使用率低下。color则将不同slab中的同样的数据结构的地址进行一个偏移,因此这些数据结构的cache line索引就错开了。从而能更好的利用cache

本文来自CSDN博客,转载请标明出处:http://blog.csdn.net/maray/archive/2008/12/25/3599845.aspx

7219

7219

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?