1 介绍

该接收机主要使用了PLL模块,通过相位比较使输出 与输入频率相关。

2结构

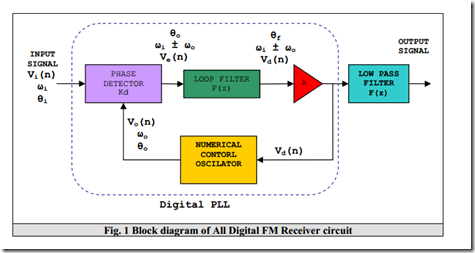

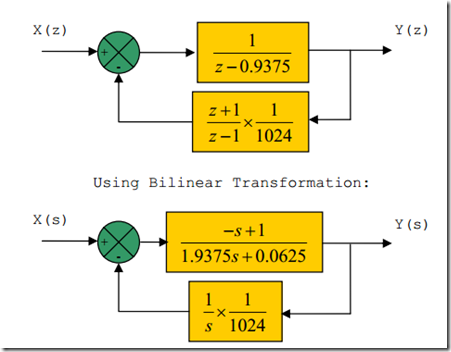

该接收机由一个PLL加一个低通滤波器组成,结构如Fig1:

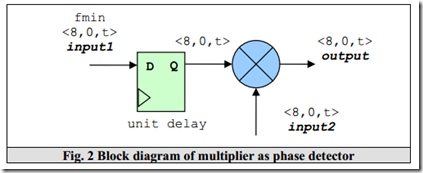

2.1鉴相器

鉴相器输出输入信号和NCO的相位差,这个模块使用了一个乘法器。输入信号![]() 是一个调频信号,可表示如下

是一个调频信号,可表示如下

PLL可以使NCO产生 一个和输入信号![]() 相同频率的输出正弦信号

相同频率的输出正弦信号![]()

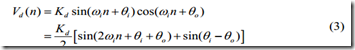

检波器输出是两个信号的乘积,用三角函数展开为

![]() 是鉴相器的增益.式3中的第一项是高频分量,第二项是两信号的相位差.用一个低通滤波器涉除高频成分,就可以得到相位差.鉴相器的结构如图Fig2.

是鉴相器的增益.式3中的第一项是高频分量,第二项是两信号的相位差.用一个低通滤波器涉除高频成分,就可以得到相位差.鉴相器的结构如图Fig2.

输入1为调频信号fmin,输入2是NCO的输出,都是8位补码。使用一个单位延时来同步。乘法器的输出是16位, 把低8位截断。

使用Booth算法计算有符号数乘法,详细写博客booth乘法。

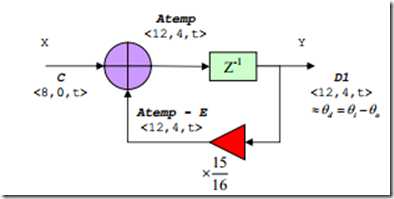

2.2环路滤波器

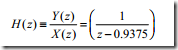

环路滤波器用来去掉鉴相器输出中的高频成分。下图是接收机中使用的一阶环路滤波器的结构图,进行符号扩展从<8,0,t>变为<12,4,t>,再乘以常数15/16;

Atemp * 15/16= Atemp- Atemp/16=Atemp – E , E=Atemp/16

Atemp * 15/16= Atemp- Atemp/16=Atemp – E , E=Atemp/16

只有一个极点Z=0.9375.由离散时间系统稳定性质知极点在单位圆内系统是稳定的。

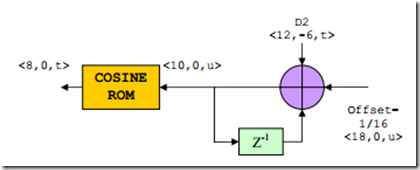

2.3NCO

结构如图

图中是基于查找表的实现方式,另一种使用CORDIC算法的实现方式见博客 cordic原理与FPGA实现(3)

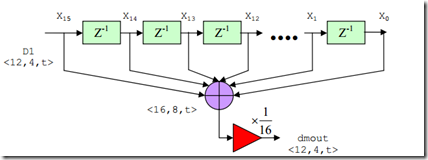

2.4FIR滤波器

具体实现见博客 FIR滤波器FPGA实现。

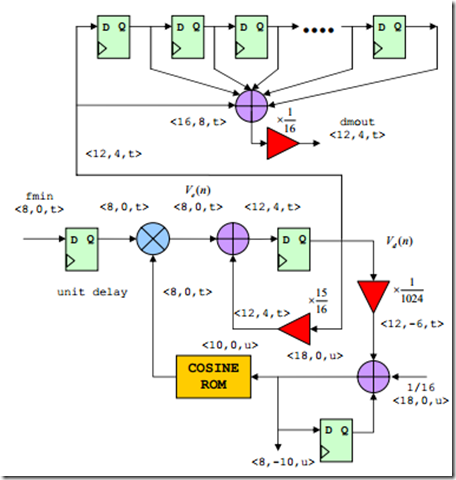

数字锁相环由三部分组成:鉴相器、环路滤波器和NCO。这个全数字FM接收机的完整结构如下图。

当无信号输入时NCO控制电压为0,NCO振荡在一个设置好的点频f0 .有信号输入时鉴相器比较输入信号的相位、频率和NCO输出信号的 差,产生一个和这个差有关系的电压Vd,这个电压经滤波后再衰减为1/1024来控制NCO。控制电压Vdd使得NCO的输出频率按与输入信号差变小的方向调整,这种负反馈的方式来完成频率的锁定。锁定后NCO的输出只和输入信号有一具相位差。这个相位差使得NCO输出频率保持在与输入锁定。也可以这样描述。鉴相器实际上是一个乘法器,输出NCO输出与输入信号的乘积即频率和和差,相锁定时差频为0,即一项为直流而一项为高频,经滤波器后只剩下直流成分来驱动NCO了。

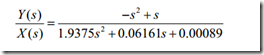

锁相环实现的最重要部分是设计反馈部分。分析这个数字PLL可以从传统反馈控制系统的瞬态响应和稳态响应入手,当有输入时,输出不能立即响应,在到达稳态时有一个瞬态响应。数字锁相环的Z变换和S变换如下:

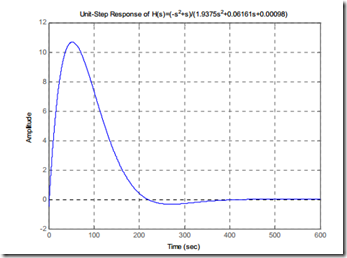

这个PLL是一个二阶系统,用一个单位阶跃测试稳定性,使用MATLAB仿真结果如下:

5916

5916

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?