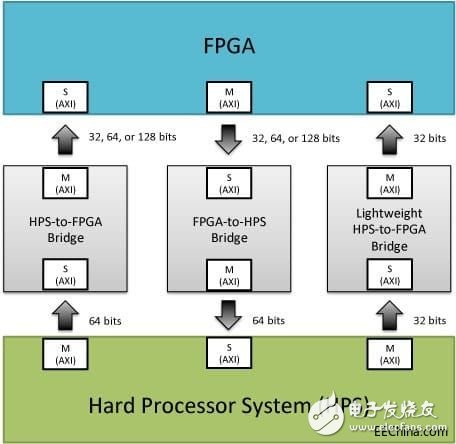

本周我想进一步探究可编程逻辑(FPGA)与硬核处理器(HPS)之间互联的结构。我发现了三种主要方式,它们是如何映射并处理通信的,哪些组件需要管控时序并且有访问权限。

AXI Bridge

为了能够实现HPS与FPGA之间的通信接口,衍生出了AXI bridge协议。AXI bridge协议能够处理带宽适应和时钟控制,支持HPS与FPGA之间双向的逻辑和数据交互。

HPS到FPGA

HPS到FPGA有两种类型:高吞吐量和低吞吐量。高吞吐量的数据带宽可以使32位、64位或128位,它是专门为高带宽数据传输而设计的,HPS作为主,处在L3层。

轻量级(或低吞吐量)通道被限制为32位,然而它进行了优化,延迟最低。它的主要功能是将控制和状态

本文探讨了可编程逻辑(FPGA)与硬核处理器(HPS)之间的连接结构,重点介绍了AXI Bridge协议、HPS到FPGA及FPGA到HPS的通信通道,并阐述了如何整合这些通信资源以提高系统性能。

本文探讨了可编程逻辑(FPGA)与硬核处理器(HPS)之间的连接结构,重点介绍了AXI Bridge协议、HPS到FPGA及FPGA到HPS的通信通道,并阐述了如何整合这些通信资源以提高系统性能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?