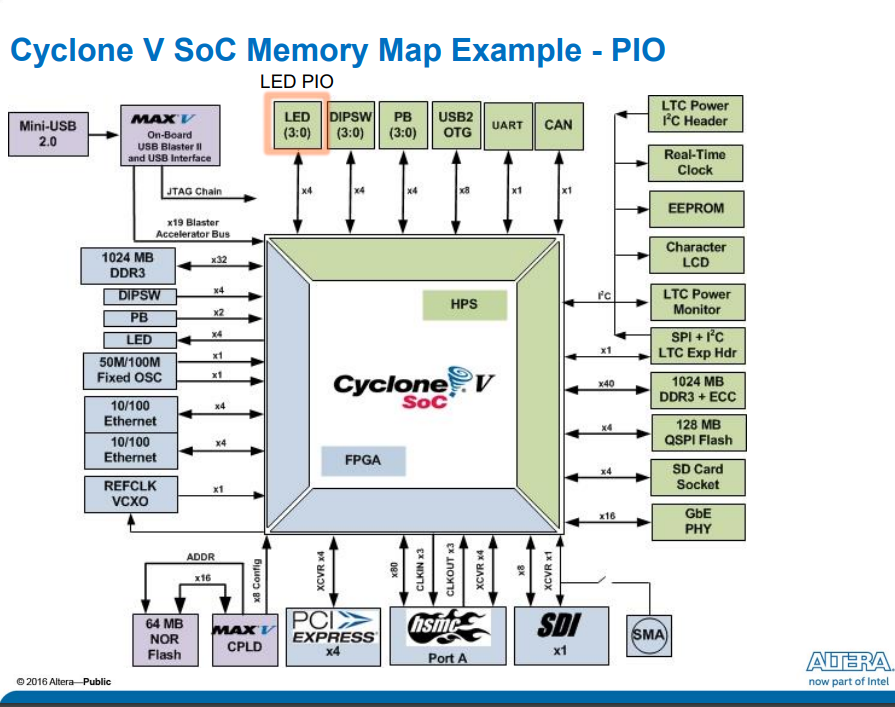

DE1-SOC开发版上的FPGA在一个基于ARM的用户定制系统(SOC)中集成了分立处理器(HPS)、FPGA和数字信号处理(DSP)功能。HPS是基于ARM cortex-A9双核处理器,具有丰富的外设和存储接口(DDR2/3)等。 HPS 和 FPGA 不仅能够独立工作,也能通过高性 能 AXI 总线桥接实现高速宽带行数据通信,这个总线是双向的,HPS 总线主机能够通过 HPS 至 FPGA 桥接访问 FPGA 架构中的总线及其外设。所有桥接兼容 AXI-3/4, 支持同时读写操作,同样的,FPGA 架构中的总线主机能够通过 FPGA 至 HPS 桥接访问 HPS 总线及其外设。基本架构如下:

1、本文学习目的

- 建立一个 SoC based FPGA hardware 系统

- HPS 组件在 Qsys 内的设定(based on DE1-SoC board)

- FPGA avmm 外设和 HPS 桥接

- 生成 Preloader 和 Device Tree(based on DE1-SoC board)

- 编译 linux 应用程序 Linux 下控制 HPS 的外设

- HPS 总线到 FPGA 总线的 Address Mapping

- HPS 控制 FPGA 端的 LED(based on DE1-SoC board)

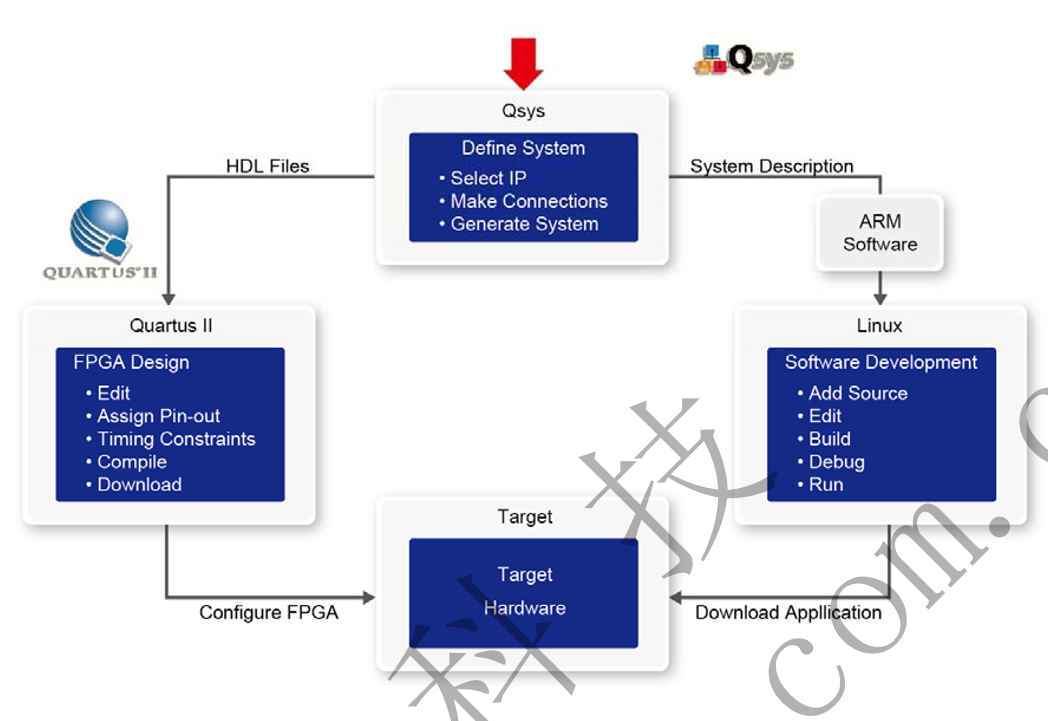

2、基本设计流程

SoC FPGA 设计流程 基于 SoC 的 FPGA 嵌入式系统硬件与软件的开发流程如图所示。

首先要基于 Qsys 规划系统需要的外设,包括 HPS 与 FPGA 各自的接口。HPS 外设只需要根据 DE1-SoC 硬 件属性进行设定即可,FPGA 外设依旧是通过 IP 模块的方式添加。然后建立各个模块间 的连接(时钟,复位,总线),最后产生出硬件与软件开发各自所需的档案

- 硬件开发和以往传统的基于 NiosII 的 FPGA 设计流程相同,使用 Quartus 加入 Qsys 以 及用户逻辑,然后设定 FPGA 管脚分配,最后综合编译产生 .sof 编程档案。

- 软件的开发则通过 Altera 的 SoCEDS 开发工具将 Qsys 所做的 HPS 硬件设定转换成产生 Preloader、uboot 和 Device Tree 所需的输入文件。这些文件可以协助 HPS 在 DE1-SoC 上运行 embedded linux system,linux 内核解析需要挂载硬件外设并完成 boot。然后 开发基于 linux 操作系统的应用程序并在 DE1-SoC 上运行。应用程序可以实现 HPS 和 FPGA 协同工作完成定制化设计。

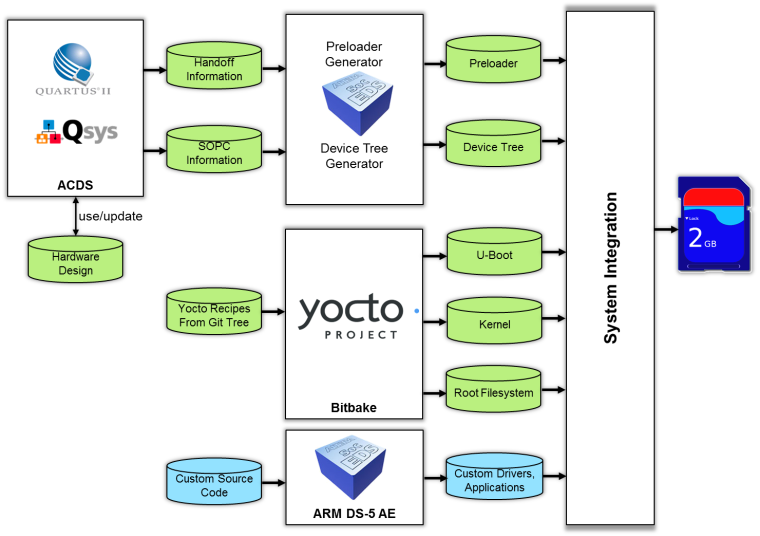

3、boot sd card制作流程

一般从系统设计开始到生成boot linux操作系统SD Card,其所需要的软件工具与生成档案如下:

下图说明了GSRD的完整构建流程。

下表显示了构建流程中使用的工具:

| 工具 | 描述 | 部分 |

|---|---|---|

| Quartus II | 创建,编辑和编译FPGA硬件设计 | ACDS |

| 设备树生成器 | 生成设备树 | SoC EDS |

| 设备树编译器 | 在设备树文件格式之间转换 | |

| 预加载器生成器 | 根据硬件切换信息生成Preloader源代码 | |

| ARM DS-5 AE | 软件开发套件 | |

| BitBake的 | Yocto建立实用程序 | Yocto源包 |

| SD卡脚本 | 创建SD卡图像的脚本 |

下表显示了构建过程中的输入文件:

| 文件 | 描述 |

|---|---|

| Quartus项目 | FPGA硬件项目源代码 |

| Board XML文件 | 描述开发板的文件,用于创建设备树 |

| Yocto食谱 | 用于构建Linux可交付成果的Yocto配方 |

| Web服务器文件 | 在板上运行的Web服务器所需的其他文件 |

下表描述了构建流程图中的其余项目:

| 文件 | 描述 |

|---|---|

| .sof | SRAM目标文件 - FPGA编程文件,由编译FPGA硬件项目产生 |

| .rbf | 原始二进制文件 - 压缩FPGA编程文件 |

| .dts | 设备树源 - 用于描述Linux内核的硬件 |

| .dtb | 设备树二进制 - .dts的二进制表示 |

| .sopcinfo |

本文介绍了基于DE1-SOC开发板的HPS系统设计,包括Qsys工程创建、HPS配置、外设添加与配置、SD卡制作流程和FPGA验证。详细讲解了如何搭建Qsys系统,配置HPS组件,如ARM Cortex-A9双核处理器,并通过Qsys生成硬件描述语言文件,最后验证FPGA部分组件的功能。

本文介绍了基于DE1-SOC开发板的HPS系统设计,包括Qsys工程创建、HPS配置、外设添加与配置、SD卡制作流程和FPGA验证。详细讲解了如何搭建Qsys系统,配置HPS组件,如ARM Cortex-A9双核处理器,并通过Qsys生成硬件描述语言文件,最后验证FPGA部分组件的功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?