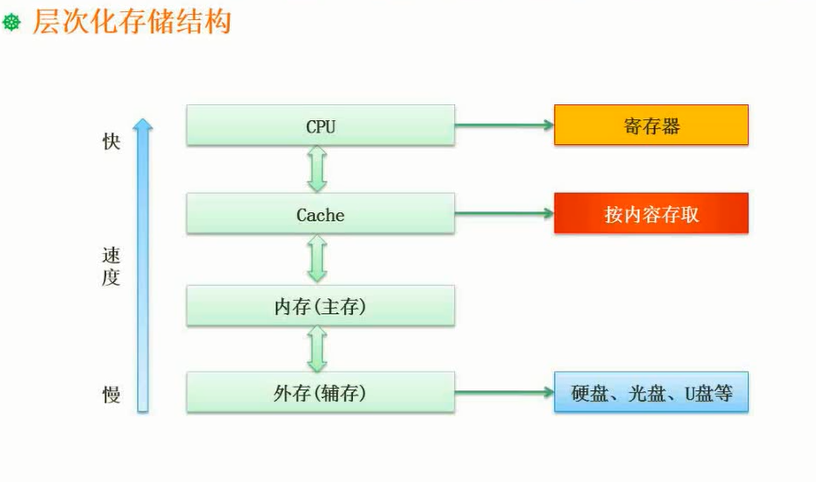

层次化存储结构

cpu --> Cache --> 内存(主存) --> 外存(辅助) ;处理速度由快至慢,制造成本由贵至便宜。

Cache-概念

1、Cache的功能,提高CPU数据输入输出的速率,突破 冯诺依曼瓶颈,即CPU与存储系统间数据传送宽带限制;

2、在计算机系统的存储系统体系中,Cache是访问速度最快的层次;

3、使用Cache改善系统性能的依据是程序的局部性原理;

t1表示Cache的周期时间,t2表示主存储器周期时间(t2远远大于t1),h代表对Cache的访问命中率

使用“Cache+主存储器”的系统的平均周期 t3,则

t3 =h*t1+(1-h)*t2

总结:h的取值范围为0.00-1.00,t3的范围为: 2t2 ~ t1 ,命中率越高,t3时间越短,Cache的价值就能越能体现出来,当h为0时,Cache将毫无价值

局部性原理

在CPU访问寄存器时,无论是存取数据抑或存取指令,都趋于聚集在一片连续的区域中,这就被称为局部性原理

时间局部性(temporal locality)

时间局部性指的是:被引用过一次的存储器位置在未来会被多次引用(通常在循环中)。

空间局部性(spatial locality)

如果一个存储器的位置被引用,那么将来他附近的位置也会被引用

栗子1

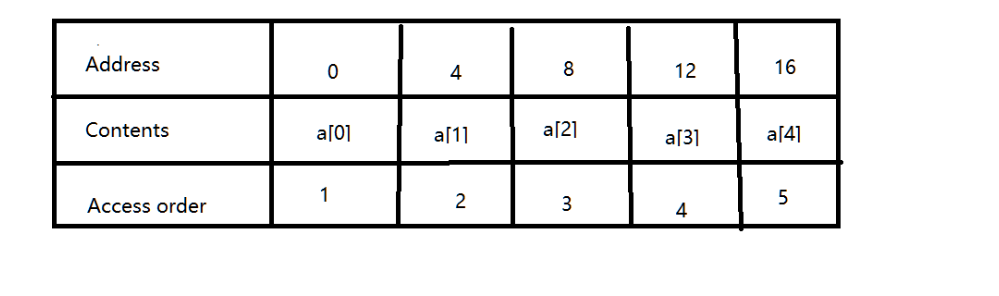

int a[N] = {0, 1, 2, 3, 4};

int sum = 0;

for (int i = 0; i < 5; ++i)

{

sum = sum + a[i];

}在这个例子中,变量在内存中的存储结构如下:

可以看出从a[0]到a[4]的地址位是连续的,而且程序中访问这些变量频率较高,所以对与a来说,其具有良好的空间局部性,但是每个a成员只被访问一次,所以并不具有良好的时间局部性。

但是对于变量sum来说,其由于其是一个标量,也就是说通过其地址只能得到一个值,故其不具有良好的空间局部性,但是由于其访问频率较高,所以有良好的时间局部性。

通过以上结论可以推出,对于向量a来说,如果其访问顺序和存储顺序一致,那么a的变量之间距离太远,那么其空间局部性越差,因为CPU没办法在其附近找到其他变量,

所以空间局部性和a的步长有很大的关系,步长越长,空间局部性越差。 同理,如果一个变量被访问的频率越高,其时间局部性就越好。

取指令的局部性

指令存子啊存储器中,CPU要读取指令必须取出该指令,所以就可以评价取指令的局部性。

在for循环中,循环体内的指令多次被执行,所以有良好的时间局部性,

循环体中的指令是按顺序执行的,有良好的空间局部性(指令在存储器中是顺序存放的)。

小结 :评价局部性的简单原则

1.重复引用同一个变量具有良好的时间局部性。

2.对于步长位k的引用程序,步长越小,空间局部性越小。步长为1的引用具有良好的空间局部性。k越大,空间局部性越差。

3.对于取指令来说、循环有良好的时间和空间局部性。

主存-分类

计算机存储器分为两类,随机存储器(RAM)和只读存储器(ROM)

主存-编址

内存是按字节编址的,所以单位是字节,1字节等于8位。

所以就记住两个就够了。记住几个常用的2的10次方为1024即1KB2的20次方=(2的10次方)的平方,即1MB就行了。

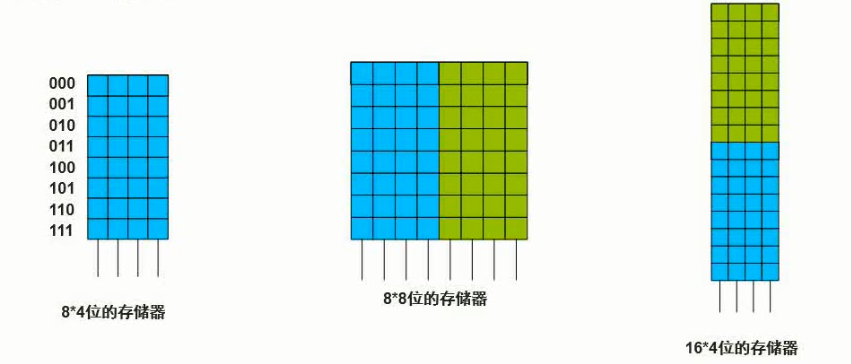

存储器模型图如下图所示,

每1横排表示一个地址单元,每个地址单元有 1* N(N表示n位存储器)个字节

栗子2

内存地址从AC000H到C7FFFH,共有___K个地址单元,如果该内存地址按(16bit)编址,由28片存储器芯片构成,已知构成此内存的芯片每片有16K个存储单元,则该芯片每个存储单元存储___位。

解析:C7FFFH-AC000H+1 = 1C000H --> 1C000H/2^10 = 112 ;共有112K个地址单元。28*16K* N = 112K * 16 --> 求解得N = 4 ;

参考博客 https://blog.csdn.net/u013315650/article/details/56347793

1709

1709

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?