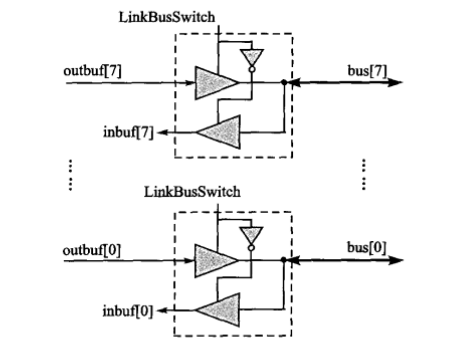

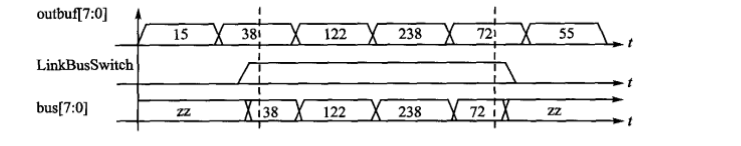

1、如图这是电路逻辑结构图及其时序逻辑图:

2、verilog程序:

`define ON 1'b1

`define OFF 1'b0

wire LinkBusSwitch;

wire[7:0] outbuf;

wire[7:0] inbuf;

inout[7:0] bus;

assign bus=(LinkBusSwitch==`ON) ? outbuf : 8'bzz;

always@(posedge clk)

begin

//此处略去些许代码。。。。

if(!LinkBusSwitch)

inbuf <= bus;

end

//此处略去些许代码。。。。

endmodule

3、高阻是什么?

在这里当LinkBusSwitch是0 时,我们的outbuf 是高阻,也就是和bus断开了,高阻嘛?就是阻值很高,别的电流就过不来了。

当outbuf是高阻值得时候,其就与bus断开了,那么我们的bus就可以被其他器件线路利用了。

****************************************************************************

made by qidaiYMM, your comment is appreciated.

email:151988261@qq.com

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?