笔记根据北京大学陆俊林老师的计算机组成(http://www.chinesemooc.org/mooc/4392)。

一、冯诺依曼结构

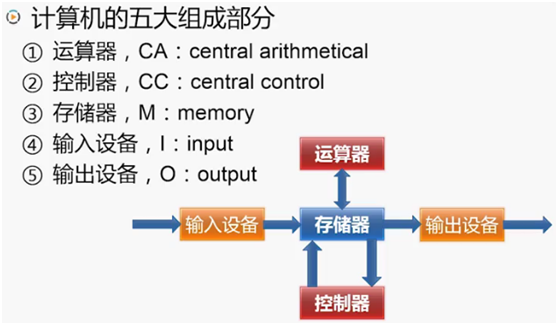

计算机的五大组成部分

冯诺依曼结构的特征是:特别要记住第二点

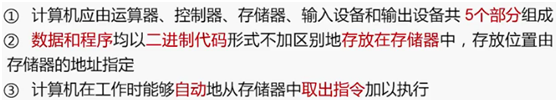

二、指令的执行

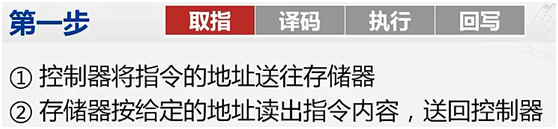

这里请先记住指令的执行步骤包括下面四步,后面有例子。

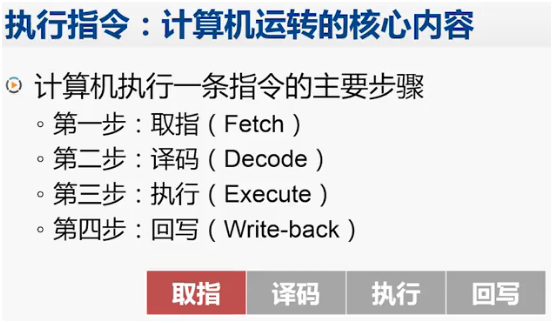

三、模型机

1、模型机的组成

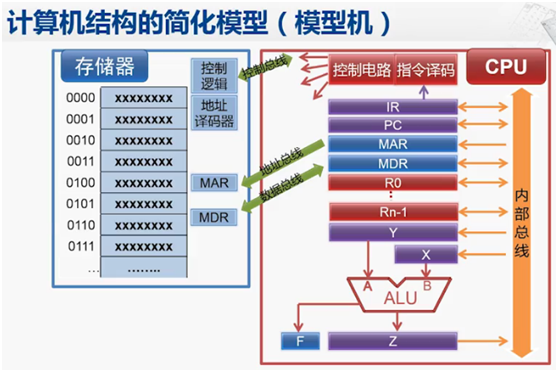

模型机可以看做一个简单的计算机,包括下面几个部分:存储器、CPU(控制器、运算器)、输入输出(这个后面有介绍)

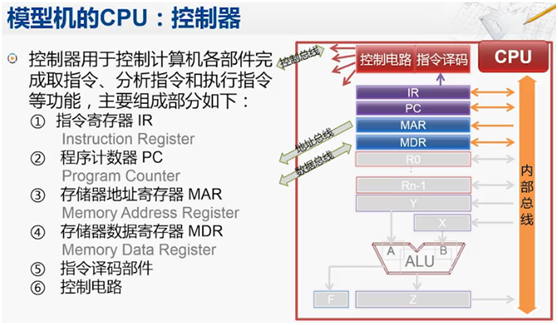

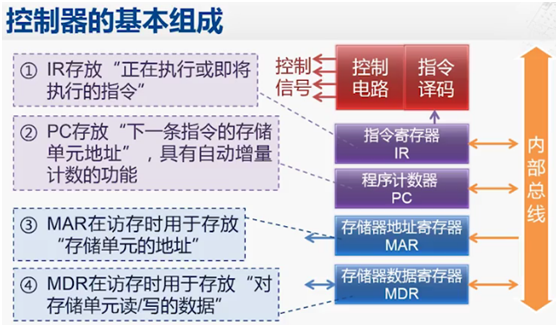

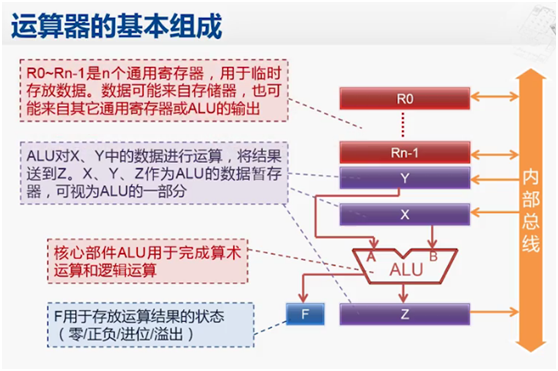

CPU包括了控制器和运算器

2、计算机结构的简化模型(模型机)

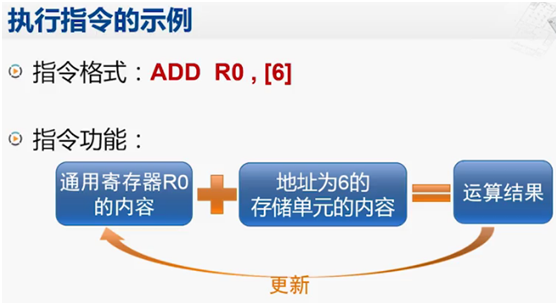

四、执行指令的示例

1、要执行的指令

2、第一步是取指

3、例子

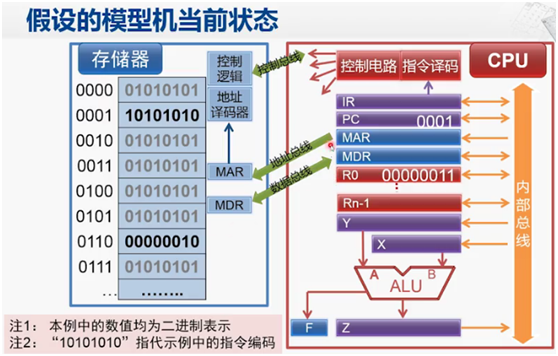

下面是起始状态

首先明确任务,任务是把R0中的数据和0110(也就是地址为6的储存单元)中的数据进行相加,并把结果更新到R0中。

然后0001单元中的数据10101010指代指令(也就是假设10101010数据是一条指令)。

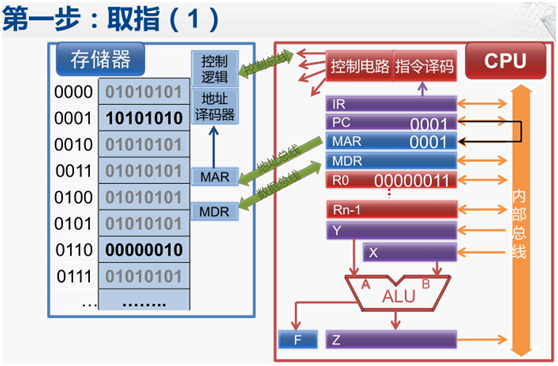

4、取值过程

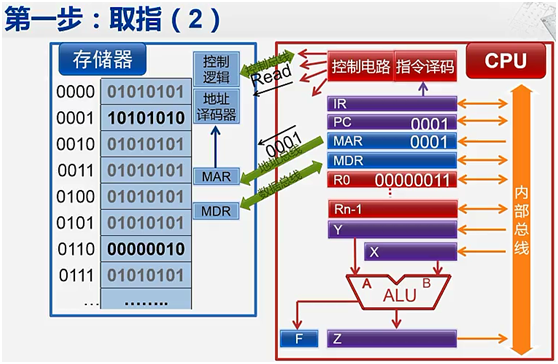

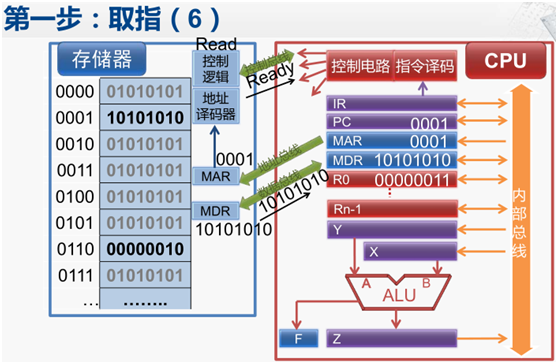

控制器发出控制信号将PC寄存器中的内容数据通过内部总线传送到MAR中

MAR把地址送到地址总线上,同时控制电路在控制总线上发出相应的控制信号,代表这次访问存储器的操作是读数据。

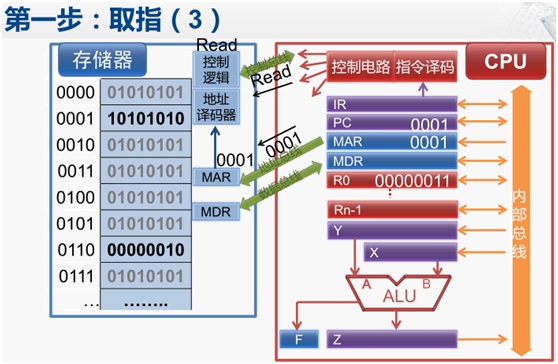

存储器的MAR保存了要访问的地址,同时存储器的控制逻辑收到控制总线的控制信号知道了这次操作是一次读取操作。

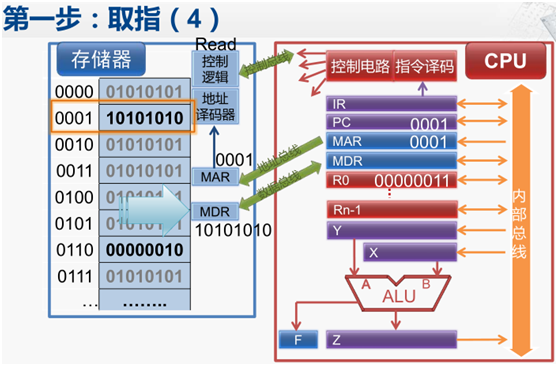

存储器通过地址译码器找到0001存储单元的内容,并送到MDR寄存器中。

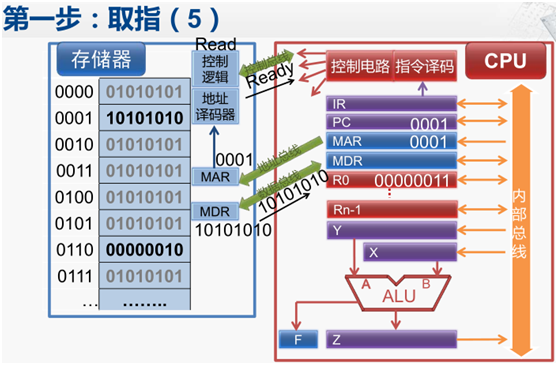

接着存储器的控制逻辑通过控制总线反馈CPU,当前传输准备好,同时MDR的内容也会送到数据总线上。

CPU接收到控制总线返回的Ready信号,知道数据总线已经准备好数据,于是,CPU的MDR寄存器就将数据总线上的数据保存下来。

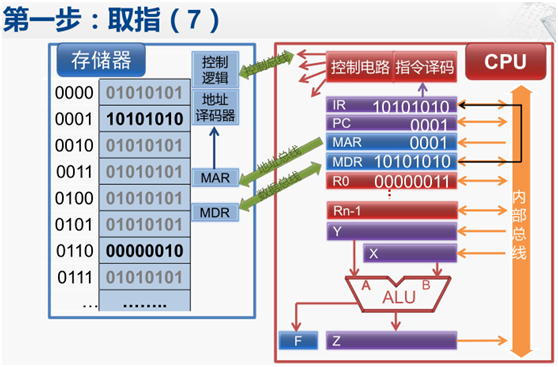

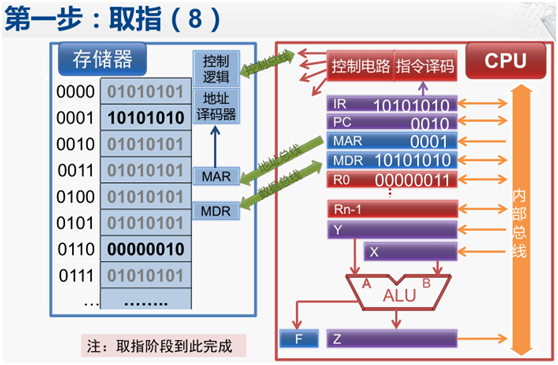

MDR将指令送到IR指令寄存器中。

更新PC寄存器中内容,更新为下一条指令要访问的地址。到这里取指阶段就完成了。

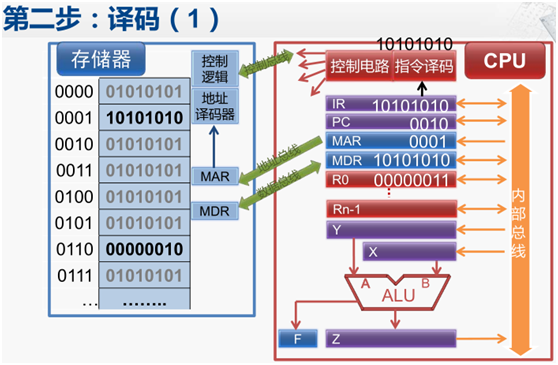

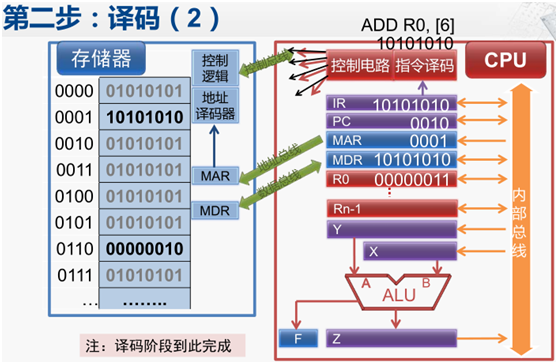

5、译码过程

IR指令寄存器中的指令会发送到指令译码部件。

指令译码部件会分析出这是加操作。

控制电路会向相关部件发送控制信号。

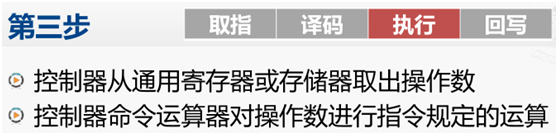

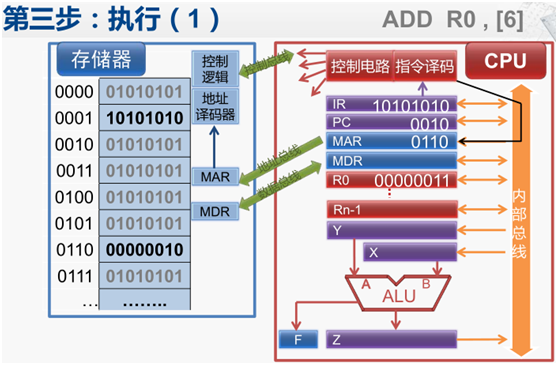

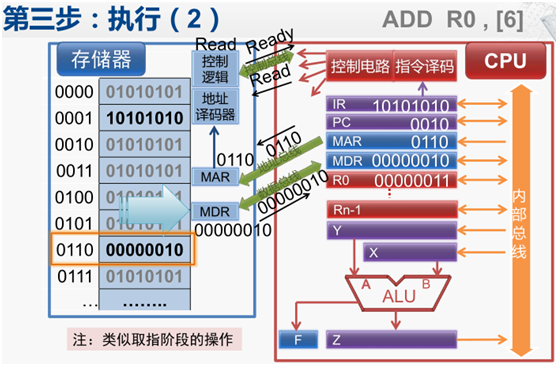

6、执行过程

指令译码部件看到指令是R0加储存单元6的数据,于是去读取储存单元6的数据。

过程就像之前的取指一样。

MAR将地址发送到地址总线上。同时控制电路在控制总线上发出信号这次是读取操作。

存储器的MAR保存地址总线上的地址,控制逻辑获得控制总线的信号,知道是读操作。

存储器的MAR控制逻辑接收到信号后,找到0110存储单元的数据送到MDR。

控制逻辑通过控制总线反馈数据准备好,同时MDR把数据送到数据总线。

CPU接收数据保存到MDR中。

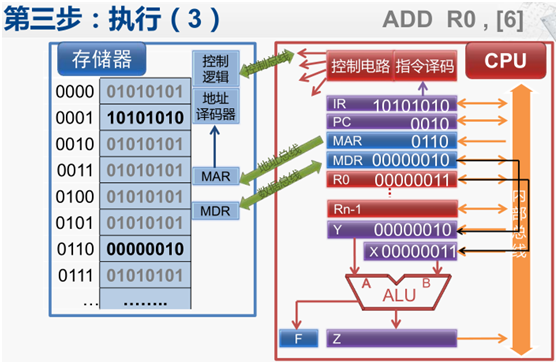

控制器将MDR中数据送到Y寄存器中,R0中数据送到X寄存器中。

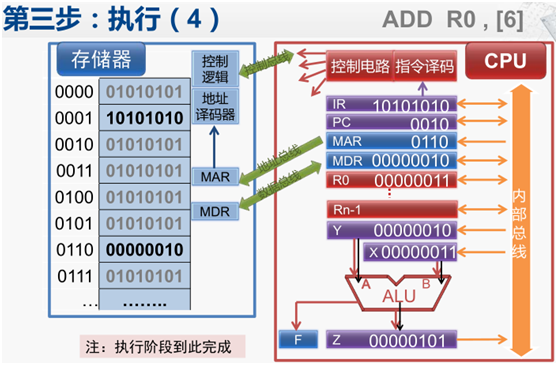

在控制电路的控制下ALU就会把Y和X中的数据进行计算,并把计算结果放到Z寄存器中。

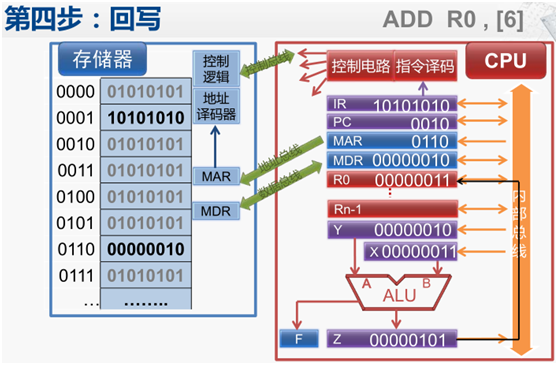

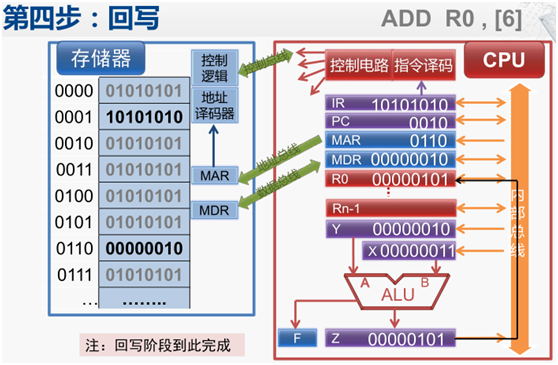

7、回写过程

这是计算结果是放在Z寄存器中。控制电路会发出相应的信号,将Z中的数据传送到R0。

这时Z寄存器数据是00000101,R0数据是00000011

当Z寄存器中的数据00000101送到R0覆盖原来的数据00000011。回写阶段就完成了。

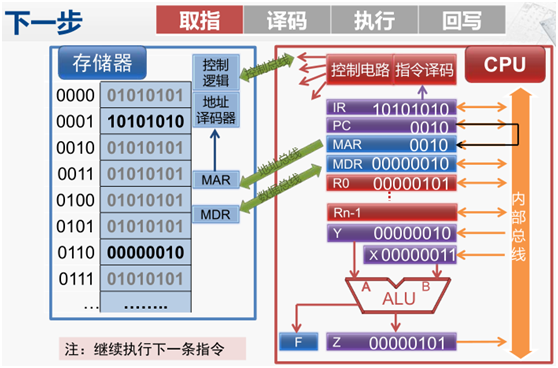

继续执行下一条指令。

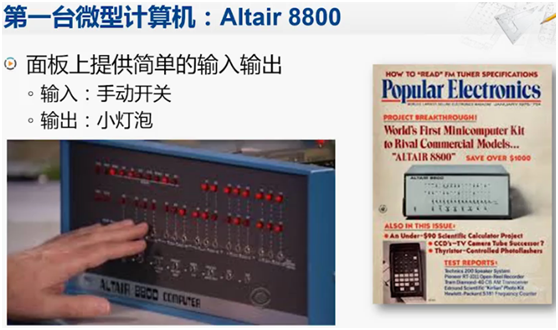

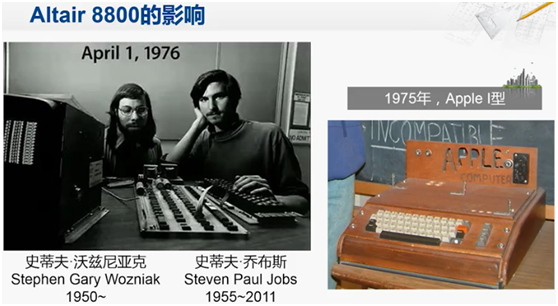

五、第一台微型计算机

第一台微型计算机影响下,产生了Apple I型,有键盘输入,可连接电视机进行输出。

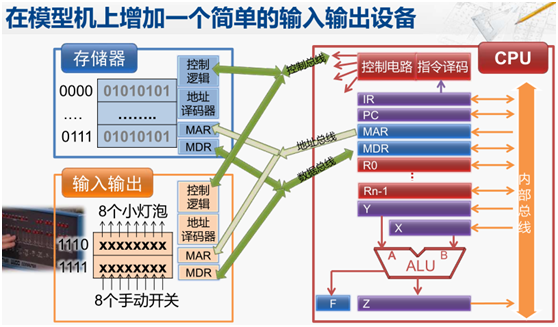

六、在模型机上增加输入输出

输入输出设备通过控制总线、地址总线、数据总线和模型机连接。

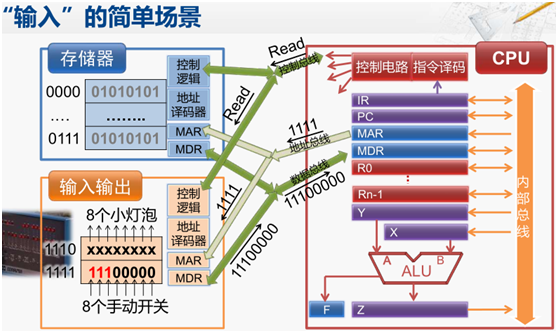

1、输入场景

因为输入输出上面的地址与存储器上的地址不重复,而且地址总线上有简单的电路可以识别出地址所在的存储单元是在储存器还是输入输出。所以可以根据地址找到对应的存储单元。

CPU的MAR向地址总线上发出1111地址,同时控制电路发出读信号。

输入输出的MDR将1111存储单元的数据发送到数据总线,同时向控制总线反馈数据准备好。

CPU的MDR将数据总线的数据保存,以便之后的操作。

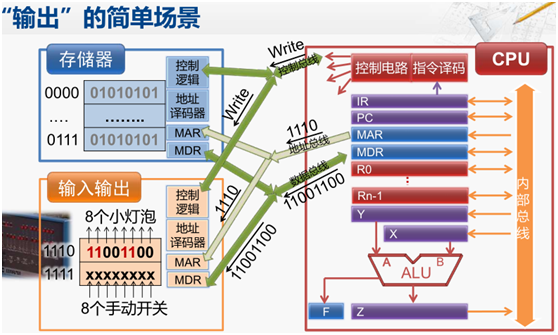

2、输出场景

MAR向地址总线发出地址1110,同时控制电路向控制总线发出写操作。

输入输出的MAR接收到地址总线的地址,同时控制逻辑接收到控制总线的写操作。

输入输出的MDR获取数据总线的数据,并向1110地址写入该数据。

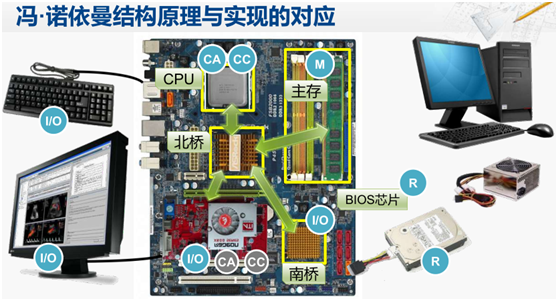

七、冯诺依曼结构原理与实现的对应

CPU:包括控制单元和运算单元

CPU通过北桥访问主存

南桥与硬盘连接

BIOS芯片,只读存储器,断电信息不会丢失,与南桥连接。

电脑启动时CPU从BIOS读取指令,检查电脑上各个硬件设备。

显卡上的GPU也有控制器和运算器

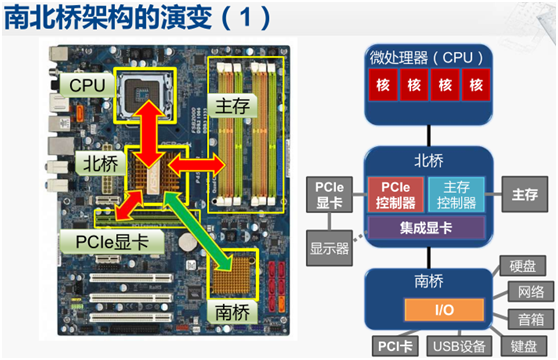

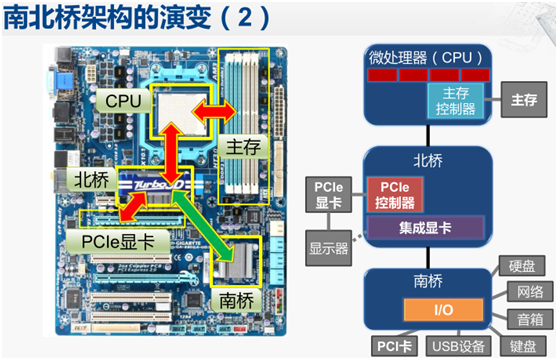

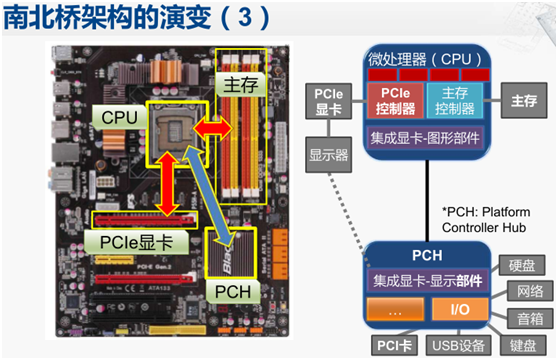

八、南北桥架构演变

红色箭头是访问压力大的通道,是首要解决的问题。

北桥的控制器移到了CPU中,现在CPU不需要通过北桥,可以直接访问主存。

北桥的控制显卡控制器PCIE集成到CPU中,北桥剩下的控制单元与南桥整合,三片式的机构变为两片式,这时南北桥架构已经不存在了。

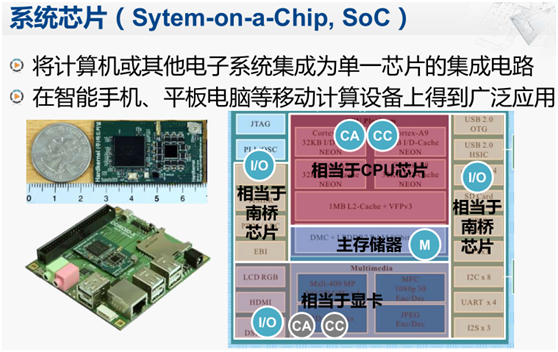

一个系统芯片集成了冯诺依曼所有结构。

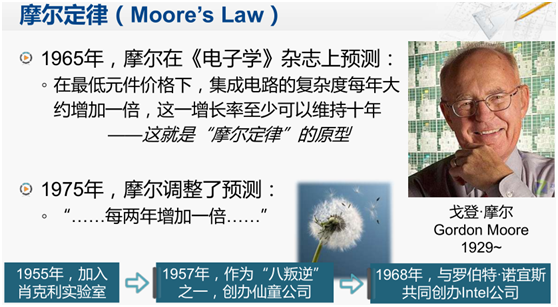

九、摩尔定律

2805

2805

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?