简介:《微机原理与接口技术》是深入理解计算机硬件架构与软硬件交互的核心课程,涵盖计算机基本结构、指令系统、存储体系、I/O接口技术等内容。本试题库由重庆科技学院教师精心编写,包含选择题、填空题、判断题、简答题和综合题等多种题型,全面覆盖CPU结构、数制转换、总线技术、中断机制及常见接口(如USB、PCI、SATA)等知识点。经过实际教学验证,该资源不仅有助于学生巩固理论知识、提升实践分析能力,也可作为教师教学辅助工具,适用于课程复习、考试备考及硬件开发人员的技能提升。

1. 微机原理基础概念详解

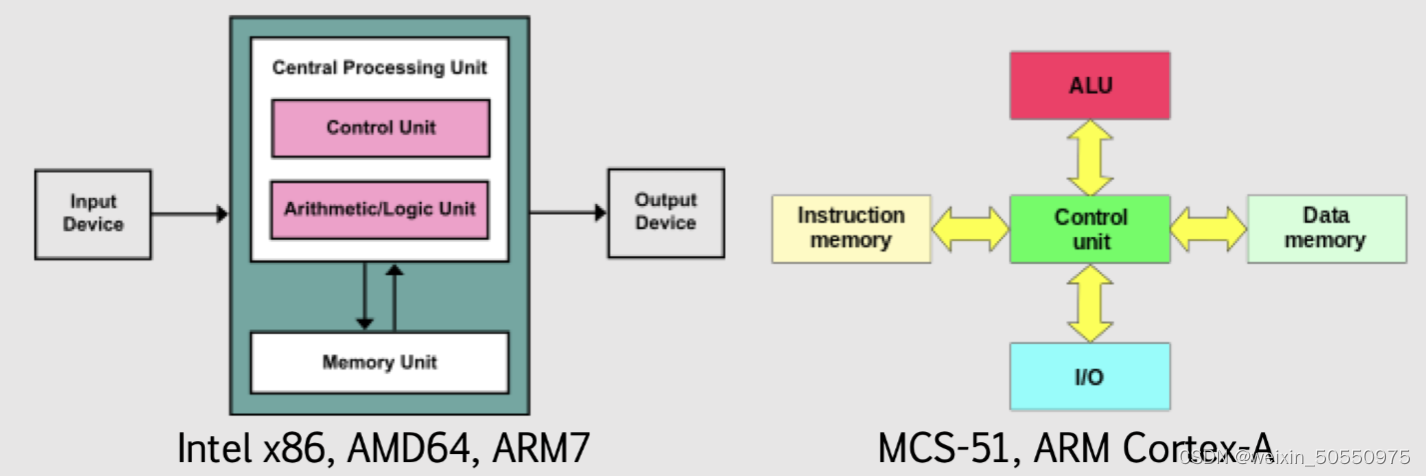

计算机系统由硬件与软件协同构成,微机原理是理解硬件运行机制的核心。本章系统讲解微型计算机的基本组成:中央处理器(CPU)、存储器、输入/输出设备及总线结构,阐明各模块的功能与协作关系。重点解析冯·诺依曼体系“程序存储”思想与哈佛架构“数据与程序分离”的本质区别,并结合现代嵌入式系统说明其应用场景。通过对比8086处理器的16位架构与当代多核CPU的技术演进,展现字长、时钟频率、指令周期等关键参数对性能的影响路径,为后续深入学习奠定理论基础。

2. CPU结构与工作原理(寄存器、运算器、控制器)

中央处理器(Central Processing Unit, CPU)是微型计算机系统的核心,负责执行程序指令、处理数据以及协调各硬件组件的运行。它不仅是计算能力的体现,更是整个系统控制流和数据流的中枢。现代CPU虽然高度集成、架构复杂,但其基本构成仍可追溯至早期微处理器的设计理念——由 寄存器组 、 运算器(ALU) 和 控制器 三大功能模块组成。这些部件通过内部总线相互连接,在时钟信号驱动下协同完成指令的取指、译码与执行全过程。

理解CPU的工作机制,必须从其内部架构入手,深入剖析各个子系统的功能分工与协作逻辑。本章将围绕CPU的三大核心组成部分展开系统性讲解,重点解析寄存器的功能分类、ALU的运算实现机制、控制单元如何生成精确的控制信号,并结合Intel 8086这一经典微处理器实例,揭示CPU在最小/最大模式下的引脚配置差异及其对系统扩展的影响。此外,还将引入数据通路设计原则,探讨总线宽度、机器周期等关键参数如何影响整体性能表现。

2.1 CPU内部架构解析

CPU的内部架构决定了其处理效率、指令兼容性和系统扩展能力。一个典型的CPU内部包含多个功能单元,其中最核心的是 寄存器组 、 算术逻辑单元(ALU) 和 控制逻辑电路 。这些单元通过高速内部总线相连,形成一条高效的数据流动路径。CPU在每一个时钟周期内都可能执行不同的微操作,如加载数据、执行加法、跳转地址等,所有这些动作均由控制器根据当前指令进行调度。

为了更清晰地展示CPU内部的信息流动与控制关系,以下使用Mermaid流程图描绘典型CPU内部结构:

graph TD

A[程序计数器 PC] -->|地址| B(地址总线)

B --> C[内存]

C -->|指令| D(数据总线)

D --> E[指令寄存器 IR]

E --> F[指令译码器]

F --> G[控制信号发生器]

G --> H[ALU 控制线]

G --> I[寄存器选择]

J[通用寄存器] -->|操作数| K(ALU)

L[状态寄存器] -->|标志位| K

K --> M[结果写回寄存器或内存]

M --> J

该流程图展示了从取指到执行的基本信息流向:程序计数器提供下一条指令地址,经地址总线访问内存获取指令,送入指令寄存器后由译码器解析并生成控制信号,最终驱动ALU完成运算任务。整个过程体现了“冯·诺依曼”体系中“存储程序”的思想。

2.1.1 寄存器组的功能分类与作用

寄存器是CPU内部用于暂存数据、地址和状态信息的高速存储单元,其访问速度远高于主存。它们按功能可分为三类: 通用寄存器 、 专用寄存器 和 状态寄存器 。

通用寄存器、状态寄存器、段寄存器的用途分析

通用寄存器 主要用于存放临时数据或中间结果,供算术逻辑运算使用。以Intel 8086为例,其拥有8个16位通用寄存器:

- AX(累加器)、BX(基址寄存器)、CX(计数寄存器)、DX(数据寄存器)

- SI(源变址寄存器)、DI(目的变址寄存器)、BP(基指针)、SP(堆栈指针)

这些寄存器既可作为整体16位使用,也可拆分为高低字节独立访问(如AH/AL)。例如,AX常用于I/O操作和乘除法运算,而CX则多用于循环控制中的计数。

| 寄存器 | 典型用途 | 可分割 |

|---|---|---|

| AX | 算术运算、I/O数据传输 | 是(AH/AL) |

| BX | 内存寻址中的基地址 | 是(BH/BL) |

| CX | 字符串操作、循环次数 | 是(CH/CL) |

| DX | 端口地址、乘除法高位 | 是(DH/DL) |

| SI/DI | 字符串源/目标地址 | 否 |

| BP | 堆栈帧基址指针 | 否 |

| SP | 堆栈顶部指针 | 否 |

状态寄存器(FLAGS) 又称程序状态字(PSW),记录CPU执行指令后的状态信息。8086的状态寄存器为16位,其中仅9位被定义,包括:

- CF(Carry Flag) :进位标志,无符号数溢出时置1

- ZF(Zero Flag) :结果为零时置1

- SF(Sign Flag) :结果为负(最高位为1)时置1

- OF(Overflow Flag) :有符号数溢出时置1

- PF(Parity Flag) :低8位中1的个数为偶数时置1

- AF(Auxiliary Carry Flag) :BCD运算中第3位向第4位进位时置1

这些标志位直接影响条件转移指令(如JE、JNE、JG等)的执行判断。

段寄存器 是x86架构特有的机制,用于实现分段内存管理。8086采用20位地址总线,但寄存器只有16位,因此引入“段地址 + 偏移地址”方式生成物理地址:

物理地址 = 段寄存器 × 16 + 偏移地址

四个段寄存器分别为:

- CS(Code Segment):代码段基址

- DS(Data Segment):数据段基址

- SS(Stack Segment):堆栈段基址

- ES(Extra Segment):附加数据段基址

这种设计使得8086能访问1MB地址空间(2^20),尽管每个段最大为64KB。

程序计数器(PC)与堆栈指针(SP)的工作机制

程序计数器(Program Counter, PC) 又称指令指针(IP),指向即将执行的下一条指令的偏移地址。在每条指令执行完毕后,PC会自动增量(增量大小取决于指令长度),实现顺序执行。当遇到跳转指令(如JMP、CALL)时,PC被强制修改为目标地址,从而改变执行流程。

例如,在8086中执行 JMP 0x100 指令时,IP将被设置为0x100,下一周期便从此处取指。

堆栈指针(SP) 指向当前堆栈顶部位置,堆栈位于SS段内,遵循“后进先出”原则。PUSH指令会使SP减2(16位系统),然后将数据压入堆栈;POP指令则先读取堆栈内容,再使SP加2。

下面是一段汇编代码示例,演示SP的变化过程:

MOV AX, 0xABCD ; 将立即数ABCDh载入AX

PUSH AX ; 压栈AX,SP = SP - 2

POP BX ; 弹栈至BX,SP = SP + 2

逻辑分析与参数说明:

- 第一行: MOV AX, 0xABCD 将16位立即数加载到AX寄存器。

- 第二行: PUSH AX 触发以下操作:

- SP ← SP − 2

- [SS:SP] ← AX(即将AX内容写入堆栈顶部)

- 第三行: POP BX 执行:

- BX ← [SS:SP]

- SP ← SP + 2

此机制广泛应用于函数调用、中断响应和局部变量保存场景。

2.1.2 运算器(ALU)的逻辑与算术运算能力

算术逻辑单元(Arithmetic Logic Unit, ALU) 是CPU中执行所有数学和逻辑运算的核心部件。它可以完成加法、减法、与、或、非、异或、移位等多种操作,其输出结果不仅包括运算值,还包括相应的状态标志(如CF、ZF、OF等)。

加法器、移位器、逻辑门电路在ALU中的集成实现

最基本的ALU构建模块是 全加器(Full Adder) 。一个全加器接收两个操作数位A和B,以及低位进位 Cin,输出和S与进位 Cout:

S = A \oplus B \oplus C_{in}, \quad C_{out} = (A \cdot B) + (C_{in} \cdot (A \oplus B))

多个全加器级联构成 行波进位加法器(Ripple Carry Adder) ,可实现多位加法。但由于进位逐级传递,延迟较大。现代CPU多采用 超前进位加法器(Carry Look-Ahead Adder) 来减少延迟。

除了加法器,ALU还集成了:

- 移位器(Shifter) :支持左移、右移、循环移位,用于快速乘除(×2^n 或 ÷2^n)和位字段提取。

- 逻辑门阵列 :实现AND、OR、NOT、XOR等布尔运算。

实际ALU通常采用多路选择器(MUX)来切换不同运算模式。例如,给定控制信号 Op[2:0] ,可选择执行加法、减法或逻辑运算。

以下是一个简化版8位ALU的行为级Verilog模型片段:

module ALU_8bit (

input [7:0] A, B,

input [2:0] Op,

output reg [7:0] Result,

output reg ZF, CF, OF, SF

);

always @(*) begin

case (Op)

3'b000: Result = A + B; // ADD

3'b001: Result = A - B; // SUB

3'b010: Result = A & B; // AND

3'b011: Result = A | B; // OR

3'b100: Result = ~A; // NOT

3'b101: Result = A << 1; // SHL

3'b110: Result = A >> 1; // SHR

default: Result = 8'h00;

endcase

// 标志位生成

CF = (Op == 3'b000) ? (A + B > 8'hFF) :

(Op == 3'b001) ? (A < B) : 1'b0;

ZF = (Result == 8'h00);

SF = Result[7];

OF = (Op == 3'b000) ? ((A[7]==B[7]) && (Result[7]!=A[7])) :

(Op == 3'b001) ? ((A[7]!=B[7]) && (Result[7]!=A[7])) : 1'b0;

end

endmodule

逐行解读分析:

- input [7:0] A, B :两个8位输入操作数。

- input [2:0] Op :3位操作码,决定执行何种运算。

- output reg [...] :输出结果及四个状态标志。

- always @(*) :组合逻辑块,实时响应输入变化。

- case (Op) :根据操作码选择不同运算路径。

- 加法时检测是否超出255(即产生进位),赋值给CF。

- ZF在结果为0时置1,SF取符号位,OF依据溢出规则判定。

该模型虽简化,但完整体现了ALU的核心设计理念: 多功能集成 + 标志反馈 + 控制解码 。

标志位生成与条件判断的关系

ALU产生的标志位是条件跳转指令的基础。例如:

CMP AX, BX ; 比较AX与BX(本质是AX-BX)

JG LABEL ; 若AX > BX(有符号比较),跳转

CMP 指令执行减法但不保存结果,仅更新标志位。后续 JG (Jump if Greater)依据SF、OF、ZF综合判断是否跳转:

\text{JG condition: } (ZF=0) \land (SF=OF)

这意味着:结果不为零且符号一致(未发生异常溢出),表示大于成立。

下表列出常见条件跳转与标志位关系:

| 指令 | 条件 | 对应标志位组合 |

|---|---|---|

| JE/JZ | 相等/为零 | ZF=1 |

| JNE/JNZ | 不相等/非零 | ZF=0 |

| JA/JNBE | 无符号大于 | CF=0 ∧ ZF=0 |

| JB/JNAE | 无符号小于 | CF=1 |

| JG/JNLE | 有符号大于 | ZF=0 ∧ (SF=OF) |

| JL/JNGE | 有符号小于 | SF≠OF |

由此可见,ALU不仅是“计算器”,更是“决策支持引擎”,其输出直接影响程序的控制流走向。

2.2 控制单元与时序协调机制

控制单元(Control Unit, CU)是CPU的“指挥中心”,负责从内存中取出指令、解析其含义,并生成一系列精确的控制信号来协调寄存器、ALU、总线等部件的动作。它的性能直接决定了CPU能否正确、高效地执行程序。

CU的工作依赖于严格的 时序控制系统 ,确保每一个微操作都在正确的时钟节拍下发生。无论是简单的MOV指令还是复杂的乘法运算,都需要经过若干机器周期才能完成。

2.2.1 指令译码器与控制信号生成过程

指令进入CPU后,首先被送入 指令寄存器(IR) ,随后由 指令译码器(Instruction Decoder) 解析操作码字段,确定所需的操作类型和操作数来源。

以8086为例,其采用 微程序控制(Microprogrammed Control) 与 硬布线控制(Hardwired Control) 相结合的方式。

微程序控制与硬布线控制方式对比

| 特性 | 微程序控制 | 硬布线控制 |

|---|---|---|

| 实现方式 | 控制信号由控制存储器(CS)中的微指令序列产生 | 由组合逻辑电路直接生成 |

| 灵活性 | 高,易于修改或扩展指令集 | 低,更改需重新设计电路 |

| 开发周期 | 较长,需编写微码 | 短,适合固定指令集 |

| 执行速度 | 相对较慢(需查表) | 快,纯硬件响应 |

| 应用场景 | 复杂CISC处理器(如早期x86) | RISC处理器(如ARM、MIPS) |

微程序控制的基本思想是将每条机器指令分解为一系列 微命令(micro-operations) ,存储在ROM中。执行时,CU按序读取这些微指令,依次发出控制信号。

例如,执行 ADD [BX], AX 指令的过程可分解为以下微操作序列:

- T1 :PC → MAR,发出地址锁存信号

- T2 :MEM_READ,指令送入MDR → IR

- T3 :IR译码,启动地址计算(BX内容+偏移)

- T4 :BX内容→ALU,执行地址加法

- T5 :结果→MAR,准备读内存

- T6 :MEM_READ,操作数→MDR

- T7 :MDR→Y寄存器,AX→ALU输入

- T8 :ALU执行加法,结果→Z寄存器

- T9 :Z→MDR,MAR保持,MEM_WRITE

- T10 :结果写回内存,PC自增

上述过程可通过如下Mermaid时序图表示:

sequenceDiagram

participant CU

participant IR

participant ALU

participant MEM

participant REG

CU->>IR: T1-T2: 取指

IR->>CU: 提供操作码

CU->>REG: T3: 读BX

REG->>ALU: T4: 地址计算

ALU->>CU: 地址结果

CU->>MEM: T5-T6: 读内存

MEM->>MDR: 数据返回

MDR->>ALU: T7: 准备运算

CU->>ALU: T8: 执行ADD

ALU->>Z: 输出结果

Z->>MDR: T9: 准备写回

CU->>MEM: T10: 写内存

该图清晰展现了控制单元如何协调各部件在时间轴上的协作。

相比之下,硬布线控制通过门电路直接实现控制逻辑。例如,当操作码为 00000011 (假设为ADD指令)时,译码器输出高电平触发ALU_ADD信号、RegWriteEnable信号等,无需中间查找步骤,响应更快。

现代高性能CPU倾向于采用 混合控制方式 :简单指令用硬布线加速,复杂指令保留微码支持,兼顾性能与灵活性。

2.2.2 机器周期、总线周期与指令执行时序配合

CPU的操作是在严格的时间框架下进行的,涉及三种基本周期概念:

- 时钟周期(Clock Cycle) :最基本的时间单位,由主频决定(如1GHz对应1ns周期)。

- 机器周期(Machine Cycle) :完成一个基本操作所需的时间,如取指、内存读/写。

- 总线周期(Bus Cycle) :CPU与外部设备(通常是内存或I/O端口)交换一次数据所需的时间,通常包含4个T状态(T1-T4)。

以8086为例,其标准总线周期由4个时钟周期组成:

| T状态 | 动作描述 |

|---|---|

| T1 | 输出地址信号和ALE(地址锁存允许) |

| T2 | 地址撤销,准备数据传输方向(读/写) |

| T3 | 数据出现在总线上,开始采样 |

| T4 | 完成数据传输,总线释放 |

若外设响应较慢,可在T3后插入等待状态Tw,延长总线周期。

指令执行时间由其所含的总线周期数量决定。例如:

- MOV AX, BX :寄存器间传送,无需访存,仅需1~2个时钟周期。

- MOV AX, [1234H] :需一次内存读操作,至少一个总线周期(4个T状态)。

下表对比几种典型指令的执行时序:

| 指令 | 总线周期数 | 时钟周期数(估算) |

|---|---|---|

| MOV reg, reg | 0 | 2 |

| MOV reg, mem | 1(读) | 6~8 |

| MOV mem, reg | 1(写) | 6~8 |

| ADD reg, imm | 0~1 | 4 |

| CALL near | 1(读)+1(写SP) | 10~14 |

可见,访存操作显著增加执行时间,这也是为何现代CPU普遍配备高速缓存(Cache)来减少对主存的依赖。

2.3 CPU与外部设备的数据交互模型

CPU并非孤立运行,它需要频繁与内存、I/O设备进行数据交换。为此,必须建立高效的 数据通路 ,并在电气层面保证信号完整性。

2.3.1 数据通路设计原则

数据通路是指CPU内部及外部各组件之间传输数据的物理路径,包括内部总线、寄存器接口、外部数据/地址/控制总线等。

关键设计原则包括:

- 总线宽度匹配 :若CPU为16位,但外部数据总线仅为8位,则每次传输需分两次进行,降低效率。

- 单总线 vs 多总线结构 :单总线结构成本低但存在争用问题;多总线(如分离数据与地址总线)提升并行度。

- 三态缓冲器应用 :允许多个设备共享同一总线,避免信号冲突。

内部总线宽度直接影响CPU一次可处理的数据量。例如,8086虽为16位CPU,但其外部数据总线在某些封装中仅为8位(如8086-8),导致性能下降约30%。

2.3.2 典型CPU实例分析:以Intel 8086为例剖析引脚功能与最小/最大模式切换

Intel 8086是16位微处理器的经典代表,采用40引脚DIP封装,支持两种工作模式:

- 最小模式(Minimum Mode) :MN/MX#引脚接+5V,适用于单处理器系统,所有控制信号由8086直接输出。

- 最大模式(Maximum Mode) :MN/MX#接地,用于多处理器系统(如协处理器8087),控制信号由总线控制器8288译码产生。

主要引脚功能如下表所示:

| 引脚名 | 方向 | 功能描述 |

|---|---|---|

| AD0-AD15 | I/O | 分时复用地址/数据总线 |

| A16/S3-A19/S6 | O | 高4位地址/状态信号 |

| NMI | I | 非屏蔽中断请求 |

| INTR | I | 可屏蔽中断请求 |

| RD# | O | 读控制信号 |

| WR# | O | 写控制信号 |

| M/IO# | O | 区分内存访问或I/O访问 |

| DT/R# | O | 数据传输方向(发送/接收) |

| DEN# | O | 数据允许信号 |

| CLK | I | 时钟输入 |

| RESET | I | 复位信号,清空内部状态 |

在最小模式下,8086直接驱动RD#、WR#、M/IO#等信号;而在最大模式下,这些信号由8288根据S0-S2状态码译码生成,支持更复杂的系统配置。

例如,当执行内存写操作时,8086在T1输出地址并激活ALE,T2发出M/IO#=1、WR#=0、DT/R#=1(表示向外发送数据),DEN#=0启用总线驱动器。

这一机制体现了CPU对外部环境的高度适应性,也为后续多核、多总线架构的发展奠定了基础。

3. 指令系统与时序控制机制

现代计算机系统的运行效率与稳定性在很大程度上依赖于其底层的指令系统设计以及精确的时序控制机制。本章深入探讨微处理器如何通过结构化的指令集完成复杂任务,并分析这些指令在硬件层面是如何被逐级分解为微操作、并在严格的时间节拍下协同执行的。从抽象的指令格式到具体的执行流程,再到驱动整个CPU节奏的时钟与状态机机制,我们将构建一个完整的“指令生命周期”模型,揭示程序代码如何转化为电信号并最终驱动计算行为的发生。

理解指令系统不仅涉及对操作码和寻址方式的形式化描述,更需要掌握其背后的设计哲学——即如何在有限的硬件资源中实现最大灵活性与执行效率之间的平衡。与此同时,时序控制系统作为CPU运行的“节拍器”,决定了每一个信号的有效窗口、数据通路的切换时机以及外设交互的同步边界。尤其在多级流水线架构广泛应用的今天,传统的周期划分方法正在经历深刻变革,但其核心逻辑依然根植于经典的T状态模型。

3.1 指令格式与寻址方式理论基础

指令是CPU执行的基本单位,它指示处理器完成某一特定操作,如数据移动、算术运算或跳转控制等。一条完整的机器指令通常由两部分组成: 操作码(Opcode) 和 地址码(Operand) 。操作码定义了要执行的操作类型,而地址码则指明参与该操作的数据来源或目标位置。不同的指令系统采用不同的编码策略来组织这两部分内容,直接影响指令长度、译码复杂度和执行效率。

为了提升编程灵活性与内存利用率,现代指令集普遍支持多种寻址方式。所谓寻址方式,是指确定操作数实际物理地址的方法。不同方式适用于不同场景,例如立即数赋值适合常量初始化,间接寻址可用于动态数组访问,而变址寻址则是循环处理结构数据的核心手段。正确选择寻址方式不仅能简化程序逻辑,还能显著提高运行性能。

3.1.1 操作码与地址码的编码规则

操作码的编码方式直接关系到指令系统的扩展性与译码速度。常见的编码策略包括固定长度操作码和可变长度操作码两种。以Intel 8086为例,其采用的是可变长度操作码设计,允许使用前缀字节扩展功能,从而支持超过上百条指令。这种设计虽然增加了译码复杂度,但提高了指令密度,节省了存储空间。

地址码的数量决定了指令能同时操作的数据个数。根据地址字段数量,可将指令分为以下几类:

| 地址数 | 结构形式 | 示例说明 | 特点 |

|---|---|---|---|

| 零地址 | OP | RET , NOP | 无需显式操作数,常用于控制流 |

| 单地址 | OP A | INC AX , NOT BX | 隐含另一操作数(如累加器) |

| 双地址 | OP A, B | MOV AX, BX , ADD CX, [SI] | 明确源与目的,通用性强 |

| 三地址 | OP A, B, C | ADD R1, R2, R3 (RISC常见) | 表达能力强,但占用较多位 |

三地址指令最具表达力,能够在一条指令中完成“A ← B op C”的运算,极大减少中间变量写回次数,在RISC架构中广泛使用。相比之下,CISC架构倾向于使用双地址甚至单地址指令,通过隐含寄存器(如AX)降低编码开销,但也导致更多内存访问。

考虑如下伪汇编代码片段:

ADD R1, R2 ; 将R2加到R1上,结果存入R1(双地址)

其对应的微操作序列可能为:

1. 取出R2的内容 → TempReg

2. ALU执行 R1 + TempReg

3. 结果写回R1

4. 更新标志位(ZF, CF等)

若采用三地址形式:

ADD R3, R1, R2 ; R3 ← R1 + R2

则原始R1值不受影响,更适合流水线中保持寄存器状态不变的需求。

编码效率与指令长度权衡

假设某系统采用8位操作码,最多支持256种指令。若所有指令均为固定长度(如16位),则剩余8位仅够表示一个地址字段,限制了寻址能力。为此,许多系统采用 扩展操作码技术 ——即根据地址字段数量动态调整操作码位宽。例如:

- 无地址指令:操作码占16位

- 单地址指令:操作码占8位,地址占8位

- 双地址指令:操作码占6位,每个地址占5位

这种方式牺牲了一定的译码速度,但提升了整体编码效率。其本质是在 操作码空间与地址空间之间进行动态分配 ,体现了计算机体系结构中的典型折衷思想。

3.1.2 常见寻址方式详解

寻址方式的选择直接影响程序的简洁性与执行效率。以下是几种典型的寻址模式及其应用场景分析。

立即寻址(Immediate Addressing)

在这种方式中,操作数直接包含在指令本身中。例如:

MOV AX, 1234H

其中 1234H 是立即数,随指令一同取出。优点是速度快,无需额外访存;缺点是灵活性差,不能用于修改数据。

适用场景:初始化寄存器、设置常量阈值。

直接寻址(Direct Addressing)

操作数的地址直接出现在指令中:

MOV AX, [1000H]

表示从内存地址 1000H 处读取数据送入AX。此方式便于访问全局变量,但地址固定,难以实现动态定位。

间接寻址(Indirect Addressing)

指令中给出的是指向实际地址的指针。例如:

MOV AX, [BX]

BX寄存器中存放的是有效地址,CPU先读取BX内容,再以此为地址访问内存。这相当于C语言中的指针解引用 *ptr 。

优势在于可以实现动态数据结构遍历,如链表遍历:

while (ptr != NULL) {

value = *ptr;

ptr = ptr->next;

}

对应汇编可写为:

LOOP:

MOV AX, [BX] ; 取当前节点数据

MOV BX, [BX+2] ; 获取下一个节点地址(假设偏移2字节)

CMP BX, 0

JNE LOOP

变址寻址(Indexed Addressing)

利用基址寄存器与变址寄存器相加得到有效地址:

MOV AL, [SI + 10H]

常用于数组元素访问。设SI指向数组首地址,则 [SI + index] 可快速定位第index个元素。

结合比例因子(如x86中的SIB字节),还可支持非单位步长访问:

MOV EAX, [ESI*4 + ARRAY_BASE] ; 访问int型数组第ESI个元素

基址加变址寻址(Base + Index)

综合使用基址寄存器和变址寄存器:

MOV AX, [BX + SI]

适用于二维数组或结构体成员访问。例如访问结构体数组中某个字段:

struct Person people[10];

people[i].age = 25;

可转换为:

MOV BX, OFFSET people ; 基址

MOV SI, i ; 索引

SHL SI, 1 ; 假设每项2字节

ADD SI, 1 ; age字段偏移

MOV BYTE PTR [BX+SI], 25

下面用Mermaid流程图展示不同寻址方式的选择路径:

graph TD

A[开始解析操作数] --> B{是否为常量?}

B -->|是| C[立即寻址]

B -->|否| D{是否为固定地址?}

D -->|是| E[直接寻址]

D -->|否| F{是否通过寄存器获取地址?}

F -->|是| G[寄存器间接寻址]

F -->|否| H{是否含偏移量?}

H -->|是| I[变址/基址+变址]

H -->|否| J[寄存器寻址]

上述流程体现了编译器或程序员在生成指令时的决策过程。合理运用这些方式,可在保证功能正确的前提下最大化性能。

此外,某些高级架构还引入了 相对寻址 (用于跳转指令)和 堆栈寻址 (用于函数调用参数传递)。以JMP指令为例:

JMP SHORT LABEL

采用相对寻址,目标地址 = 当前IP + 偏移量。这种方式使得代码具有位置无关性,有利于模块化加载。

3.2 指令执行流程与微操作序列

CPU并非一次性执行整条指令,而是将其拆解为一系列细粒度的 微操作(Micro-operations) ,在严格的控制信号驱动下一一完成。这一过程构成了指令执行的核心机制,也是理解计算机内部工作原理的关键所在。

每条指令的执行都遵循一定的阶段划分:取指(Fetch)、译码(Decode)、执行(Execute)、访存(Memory Access)、写回(Write-back)。在简单处理器中,这些阶段串行进行;而在高性能CPU中,则通过 流水线技术 使其重叠执行,大幅提升吞吐率。

3.2.1 典型指令的执行步骤拆解

我们以Intel 8086中的三条基本指令为例,详细剖析其微操作序列。

MOV 指令执行示例

指令: MOV AX, [BX]

该指令将内存地址为BX所指单元的内容加载到AX寄存器中。其执行过程如下:

T1: 地址总线输出BX内容,控制总线发出MEMR(内存读)信号

T2: 存储器准备数据,数据总线上传输字节

T3: 数据进入CPU内部缓冲器

T4: 将低字节写入AL,高字节写入AH(假设为字操作)

对应的微命令序列可表示为:

| 时间周期 | 微操作 | 控制信号 |

|---|---|---|

| T1 | PC → MAR | MEMR |

| T2 | Memory → MDR | - |

| T3 | MDR → IR | - |

| T4 | BX → Address Bus | MEMR |

| T5 | Memory → Data Bus → Temp Register | - |

| T6 | Temp Reg → AL / AH | Write Enable on AX |

注:此处省略了取指阶段,专注于执行阶段。

关键参数说明:

- MAR(Memory Address Register) :保存当前访问的内存地址。

- MDR(Memory Data Register) :暂存从内存读出或待写入的数据。

- IR(Instruction Register) :存放当前正在执行的指令。

整个过程依赖于内部控制总线协调各部件动作,确保数据流动有序。

ADD 指令执行流程

指令: ADD AX, BX

这是一个寄存器到寄存器的加法操作,不涉及内存访问。

1. BX内容送入ALU的一个输入端

2. AX内容送入另一个输入端

3. ALU执行加法运算

4. 结果写回AX

5. 根据结果更新标志寄存器(CF, ZF, SF等)

代码逻辑逐行解读:

// Verilog风格模拟

always @(posedge clk) begin

if (opcode == ADD && src_reg == BX && dst_reg == AX) begin

alu_in1 <= reg_file[AX]; // 读AX

alu_in2 <= reg_file[BX]; // 读BX

alu_op <= ADD_OP; // 设置ALU操作类型

result <= alu_in1 + alu_in2;// 执行加法

reg_file[AX] <= result; // 写回AX

update_flags(result); // 更新标志位

end

end

参数说明:

- alu_op :决定ALU执行何种运算(加、减、与、或等)。

- update_flags() :依据结果设置进位、零、符号等标志位,供后续条件跳转使用。

此类指令因无需访存,执行速度快,属于典型的“寄存器级”操作。

JMP 指令的跳转机制

指令: JMP 2000H

无条件跳转至地址2000H处继续执行。

微操作流程:

1. 将立即数2000H装入程序计数器PC

2. 下一周期从新PC值处开始取指

由于改变了指令流方向,可能导致流水线清空(Pipeline Flush),带来性能损失。因此现代处理器常采用 分支预测 技术提前预判跳转目标,减少停顿。

3.2.2 流水线技术在指令执行中的初步体现

传统顺序执行模式下,每条指令必须等待前一条完全结束后才能开始,造成大量硬件闲置。引入流水线后,多个指令的不同阶段可以并行处理,如同工厂装配线一般提升整体效率。

四阶段经典流水线模型如下:

graph LR

IF[取指] --> ID[译码]

ID --> EX[执行]

EX --> WB[写回]

subgraph 流水线并行执行

I1_IF --> I1_ID --> I1_EX --> I1_WB

I2_IF --> I2_ID --> I2_EX --> I2_WB

I3_IF --> I3_ID --> I3_EX --> I3_WB

end

假设每个阶段耗时1个时钟周期,则N条指令在非流水线下需4N周期完成,而在流水线下仅需(N+3)周期,接近4倍加速。

然而,流水线也带来三大冲突问题:

| 冲突类型 | 成因 | 解决方案 |

|---|---|---|

| 结构冲突 | 资源争用(如共用ALU) | 增加功能单元 |

| 数据冲突 | 后续指令依赖前序未完成结果 | 插入气泡、转发(Forwarding) |

| 控制冲突 | 分支导致流水线断裂 | 分支预测、延迟槽 |

例如,以下代码存在RAW(Read After Write)依赖:

ADD AX, BX

MOV CX, AX ; 依赖AX的新值

若第二条指令在ADD尚未写回AX时就读取,将获得错误数据。解决办法之一是插入 旁路通路(Bypass Path) ,将ALU输出直接转发给下一级输入,避免等待写回完成。

3.3 时序控制系统的设计与实现

CPU的所有操作都必须在统一的时钟节拍下协调进行,否则将导致信号竞争、数据错乱等问题。时序控制系统正是负责生成这些时间基准信号,并按预定顺序激活各个控制部件的中枢机构。

3.3.1 时钟信号驱动下的节拍分配策略

以Intel 8086为例,其总线周期被划分为四个状态:T1、T2、T3、T4。每个状态持续一个时钟周期(CLK),共同构成一次完整的内存或I/O操作。

| 状态 | 动作描述 |

|---|---|

| T1 | 输出地址信息,发出地址锁存信号ALE |

| T2 | 地址撤销,准备传输数据(读/写信号生效) |

| T3 | 数据稳定,进入有效期 |

| T4 | 完成数据传输,撤销控制信号 |

表格示例:读操作时序

| CLK | T1 | T2 | T3 | T4 |

|---|---|---|---|---|

| A/D | Address | High-Z | Data In | High-Z |

| DEN | Low (Enable) | Low | Low | High (Disable) |

| RD | High | Low | Low | High |

代码模拟该时序控制器的行为:

-- VHDL片段:8086风格总线周期控制器

process(clk)

begin

if rising_edge(clk) then

case state is

when T1 =>

addr_bus <= current_addr;

ale <= '1';

state <= T2;

when T2 =>

ale <= '0';

if read_op then rd <= '0'; end if;

if write_op then wr <= '0'; den <= '0'; end if;

state <= T3;

when T3 =>

if read_op then data_in <= memory_data; end if;

state <= T4;

when T4 =>

rd <= '1'; wr <= '1'; den <= '1';

state <= IDLE;

end case;

end if;

end process;

逐行分析:

- 第3行:检测上升沿触发状态迁移。

- 第5–17行:根据不同状态设置相应输出信号。

- ale 在T1置高,通知外部锁存地址。

- den 控制数据总线收发器使能。

- rd/wr 分别控制读写方向。

该设计确保了地址与数据在时间上严格分离,避免总线冲突。

3.3.2 同步与异步时序控制的应用场景选择

同步系统中,所有设备共享同一时钟源,操作严格按照节拍进行。优点是设计简单、易于调试;缺点是对最慢设备敏感,整体速度受限。

异步系统则依靠 就绪信号(READY) 实现协调。当外设未准备好时,拉低READY,迫使CPU插入等待周期(Tw)。这对于连接低速设备(如打印机、键盘)极为重要。

例如,在8086中,若存储器响应慢,可在T3后插入一个或多个Tw状态:

sequenceDiagram

CPU->>Memory: T1: 发送地址

CPU->>Memory: T2: 发出读信号

Memory-->>CPU: READY=0 (未就绪)

CPU->>CPU: 插入Tw1

Memory-->>CPU: READY=1 (就绪)

CPU->>Memory: T3: 接收数据

CPU->>CPU: T4: 结束周期

通过监测READY信号,CPU自动适应外设速度差异,实现了 弹性时序控制 。

综上所述,无论是指令格式的设计、执行流程的分解,还是时序系统的构建,均体现出计算机体系结构中“分层抽象”与“时空协调”的核心理念。只有深入理解这些底层机制,才能真正驾驭软硬件协同工作的全貌。

4. 存储系统结构与内存类型分析

现代计算机系统的性能瓶颈已逐渐从CPU转向存储子系统。随着处理器运算能力的持续提升,存储器在响应速度、带宽和容量上的匹配成为决定整体系统效率的关键因素。本章将深入剖析存储系统的层级架构设计原理,解析主存储器中各类内存技术的核心工作机制,并探讨外存储设备接口协议的技术实现路径。通过电路级分析、时序建模与实际应用场景对比,帮助读者建立对存储系统全面而系统的认知框架。

4.1 存储器层次结构设计原理

计算机系统中的存储资源并非单一均质体,而是按照访问速度、成本与容量进行分级组织的复杂体系。这种分层结构的设计源于程序运行过程中表现出的空间局部性与时间局部性规律。当程序执行时,往往会在短时间内反复访问某些数据或指令(时间局部性),同时倾向于连续访问相邻地址区域(空间局部性)。基于这一特性,构建多级缓存机制可显著提升平均访问效率。

4.1.1 高速缓存(Cache)、主存与辅存的三级架构

典型的存储层次由高速缓存(Cache)、主存储器(Main Memory)和辅助存储器(Secondary Storage)构成。每一层级在速度、容量和单位成本上形成递进关系:

| 层级 | 典型介质 | 访问延迟 | 容量范围 | 单位成本(相对) |

|---|---|---|---|---|

| L1 Cache | SRAM | ~1–3 CPU周期 | 32KB–256KB | 极高 |

| L2/L3 Cache | SRAM | ~10–40周期 | 几百KB至数十MB | 高 |

| 主存(DRAM) | DDR SDRAM | ~100–300周期 | 数GB至数百GB | 中等 |

| 辅存(SSD/HDD) | NAND Flash / 磁盘 | ~微秒至毫秒级 | TB级 | 低 |

该表格清晰地展示了各层级之间的权衡取舍。例如,虽然SRAM速度快且无需刷新,但其每个存储单元需6个晶体管,导致集成度低、成本高昂,因此仅用于小容量高速缓存;而DRAM虽需定期刷新以维持电荷,但单个单元仅需一个晶体管加一个电容,适合大容量部署。

为更直观展示数据流动过程,以下使用Mermaid绘制存储层次的数据迁移流程图:

graph TD

A[CPU] --> B{L1 Cache命中?}

B -- 是 --> C[直接读取数据]

B -- 否 --> D{L2 Cache命中?}

D -- 是 --> E[从L2加载到L1并返回]

D -- 否 --> F{L3 Cache命中?}

F -- 是 --> G[从L3加载至L2/L1]

F -- 否 --> H[访问主存DRAM]

H --> I[触发缺页中断?]

I -- 是 --> J[从SSD/HDD调入页面]

I -- 否 --> K[更新TLB并送回Cache]

此流程图揭示了现代处理器如何通过逐级下探的方式获取所需数据。一旦发生Cache Miss,不仅带来额外延迟,还可能引发总线争用、内存调度开销等问题。为此,操作系统常配合硬件采用预取(Prefetching)策略,在检测到顺序访问模式时提前加载后续块,从而提高命中率。

进一步分析Cache的工作机制,通常采用组相联映射方式平衡灵活性与查找效率。假设某L1 Cache为8KB大小,每行64字节,采用2路组相联结构,则共有:

\text{行数} = \frac{8 \times 1024}{64} = 128 \quad \Rightarrow \quad \text{组数} = \frac{128}{2} = 64

物理地址被划分为三部分:

- Tag :标识来自哪个内存区域

- Index :确定所属Cache组

- Offset :定位组内具体字节位置

代码示例:模拟Cache行结构定义(C语言)

#define CACHE_LINE_SIZE 64

#define WAYS_PER_SET 2

#define NUM_SETS 64

typedef struct {

unsigned long tag;

uint8_t valid;

uint8_t dirty; // 是否修改过

uint8_t data[CACHE_LINE_SIZE];

} cache_line_t;

cache_line_t cache[NUM_SETS][WAYS_PER_SET];

// 地址解析函数

int extract_index(uintptr_t addr) {

return (addr >> 6) & 0x3F; // 偏移6位(64B=2^6),取低6位作为index

}

unsigned long extract_tag(uintptr_t addr) {

return addr >> 12; // 高位作为tag(假设虚拟地址48位)

}

逻辑分析 :

- CACHE_LINE_SIZE 设置为64字节,符合主流CPU缓存行标准;

- valid 标志表示该行是否包含有效数据;

- dirty 用于写回策略判断,若为1则需回写至主存;

- extract_index() 将地址右移6位后与 0x3F (即63)按位与,提取出6位索引值(对应64组);

- extract_tag() 右移12位获得高位标签,忽略低12位(6位offset + 6位index)。

该模型可用于教学仿真或性能评估工具开发。实际CPU中还会引入LRU替换算法、MESI一致性协议等高级机制来管理多核环境下的缓存一致性问题。

4.1.2 存储容量、速度与成本之间的权衡关系

在系统设计阶段,必须根据应用场景合理配置各级存储资源。例如,高性能计算集群注重内存带宽与低延迟,常采用HBM(High Bandwidth Memory)堆叠式显存架构;而嵌入式设备受限于功耗与体积,则优先选用LPDDR4X或eMMC方案。

考虑如下三种典型系统配置策略:

| 应用场景 | Cache配置 | 主存类型 | 外存方案 | 设计重点 |

|---|---|---|---|---|

| 服务器数据库 | 多核大L3 Cache(>100MB) | Registered DDR5 ECC | NVMe SSD阵列 | 高吞吐、容错性 |

| 移动终端 | 小L2+统一L3 | LPDDR5 | UFS 3.1 | 功耗控制、空间紧凑 |

| 工业控制器 | 固定映射SRAM缓存 | 工规级DDR3 | CompactFlash | 可靠性、抗干扰 |

上述配置差异体现了“没有最优,只有最合适”的工程哲学。以工业控制器为例,尽管DDR3速度落后于DDR5,但其成熟的温度适应性和长期供货保障使其在恶劣环境中更具优势。

此外,虚拟内存机制进一步扩展了可用地址空间。通过MMU(Memory Management Unit)将虚拟地址转换为物理地址,操作系统可在物理内存不足时将不活跃页面交换至磁盘Swap分区。然而,频繁的Page In/Out会导致“抖动”(Thrashing)现象,严重降低系统响应速度。

为此,Linux内核提供了 vm.swappiness 参数调节换页倾向,默认值为60。管理员可根据负载类型调整该值:

# 查看当前swappiness值

cat /proc/sys/vm/swappiness

# 临时设置为10(减少swap使用)

echo 10 > /sys/fs/cgroup/memory/vm.swappiness

# 永久生效需修改/etc/sysctl.conf

vm.swappiness=10

参数说明 :

- swappiness=0 :尽可能避免使用swap,仅在绝对必要时启用;

- swappiness=100 :积极使用swap,即使内存仍有空闲;

- 对于运行大型应用的服务端,建议设为10~30,避免因短暂内存峰值触发不必要的磁盘IO。

综上所述,存储层次结构不仅是硬件布局的结果,更是软硬件协同优化的产物。理解其背后的设计逻辑,有助于在系统调优、故障排查及新产品研发中做出科学决策。

4.2 主存储器类型及其电气特性

主存储器是连接CPU与外设的核心枢纽,承担着程序指令与运行数据的即时存取任务。其性能直接影响系统的响应速度与并发处理能力。本节将系统梳理RAM与ROM的技术演进路径,比较SRAM与DRAM的电路实现差异,并深入讲解非易失性存储器的应用边界划分。

4.2.1 RAM与ROM的技术演变

随机存取存储器(Random Access Memory, RAM)支持快速读写操作,断电后内容丢失,属于易失性存储器。主要分为静态RAM(SRAM)与动态RAM(DRAM)两类。

SRAM与DRAM的电路结构与刷新机制对比

SRAM的基本存储单元由6个MOSFET组成双稳态触发器结构,如图所示:

Vcc

|

+---o---+

| |

Q1 Q3

| |

+---o---+----> Out

|

Q5

|

Q2 Q4

| |

+---o---+

|

GND

其中Q1-Q4构成交叉耦合反相器,保持0/1状态稳定;Q5/Q6为传输门,受字线(Word Line)控制通断。只要供电不断,SRAM即可无限期保持数据,无需刷新。

相比之下,DRAM利用电容存储电荷表示比特,每个单元仅需一个晶体管与一个电容(1T1C结构)。但由于漏电流存在,电荷会在几十毫秒内衰减,故必须周期性刷新(通常为64ms内完成所有行刷新)。

| 特性 | SRAM | DRAM |

|---|---|---|

| 单元结构 | 6T | 1T1C |

| 是否需要刷新 | 否 | 是(64ms周期) |

| 速度 | 快(<1ns) | 较慢(~50ns) |

| 功耗 | 高待机功耗 | 低静态功耗 |

| 成本 | 高($/bit) | 低 |

| 应用场景 | Cache | 主存 |

代码示例:模拟DRAM刷新请求生成器(Verilog片段)

module dram_refresh_controller (

input clk,

input reset,

output reg refresh_req

);

parameter REFRESH_INTERVAL = 15_625; // 每15.625μs触发一次(64ms/4096行)

reg [13:0] counter;

always @(posedge clk or posedge reset) begin

if (reset)

counter <= 0;

else if (counter >= REFRESH_INTERVAL - 1) begin

counter <= 0;

refresh_req <= 1;

end else begin

counter <= counter + 1;

refresh_req <= 0;

end

end

endmodule

逻辑分析 :

- 使用14位计数器跟踪时间间隔;

- REFRESH_INTERVAL 设为15625(对应15.625μs,假设时钟为1MHz);

- 每达到阈值即发出 refresh_req 信号,通知内存控制器启动行刷新;

- 实际系统中由内存控制器(如Intel MCH)统一调度刷新操作,避免影响正常读写。

值得注意的是,现代DDR SDRAM采用“自刷新”(Self-refresh)模式,在系统休眠时仍能维持数据完整性,极大提升了移动设备的续航表现。

PROM、EPROM、EEPROM与Flash的应用边界划分

只读存储器(ROM)家族经历了多次技术迭代:

| 类型 | 写入方式 | 擦除方式 | 耐久性 | 典型用途 |

|---|---|---|---|---|

| PROM | 一次性烧录 | 不可擦除 | 1次 | 固件备份 |

| EPROM | 编程电压写入 | UV光照射擦除 | ~100次 | 开发调试 |

| EEPROM | 字节级电擦写 | 电信号擦除 | ~10万次 | 参数存储 |

| NOR Flash | 块擦除+字节写 | 电信号 | ~10万次 | BIOS存储 |

| NAND Flash | 页读写+块擦除 | 电信号 | ~3K–100K次 | SSD/U盘 |

NOR Flash支持XIP(eXecute In Place),允许CPU直接从中取指执行,适用于Bootloader存储;而NAND Flash因密度高、成本低,广泛用于大容量数据存储。

代码示例:SPI Flash读取ID指令序列(C语言驱动片段)

void spi_flash_read_jedec_id(uint8_t *manuf_id, uint16_t *dev_id) {

spi_select_device(FLASH_CS);

spi_write_byte(0x9F); // JEDEC ID命令

*manuf_id = spi_read_byte();

*dev_id = (spi_read_byte() << 8) | spi_read_byte();

spi_deselect_device(FLASH_CS);

}

参数说明 :

- 0x9F 为标准JEDEC ID读取命令;

- 返回制造商ID(如0xC8为GigaDevice)与设备型号编码;

- 用于自动识别Flash芯片型号,便于加载正确驱动。

该机制在U-Boot等引导程序中广泛应用,确保兼容多种硬件平台。

4.2.2 内存芯片选型与地址译码电路设计

在嵌入式系统或定制主板设计中,需手动规划内存映射与片选逻辑。常见方法包括线选法与译码器法。

以8086系统为例,假设使用两片62256(32KB×8)SRAM构建64KB内存空间,地址范围为00000H–0FFFFH。A15用于区分高低片:

高位片:A15 = 1 → 地址 8000H–FFFFH

低位片:A15 = 0 → 地址 0000H–7FFFH

地址译码电路可采用74LS138三八译码器实现更复杂的片选控制。例如:

| 输入(C,B,A) | 输出Y0–Y7 | 用途 |

|---|---|---|

| 0,0,0 | Y0=0 | ROM片选 |

| 0,0,1 | Y1=0 | RAM Bank0 |

| 0,1,0 | Y2=0 | RAM Bank1 |

| … | … | … |

表格化设计有助于避免地址重叠与资源浪费。

4.3 外存储接口技术实现机制

外部存储设备通过标准化接口与主机通信,其实现机制涉及协议栈、电气规范与数据传输模式等多个层面。

4.3.1 IDE/SATA硬盘接口协议解析

IDE(Integrated Drive Electronics)曾是PC主流硬盘接口,后演化为SATA(Serial ATA)。两者在物理连接与传输模式上有显著区别。

PIO(Programmed I/O)模式下,CPU全程参与数据搬运,效率低下:

while (count--) {

data = inw(0x1F0); // 从数据寄存器读取

*buffer++ = data;

}

而DMA(Direct Memory Access)允许外设直接与内存交互,释放CPU负担。配置IDE DMA需设置PRDT(Physical Region Descriptor Table)描述符表:

struct prdt_entry {

uint32_t base_addr; // 物理地址

uint32_t byte_count : 23;

uint32_t reserved : 8;

uint32_t end_of_table: 1;

};

驱动程序初始化DMA引擎后,硬盘控制器自动完成数据传输,仅在结束时触发中断通知CPU。

4.3.2 PCI总线在高速外设连接中的角色定位

PCI(Peripheral Component Interconnect)总线提供即插即用(PnP)功能,设备配置空间包含Vendor ID、Device ID等字段,OS可通过枚举识别硬件。

中断共享机制允许多个设备共用同一IRQ线,依赖MSI(Message Signaled Interrupts)提升可靠性。PCI配置头结构如下:

| Offset | 名称 | 描述 |

|---|---|---|

| 0x00 | Vendor ID | 厂商标识(如0x8086为Intel) |

| 0x02 | Device ID | 设备型号 |

| 0x3C | IRQ Line | 分配的中断号 |

| 0x3D | IRQ Pin | 请求的中断引脚(INTA#–INTD#) |

这些机制共同支撑了现代计算机灵活扩展的能力。

5. I/O接口技术与综合应用实践

5.1 I/O端口编址与数据传输方式

在微机系统中,CPU与外部设备(如键盘、显示器、硬盘等)之间的信息交换必须通过I/O接口电路完成。为了实现高效、可靠的数据通信,需合理设计I/O端口的编址方式和选择合适的数据传输机制。

5.1.1 统一编址与独立编址的优劣分析

I/O端口有两种主要的地址分配方式: 统一编址 (Memory-Mapped I/O)和 独立编址 (Isolated I/O)。

| 编址方式 | 地址空间共享 | 使用指令类型 | 优点 | 缺点 |

|---|---|---|---|---|

| 统一编址 | 是 | 普通访存指令(MOV等) | 简化指令系统,便于使用高级语言访问 | 占用主存地址空间,可能影响内存可用性 |

| 独立编址 | 否 | 专用I/O指令(IN/OUT) | 不占用内存地址空间,I/O操作更明确 | 需要额外的控制信号和指令支持 |

例如,在x86架构中采用的是独立编址方式,使用 IN AL, DX 从指定端口读取数据,而ARM架构通常采用统一编址,将外设寄存器映射到特定内存区域,如:

#define UART_DR (*(volatile unsigned char*)0x10000000)

UART_DR = 'A'; // 向串口发送字符'A'

该方式使得程序员可以像操作变量一样访问硬件寄存器,提升了编程灵活性。

5.1.2 程序查询、中断驱动与DMA三种传输模式对比

不同的I/O数据传输方式适用于不同性能需求的应用场景:

| 传输方式 | CPU参与程度 | 实时性 | 效率 | 典型应用场景 |

|---|---|---|---|---|

| 程序查询 | 高 | 低 | 低 | 简单LED控制 |

| 中断驱动 | 中 | 高 | 中 | 键盘输入、串口通信 |

| DMA | 极低 | 高 | 高 | 磁盘读写、高速ADC采集 |

-

程序查询 :CPU不断轮询状态寄存器,直到设备就绪。简单但浪费CPU资源。

asm WAIT: IN AL, STATUS_PORT TEST AL, 01H JZ WAIT IN AL, DATA_PORT -

中断驱动 :设备准备好后向CPU发出中断请求,CPU暂停当前任务执行中断服务程序(ISR),提高响应速度。

-

DMA(Direct Memory Access) :由DMA控制器接管总线,在外设与内存间直接传输数据,无需CPU干预。典型流程如下:

graph TD

A[外设准备就绪] --> B{是否启用DMA?}

B -- 是 --> C[DMA控制器申请总线]

C --> D[CPU释放总线控制权]

D --> E[DMA完成数据传输]

E --> F[通知CPU传输结束]

B -- 否 --> G[使用中断或查询方式]

在高性能嵌入式系统中,常结合多种方式:如键盘使用中断,磁盘使用DMA,状态指示灯则用查询法,以达到资源最优配置。

5.2 典型接口电路设计实战案例

5.2.1 简单并行接口芯片8255A的应用设计

Intel 8255A是一种可编程并行接口芯片,广泛用于连接开关、按键、数码管等外设。其具有三个8位端口(PA、PB、PC)和一个控制寄存器,支持三种工作方式:

- 方式0:基本输入/输出

- 方式1:选通输入/输出(带握手信号)

- 方式2:双向总线方式(仅PC口支持)

假设使用方式0,将PA口设为输出控制LED,PB口设为输入读取按键状态。初始化代码如下(x86汇编):

MOV DX, 0303H ; 控制端口地址

MOV AL, 82H ; 方式控制字:PA输出,PB输入,PC未用

OUT DX, AL ; 写入控制字

其中控制字 82H 二进制为 10000010 ,含义如下:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 方式选择 | PA方向 | PC上半部 | PB方向 | PC下半部 |

随后可通过以下指令进行数据读写:

MOV DX, 0300H ; PA端口地址

MOV AL, 0FH ; 点亮低4位LED

OUT DX, AL

MOV DX, 0301H ; PB端口地址

IN AL, DX ; 读取按键状态

此结构可用于构建简易工业控制面板,实现人机交互功能。

5.2.2 串行通信接口UART与RS-232标准实现

通用异步收发器(UART)是实现串行通信的核心组件。以常见的16C550为例,其关键参数包括波特率、数据位、停止位和校验方式。

常见帧格式定义:

- 起始位:1 bit(低电平)

- 数据位:5~8 bits(LSB先行)

- 校验位:奇/偶/无

- 停止位:1 或 1.5 或 2 bits(高电平)

波特率计算公式(基于1.8432MHz晶振):

Divisor = 1843200 / (16 × BaudRate)

设置9600波特率时:

Divisor = 1843200 / (16 × 9600) = 12

配置步骤(伪代码):

// 使能DLL/DLM访问

write_reg(LCR, 0x80);

write_reg(DLL, 12);

write_reg(DLM, 0);

// 设置数据格式:8N1

write_reg(LCR, 0x03);

// 使能FIFO并清空

write_reg(FCR, 0x07);

物理层采用RS-232标准,电压范围±3V~±15V,使用DB9接口,典型引脚包括:

| 引脚 | 名称 | 方向 | 功能 |

|---|---|---|---|

| 2 | RxD | 输入 | 接收数据 |

| 3 | TxD | 输出 | 发送数据 |

| 5 | GND | — | 信号地 |

| 7 | RTS | 输出 | 请求发送 |

| 8 | CTS | 输入 | 清除发送 |

实际应用中常通过MAX232电平转换芯片实现TTL与RS-232之间的电平匹配,确保长距离通信稳定性。

简介:《微机原理与接口技术》是深入理解计算机硬件架构与软硬件交互的核心课程,涵盖计算机基本结构、指令系统、存储体系、I/O接口技术等内容。本试题库由重庆科技学院教师精心编写,包含选择题、填空题、判断题、简答题和综合题等多种题型,全面覆盖CPU结构、数制转换、总线技术、中断机制及常见接口(如USB、PCI、SATA)等知识点。经过实际教学验证,该资源不仅有助于学生巩固理论知识、提升实践分析能力,也可作为教师教学辅助工具,适用于课程复习、考试备考及硬件开发人员的技能提升。

540

540

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?