问题描述:

用zynq7020控制一个ADC,发现采样的数据总是实际值的1/2,ps侧启动的是linux系统;如果是用jtag直接控制的话,采样值就是正确的。

测试中发现给adc的clk从20mhz变成了40mhz,这个adc工作时钟最大只能到27mhz,所以采样值不对。

该clk时钟来自前面的PLL核,发现PLL核的input时钟变成了100mhz,而我们设置的是50mhz。

input时钟直接来自ps侧的IP核,是ps直接出给pl侧的fabric时钟,内部应该也是个PLL核产生的。

为什么设置的频率会翻倍?

完全一样的配置,在之前一直没出错,只是这几天必现。

然后让ps直接出时钟给adc,频率翻倍;

改变FCLK_CLK0的输出频率,频率翻倍;

让FCLK_CLK0~3都出时钟,频率翻倍;

删除重新添加ps核,频率翻倍;

更换另一块核心板;频率翻倍;--- 说明翻倍的bug已经在bit文件里面

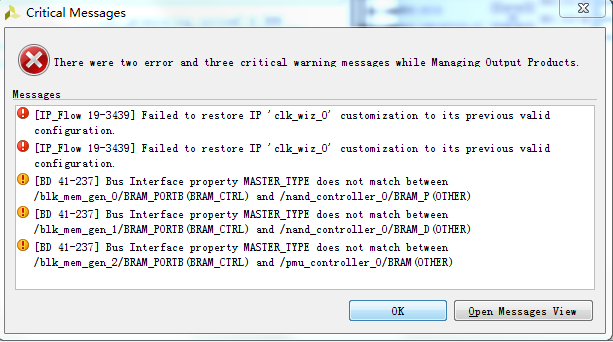

最近新跳出一个错误。几次generate后就没有了。官网的issue说这个error不是问题

Failed to restore IP 'clk_wiz_0' customization to its previous valid configuration

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?