FPGA学习笔记:阻塞赋值和非阻塞赋值

刚开始学习FPGA,对于Verilog HDL 中两种赋值语句(阻塞赋值、非阻塞赋值)学习后,简单做一个学习笔记加深理解。

引出例子

有a,b,c三个输入信号,需要计算[1:0]out=a+b+c

我们采用中间变量d存放第一次加法的值:

d=a+b

out=d+c

那么在以上两次加法操作时就存在两种赋值选择:阻塞赋值和非阻塞赋值

接下来,咱们就对两种不同的赋值方式分别进行分析研究

阻塞赋值 “=”

使用阻塞赋值语句时,赋值语句的顺序与其对应生成的电路不一样,阻塞赋值语句相互之间的关系是顺序执行的关系,以下两种代码顺序可以直观地解释阻塞赋值的顺寻执行特性:

input a,b,c;

output reg [1:0]out;

reg [1:0]d;

d=a+b;

out=d+c;

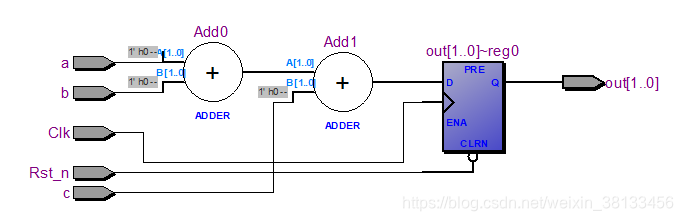

以上代码顺序产生的电路如下图所示:首先执行a+b,再把a+b的结果与c相加,再次相加的结果放入到寄存器中保存。

input a,b,c;

output reg [1:0]out;

reg [1:0]d;

out=d+c;

d=a+b;

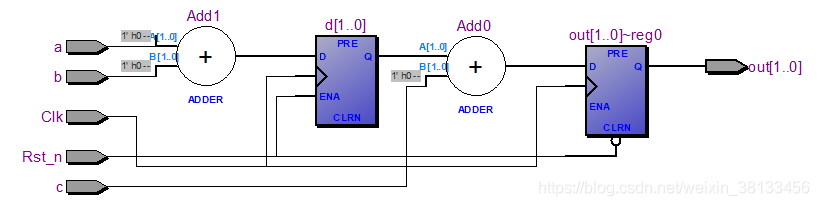

当调换赋值顺序后,生成的电路也不一样:首先赋值的是out=d+c,然而d还没有得到计算结果,所以就会出现a+b的结果被放入到寄存器中,当计算d+c时,d的值是从寄存器中得到。

以上两个简单的例子和其对应的生成的电路可以理解和证明阻塞赋值语句的顺序执行的特性。当顺序执行赋值语句时,对于一些得不到的数据时则会使用到寄存器解决,这也就会造成了数据信息延迟和一些其他的影响。

非阻塞赋值 “<=”

与阻塞赋值不同的是非阻塞赋值,这种赋值方式与复制的顺序无关,可以理解为赋值语句之间是并行执行的 ,阻塞赋值方式所赋值的变量不能立即就为下面语句所用,只有当块结束后才能得到上一次所附的值,这种赋值方式是编写可综合的时序逻辑时常用的赋值方式。还是用之前的例子进行说明:

第一种赋值顺序:

d<=a+b;

out<=d+c;

第二种赋值顺序:

out<=d+c;

d<=a+b;

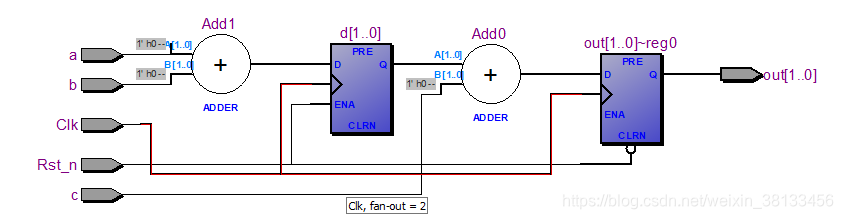

这两种不同顺序的赋值方式生成的电路是一样的,如下图所示:a+b的计算结果都被保存在寄存器之中,计算d+c时先从寄存器中取出a+b的结果再与c相加。

1605

1605

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?