【JESD204系列】一、JESD204总目录

总链接:

链接:

【JESD204系列】一、JESD204总目录

【JESD204系列】二、JESD204概述

【JESD204系列】三、JESD204B标准分层

【JESD204系列】四、JESD204B实现类型

【JESD204系列】五、传输层设计原理

【JESD204系列】六、加解扰模块的设计原理

【JESD204系列】七、8B10B编码

0、术语和定义

8B10B编码: 指定的DC平衡的面向八位字节的数据编码。

字符: 8B10B编码产生的符号。

代码组: 一组十个比特,在表示数据时传达一个八位字节。

字符时钟: 用于确认8B10B字符或八位字节排序的信号。

时钟发生器: 用于向JESD204B系统中的各种设备生成同步相位对准器件时钟的电路。注意时钟发生器电路可以包括一个或多个时钟发生器设备,但是它们必须使用公共源时钟。

控制接口: 一种特定于应用程序的接口,用于在转换器设备和逻辑设备之间以及或在设备和更高层应用程序级别之间传递信息(通常是状态和控制信息)。

转换时钟: 用于确认转换器中模拟采样时刻的信号。通常转换时钟与采样时钟相同,除了在插值dac或抽取adc的情况下,转换时钟比采样时钟更快。在所有情况下,转换时钟都是从器件时钟派生的。

转换器设备: 包含一个或多个转换器的组件封装。

数据链路: 由两个设备和互连数据电路组成的组件,由链路协议控制。

器件时钟: 设备必须从中生成本地时钟的主时钟信号。

帧: 一组连续的八位字节,其中每个八位字节的位置可以通过参考帧对齐信号来识别。

注1:帧对齐信号不一定出现在每帧中。

注2:在JESD204中,帧由F个八位字节组成,并在单个通道上传输。

帧时钟: 用于定序帧或监视其对齐的信号。

帧周期: 帧时钟的一个周期,即一帧的持续时间。在一个帧周期内,在多通道链路的每个通道上传输一个帧。

空闲模式: 用于当前未采样数据的转换器的操作模式。

无效代码组: 根据当前运行差异,在8B10B解码表的正确列中找不到的代码组。

线时钟: 用于对电接口上的串行位进行排序的信号。

本地时钟: 从器件时钟在设备内部派生的时钟,用于在设备内实现JESD204B链路。

逻辑器件: 仅包含或主要包含数字逻辑的组件包;例如,ASIC或FPGA。

多帧: 一组连续帧,其中可以通过参考多帧对准信号来识别每个帧的位置。

注1多帧对齐信号不一定出现在每个多帧中。

注2在JESD204中,多帧由K个帧组成,并在单个通道上传输。

多帧时钟: 用于对多帧进行排序或监视其对齐的信号。

多点链路: 互连三个或更多设备的数据通信链路。

接收器: 连接到通道的电路,用于将串行比特流重建为时间对齐的帧。接收器由一个物理层块和一个链路层块组成。

接收器块: 接收器传输层与连接到一条链路的所有接收器链路层和物理层块的组合。

接收器设备: 包含一个或多个接收器块的组件包。

差分信号(P,N)的上升沿: 当信号P从低逻辑电平变为高逻辑电平并且信号N从高逻辑电平变为低逻辑电平时发生的同时转换。

运行差异: 值为+或-的二进制参数,表示8B10B代码组序列中的1和0之间的不平衡。

采样时钟: 用于定义帧内样本边界的信号。通常采样时钟与帧时钟相同,在一个帧内每个转换器有多个样本的情况下,采样时钟是帧时钟的整数倍。在所有情况下,采样时钟都是从器件时钟导出的。

加扰器: 一种随机机制,用于消除连续相同传输符号的长串,并在不改变信令速率的情况下避免信号频谱中出现谱线。

源时钟: 从中导出各种其他时钟信号的振荡器。该振荡器通常是时钟发生器设备内的VCO,或时钟发生器电路内的外部VCO。

SYSREF: 一种周期性、一次或“间隙”周期性信号,用于对齐JESD204B子类1设备中的本地时钟的边界。SYSREF必须与器件时钟源同步。

发送器: 串行化输入帧并在通道上传输所得比特流的电路。发射机由一个链路层块和一个物理层块组成。

发射机块: 发射机传输层和连接到一条链路的所有发射机链路层和物理层块的组合。

发射机设备: 包含一个或多个发射机块的组件包。

有效代码组: 根据当前运行差异,在8B10B解码表的正确列中找到的代码组。

1、符号和缩写的含义

| 缩略词 | 英文 | 释义 |

|---|---|---|

| LMFC | Local Multi Frame Clock | 本地多帧时钟 |

| LEMC | Local Extended Multiblock Clock | 本地扩展多块时钟 |

| CDR | Clock Data Recovery | 时钟和数据恢复 |

| MCDA | Multiple Converter Device Alignment | 多转换器设备对准 |

| CGS | Code Group Synchronization | 代码组同步 |

| ILAS | Initial Lane Alignment Sequence | 初始通道对齐序列 |

| RBD | RX Buffer Delay | 接收端缓冲器延迟 |

| RD | Running Disparity | 极性偏差 |

2、链路配置参数含义及取值范围

| 参数名 | 含义 | 取值范围 |

|---|---|---|

| M | 每个设备中的转换器数 | 1-256 |

| L | 每个转换器链路的通道数 | 1-32 |

| F | 每个帧中的字节数 | 1-256 |

| S | 每帧中每个转换器的采样点数 | 1-32 |

| N | 转换器分辨 | 1-32 |

| N’ | 每个采样的总比特数 | 1-32 |

| K | 每个多帧中帧的数量 | 1-32 |

| CF | 每个链路每个帧周期的控制字数量 | 0-32 |

| CS | 每个采样的控制比特数 | 0-3 |

| HD | 高数据密度模式使能 | 0-1 |

3、控制字符

| 字符简写 | 字符 | 编码前数值 | RD=-1时编码结果 | RD=+1时编码结果 | 功能说明 |

|---|---|---|---|---|---|

| /R/ | /K28.0/ | 000_11100 | 001111_0100 | 110000_1011 | 多帧开始 |

| /A/ | /K28.3/ | 011_11100 | 001111_0011 | 110000_1100 | 通道对齐 |

| /Q/ | /K28.4/ | 100_11100 | 001111_0010 | 110000_1101 | 链路配置数据开始 |

| /K/ | /K28.5/ | 101_11100 | 001111_1010 | 110000_0101 | 组同步 |

| /F/ | /K28.7/ | 111_11100 | 001111_1000 | 110000_0111 | 帧同步 |

4、subclass0~2确定延迟

subclass0:不支持确定延迟;

subclass1:SYSREF

subclass2:SYNC~。

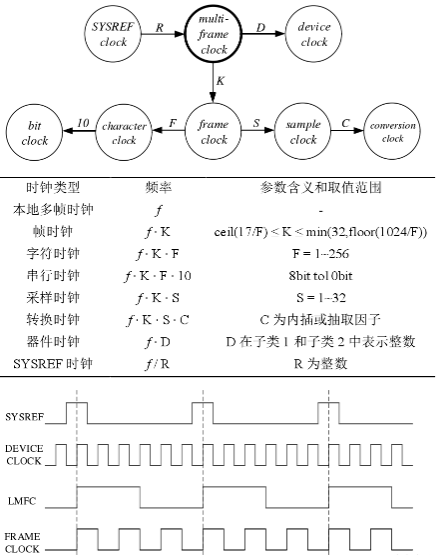

5、时钟

源时钟: 从中导出各种其他时钟信号的振荡器。该振荡器通常是时钟发生器设备内的VCO,或时钟发生器电路内的外部VCO。

器件时钟: 器件必须从中生成本地时钟的主时钟信号。

转换时钟: 用于确认转换器中模拟采样时刻的信号。通常转换时钟与采样时钟相同,除了在插值dac或抽取adc的情况下,转换时钟比采样时钟更快。在所有情况下,转换时钟都是从器件时钟派生的。

帧时钟: 用于定序帧或监视其对齐的信号。

多帧时钟: 用于对多帧进行排序或监视其对齐的信号。

本地时钟: 从器件时钟在器件内部派生的时钟,用于在器件内实现JESD204B链路。

采样时钟: 用于定义帧内样本边界的信号。通常采样时钟与帧时钟相同,在一个帧内每个转换器有多个样本的情况下,采样时钟是帧时钟的整数倍。在所有情况下,采样时钟都是从器件时钟导出的。

线时钟: 用于对电接口上的串行位进行排序的信号。

各时钟关系图:

5、同步对齐过程

发送器和接收器各维护一个LMFC,所有发送器和接收器连接到一个公共(源)SYSREF,这些器件利用SYSREF复位其LMFC,这样所有LMFC应互相同步(在一个时钟周期内)。

SYSREFsignal(DeviceSubclass1):

a、确定时延(小于1个多帧时钟周期)。

b、对齐和器件时钟同源,LMFC周期的整数倍,在DeviceClk沿变化时采样SYSREF信号,确定时延,对齐多帧和帧时钟。SYSREF用于对齐所有收发器件LMFC相位。

SYNC~signal:

同步请求信号。接收端与接收器帧时钟同步。CGS后在接收端LMFC边沿拉高。释放SYNC(所有器件都会看到)后,发送器在下一次(TX)LMFC绕回0时开始ILAS。如果F*K设置适当,大于(发送器编码时间)+(线路传播时间)+(接收器解码时间),则接收数据将在下一个LMFC之前从接收器的SERDES传播出去。接收器将把数据送入FIFO,然后在下一个(RX)LMFC边界开始输出数据。发送器SERDES输入与接收器FIFO输出之间的已知关系称为确定性延迟。

1112

1112

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?