本章介绍了一些简单的处理器结构的设计,甚至介绍了一些底层电路设计语言HCL。这些吧,基本上已经跟软件开发脱离了关系,当做开开眼界吧。很多地方,都是走马观花,也看不太懂,想着也关系不大,就简单记录一下吧。

引言

在计算机科学中,用巧妙的方法在提高性能的同时,又保持一个更简单、更抽象的功能模型是一个比较广泛被接受的思想。在web浏览器或像平衡二叉树和哈希表这样的信息检索数据结构中使用缓存,就是这样的例子。

- 从智力方面来说,处理器设计是非常有趣的。它需要完成复杂的任务,而结构又要尽可能的简单。

惭愧,可能智力跟不上吧,都看不懂,何来乐趣可言呢?

- 理解处理是如何工作的能够帮助理解整个计算机系统是如何工作的。

HCL(Hardware Control Language)是硬件控制语言。

halt指令会导致整个系统停止,IA32中,应用程序不允许使用该指令。

4.1 RISC和CISC指令集

CISC是复杂指令集,RISC与之相对,是精简指令集。CISC首先出现,后来随着各种高级指令的加入,指令集变得非常庞大。于是有些人就发展出了RISC,他们认为很多指令编译器很难生成,也很少用到,使用更少的指令可以用更少的硬件来实现,并以高效的流水线结构组织起来。

4.2 逻辑设计和硬件控制语言HCL

啊,我为什么要学HCL?

大多数现代电路技术都是用信号线上的高电压或低电压来表示不同的值。例如,逻辑1是用1.0伏的电压表示,逻辑0则是用0.0伏的低电压表示。要实现一个数字系统需要三个部分:

- 计算位的函数的组合逻辑

- 存储位的存储器元素

- 控制存储器元素更新的时钟信号

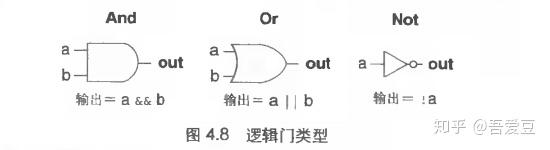

4.2.1 逻辑门

逻辑门是数字电路的基本计算元素。下面是三个基本的逻辑门:

这And和Or长的有点像啊,这样看电路图不是很容易晕么。

4.2.2 组合电路和HCL布尔表达式

多个逻辑门组合有一定的规则:

- 两个或多个逻辑门的输出不能直接连到一起,否则信号会冲突,只能以新的逻辑门连接到一起。

- 逻辑门的网必须是无环的,否则可能导致计算有歧义。

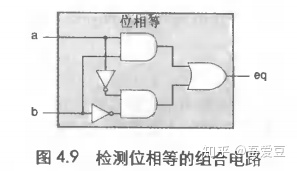

例如有HCL的代码如下,则对应的电路图如下图:

bool eq = (a && b) || (!a && !b);

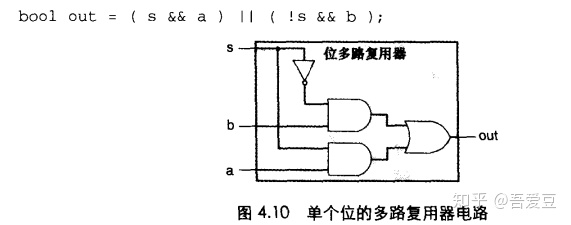

来看另一个典型的电路:

这个bool等式也很经典,乍看还以为等价于:

out = s ? a : b; 再一看好像不对,再仔细看确实等价,捂脸...

4.2.3 字级组合电路和HCL整数表达式

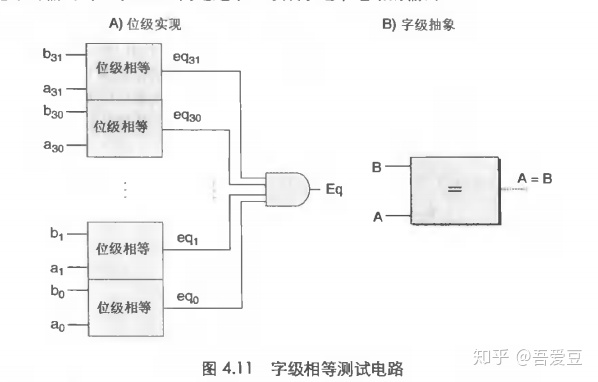

上面的单个逻辑门只能处理单个位,要想处理一个32位的数值是否相等,是否就是排32个上面的电路来检测呢?还真是。

这里的位级相等就是4.9那个电路了。

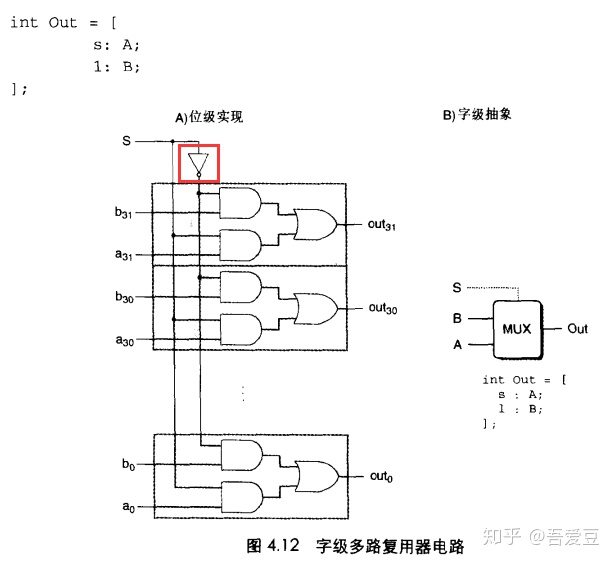

对于4.10的多路复用的扩展则稍微不同,因为s作为控制变量可以只使用一次not逻辑门,而不用重复上面的电路:

可以看到not逻辑门只用了一次,其他部分则重复。

HCL电路相关的,到这就差不多了,后面就感觉有点高深的样子,就不深入研究了。

4.2.5 存储器和时钟控制

组合电路从本质上讲,不存储任何信息。相反,他们只是简单的响应输入信号,产生等于输入的某个函数输出。

硬件概念上的寄存器跟之前机器级寄存器有所区别。硬件寄存器由输入电线和输出电线跟其他部分连接,当时钟变化的时候,输出才会变化成输入数据一致,其他时候保持一致。

4.3 处理器操作顺序

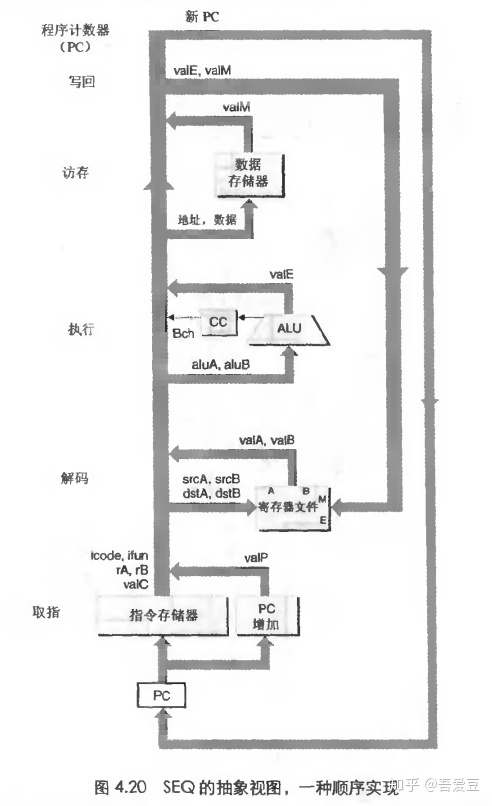

处理器处理指令的大致顺序如下:

- 取值:从存储区读入指令,地址为PC的值。

- 译码:从寄存器读入最多两个操作数。

- 执行:ALU执行指令的操作,计算存储器引用的有效地址等操作。

- 访存:该阶段可以从存储器写入或读取数据

- 写回:最多可以将两个数据写回到寄存器

- 更新PC

从这个图上,可以看出取值之后,PC实际就更新了。符合上一章学习到知识

但是,从电路的角度,在下一个时钟周期前,PC的输出依然还是之前的值,但下次试图访问PC的时候,肯定是新的时钟周期了,输出也必然变成了新的值。

后面都是讲处理器指令的具体实现、流水线的处理、PC预测、流水线带来的数据冒险及解决等等。基本上我也看不懂,后面的略过了

本章,走马观花、风驰电掣的对控制器有了惊鸿一瞥。芯片设计果然高端,不是我辈随便看看就能入门的。

932

932

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?