一、概述

组成:逻辑电路,摆阔管理信息传输规则的电路,连接各功能部件,所以,总线 ≠ 连接线

特性:在任何时刻,只可以有一个部件向总线上发送信息,但是可以有多个部件同时从总线上接收信息

总线标准:为了使不同厂家生产的各类模块化产品具有较好的 兼容性和互换性 ,计算机行业制定了总线标准

机械特性:总线机械连接的指标,包括总线使用的插座和插头

电气特性:每根传输线上信号的传递方向和有效电平范围等

功能特性:总线上所传信号的功能,可分为地址总线、数据总线、控制总线

时间特性:总线中任一根线上的信号在什么时间有效,一般用信号的时序关系图来说明

性能指标

总线宽度:总线的根数,单位 bit

总线工作频率:用于协调总线上各种操作的时钟信号频率

总线带宽:每个时钟周期在总线上可以传输的数据量

数据传输率:每个系统周期在总线上传输的数据量

分类

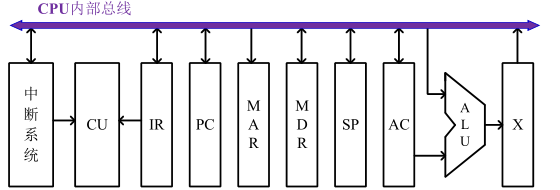

片内总线

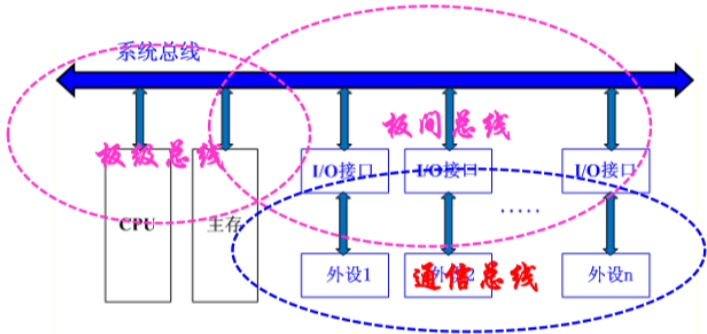

系统总线

总线周期:一次完整的总线传送操作所需要的时间

正常总线周期:一次地址传送时间 + 一次数据传送时间

BURST 总线周期:一次地址传送时间 + 多次数据传送时间

总线的等待状态:在正常总线周期中,若由于被读写的部件速度慢,一次数据时间内不能完成读写,需要增加一个或多个数据时间

总线通信过程

申请分配:主线 -> 控制总线,控制总线判优

寻址:总线 -> 主模块,发送地址、读写命令,启动从模块

传送:主从模块通过总线进行数据交换

结束:主模块撤出占用信号

二、总线结构

单总线结构

多总线结构

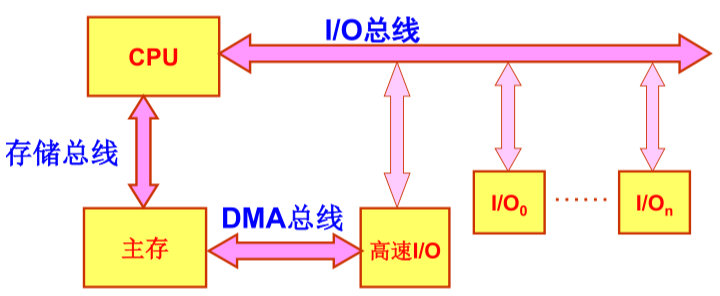

以 CPU 为中心的双总线结构:IO 不能直接访存

以 主存 为中心的双总线结构:IO 可以直接访存(但是不能和 CPU 同时访存)

三总线结构

三、总线管理

整个计算机系统中,各个模块根据是否对总线具备控制能力划分为:

主模块:具有申请、启动总线操作的部件,比如 CPU、DMA 控制器、I/O 接口等

从模块:被动响应主模块发来的总线操作命令,一般是一些具备存储能力的部件

一次总线操作只能由一个主模块,但可以有多个从模块。如何响应这些主模块的使用总线的请求就是这一部分的重点,即总线管理。有两种思路:

集中式:逻辑电路集中在一起,比如集中放在 CPU 中,或者设置总线控制器

分布式:总线控制所需的逻辑电路分散在与总线连接的 各个功能部件或设备接口中,不专设总线控制器

总线仲裁

总线的管理中首先需要解决的,是多个主模块同时申请总线时的分配问题。

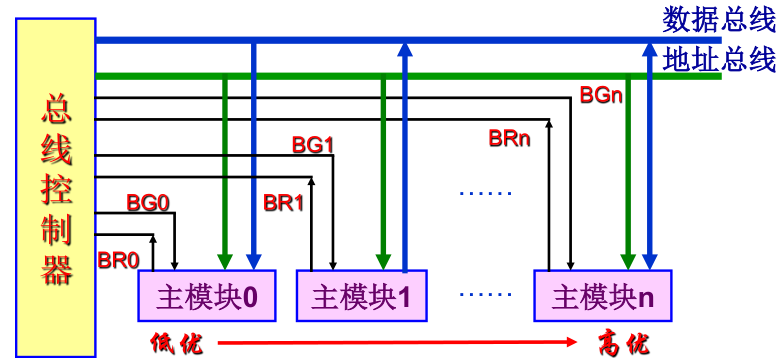

链式查询:从离总线控制器最近的主模块开始查起,离总线控制器物理连接最近的部件优先权最高

BR:Bus Request,主模块 -> 总线控制部件 发出使用请求的信号

BG:Bus Grant,总线控制部件 -> 主模块 发出同意使用的信号

BS:Bus Busy,总线控制部件 -> 主模块 发出“忙”的信号

计数器定时查询:计数器每计一次数,将计数值作为模块地址发往各个主模块。符合地址的主模块获得总线控制权,停止计数,若没有相应主模块没有请求,则计数器 +1。也就是说计数初值决定最高优先级,可以通过设置该值更改优先级

独立请求:每个主模块独立设置 BR、BG 线,通过总线控制器中的排队电路进行控制

通信方式

这部分主要解决主从模块间通信的问题,有以下四种常见的通信方式:

同步通信

完全通过时钟信号控制通信,每个总线周期中时钟个数固定,计时必须按最慢的模块、最长的举例来安排公共时钟周期时间,控制简单但灵活性差。

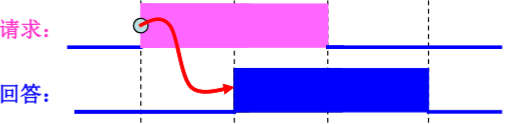

异步通信

主/从部件间有两条应答信号线,应答(握手)建立联系,个部件按照约定的信号或绝对时间使用总线:

不互锁方式:主模块自动撤销请求信号,从模块自动撤销应答信号

半互锁方式:主模块等待应答信号,从模块自动撤销应答信号

全互锁方式:主模块等待应答信号,从模块等到请求信号消失后撤销应答信号

半同步通信

同步 + 异步,以同步通信为基础,但是针对一些特别慢的部件,增加等待信号,插入等待时钟进行通信

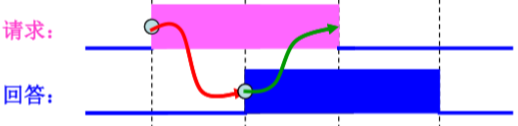

分离式通信

取消了主模块、从模块的概念,所有数据要使用总线必须申请,这样将一次总线周期分为两个子周期:

第一个子周期:模块 A 向模块 B 发送数据地址、命令、数据等信息,一旦 B 模块接收,立刻释放总线。

第二个子周期:模块 B,通过总线向模块 A 反馈数据,一旦 A 接收,立刻释放总线

可以看出,这个设计方式的好处是直接将等待过程删除掉了,模块 B 接收数据后什么时候处理好什么时候使用总线,期间总线是可以被其他模块使用的,增强了异步性

本文深入解析总线构成、工作原理、标准与特性,包括单多总线结构、总线仲裁、通信方式,以及集中式与分布式总线控制。重点讲解了总线管理中的冲突解决和通信方法,如链式查询、计数器定时查询和独立请求。

本文深入解析总线构成、工作原理、标准与特性,包括单多总线结构、总线仲裁、通信方式,以及集中式与分布式总线控制。重点讲解了总线管理中的冲突解决和通信方法,如链式查询、计数器定时查询和独立请求。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?