自集成电路器件的封装从单个组件的开发,进入到多个组件的集成后,随着产品效能的提升以及对轻薄和低耗需求的带动下,迈向封装整合的新阶段。在此发展方向的引导下,形成了电子产业上相关的两大新主流:系统单芯片SOC(System on Chip)与系统化封装SIP(System in a Package)。

以下为SOC与SIP的对比

简单来说SiP是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能,其主流封装形式是BGA。

今天来看看一些设计的比较牛逼的SIP

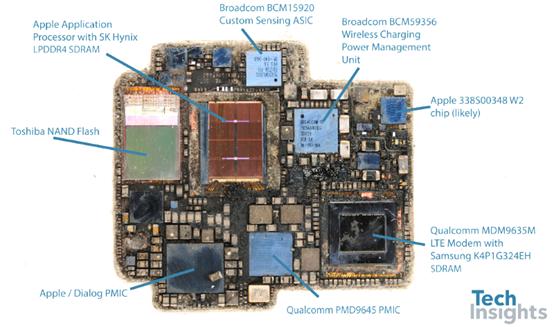

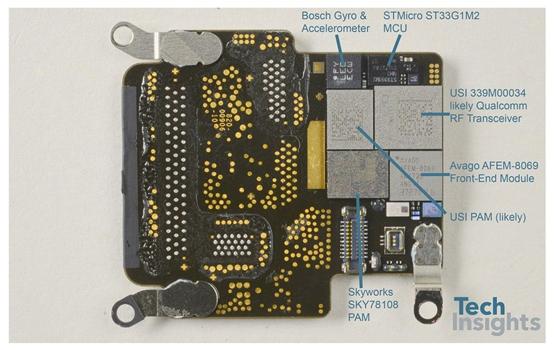

1. 先上大杀器 Apple Watch Series 3,其采用SiP设计,封装进更多的组件,挑战SiP设计极限…

Apple Watch Series 3 SiP正面

Apple Watch Series 3 SiP正面

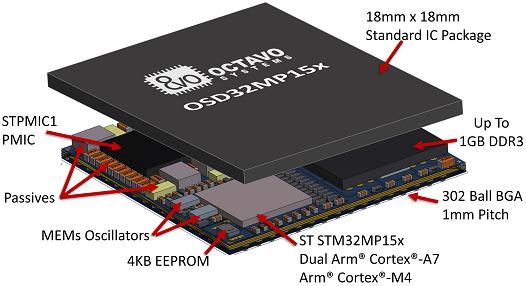

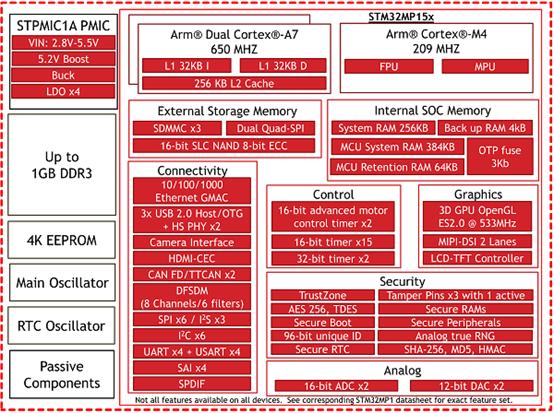

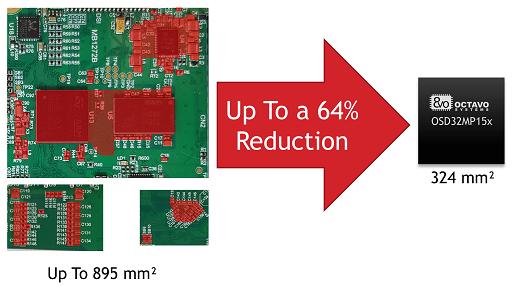

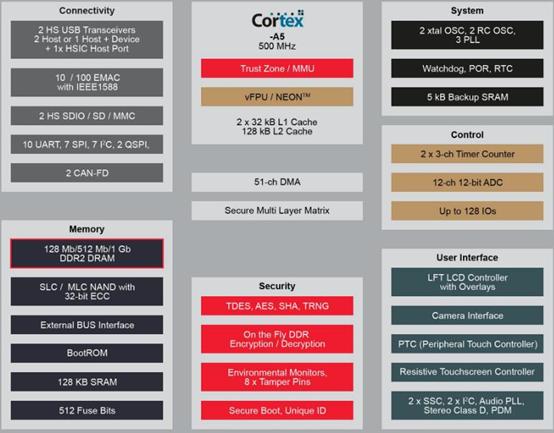

2. OSD32MP1将STM32MP1处理器与DDR存储器,电源管理,EEPROM,振荡器和无源器件集成到单个18mm X 18mm封装中,从而使其成为市场上最小的模块。它消除了使用微处理器进行设计的繁琐部分,从而使您可以将更多的时间花费在应用程序上。

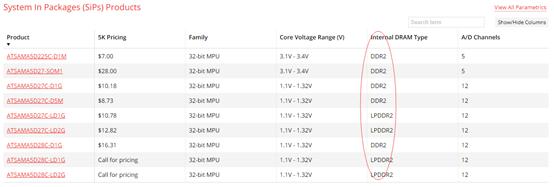

3. Microchip的MPU System in Packages (SiPs)

基于Arm®Cortex®-A5的SAMA5D2 SiP在单个封装中集成了DDR2或LPDDR2存储器(取决于设备),通过消除印刷电路板(PCB)的高速存储器接口限制,简化了设计。 阻抗匹配是在封装中完成的,而不是在开发过程中手动进行的,因此系统将在正常和低速运行下正常运行。由于其较高的系统集成水平,因此特别适合于空间受限的应用程序。

Microchip SIP仅仅集成了DDR2 or LPDDR2,还有没有更简易上手的片子or模块?当然有,下面上System on Module (SOM)

System on Module (SOM)

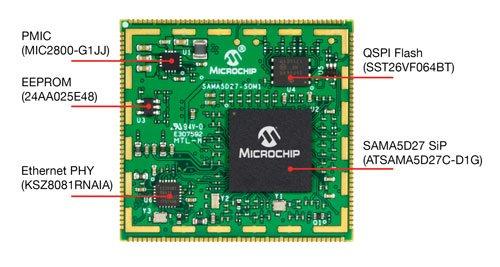

ATSAMA5D27-SOM1,其中包含了ARM ®的Cortex ® -A5 ATSAMA5D27C-D1G-CU系统级封装(SiP),极大地整合了电源管理,非易失性引导存储器,以太网PHY和高速低功耗DDR2简化了设计将存储器存储到小型单面印刷电路板(PCB)中。

有人说这个就是我们所说的核心板,对,就是这样。

4. AcSIP的S78G =SX1278 + STM32L073x + GNSS

S78G SiP(系统级封装,SEMTECH SX1278和32位超低功耗Cortex M0 + MCU(STM32L073x)集成在一起,S78G支持全球433MHz或470MHz ISM频段。能够进行双向通讯,并且可以达到16公里(10英里)的距离。此外,S78G还包含一个GPS芯片– SONY CXD5603GF,用于接收GPS / GPS + GLONASS信号进行定位。

欢迎关注公众号“嵌入式杂谈”,下载datasheet,探讨了解最新内容~

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?