作为一个科技型的博主,经常会被问到一个问题:XXX,我C盘满了,怎么办?

奈何很多人还在用360,腾讯电脑管家清理,然后清理了半天C盘就少了一两个G,下面,就告诉大家几个常用的清理方法。

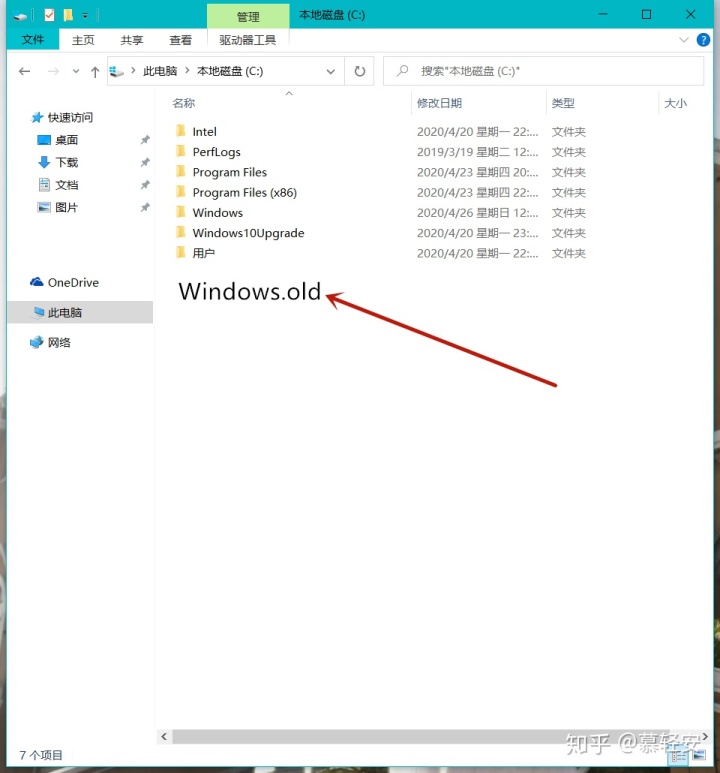

一.清理Windows.old

顾名思义,Windows.old,老旧的windows,像win7,win8升级来的,win10低版本升级到新版,都会形成这个文件夹,这个文件包含了很多之前版本win的信息,以及一些重要文件,有些用不习惯win10的用户可以通过这个文件夹逆向升级,也就是降级!

但是很多人根本就不知道,然后C盘白白多了十几个G。

由于笔者的电脑比较干净,Windows.old 文件夹早就没啦,不过,只要有这个文件夹的电脑,位置都在C盘根目录,直接删也没事,要是你是在不放心,也可以这么删。

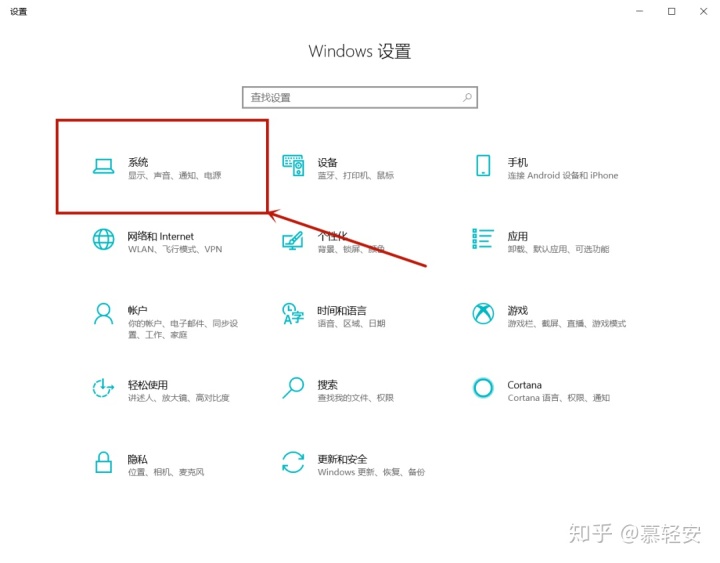

点开设置,选择系统

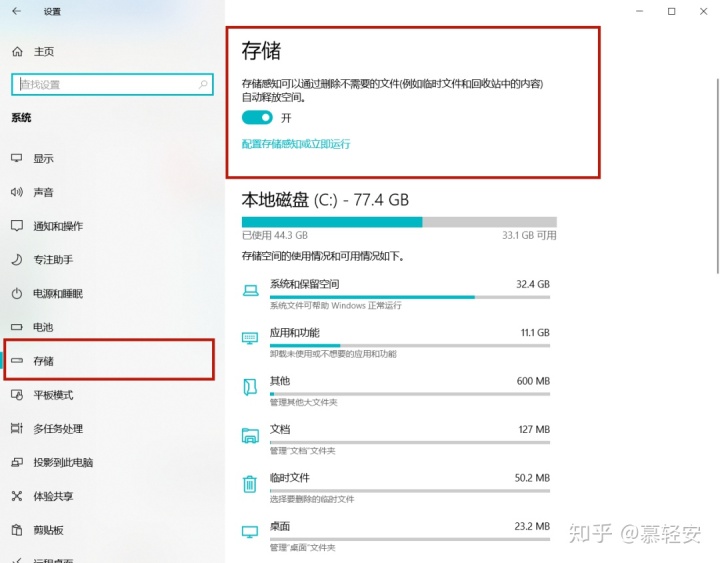

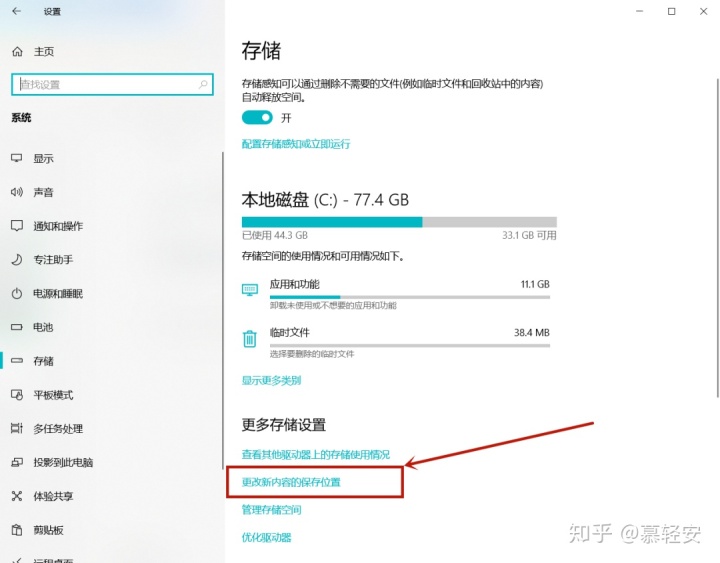

选择存储,点开开存储感知开关

点击配置存储感知或立即运行

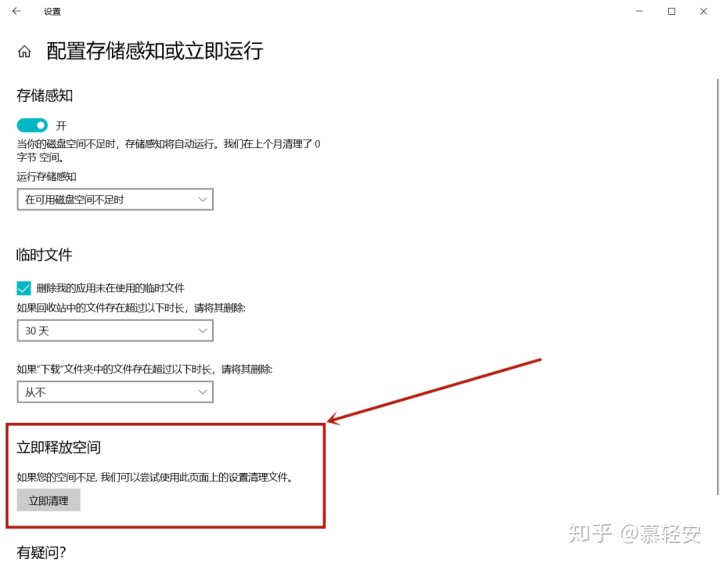

单击立即清理即可,如有删除以前版本的windows,打钩即可,就是这个文件。

二.更改系统文件夹位置

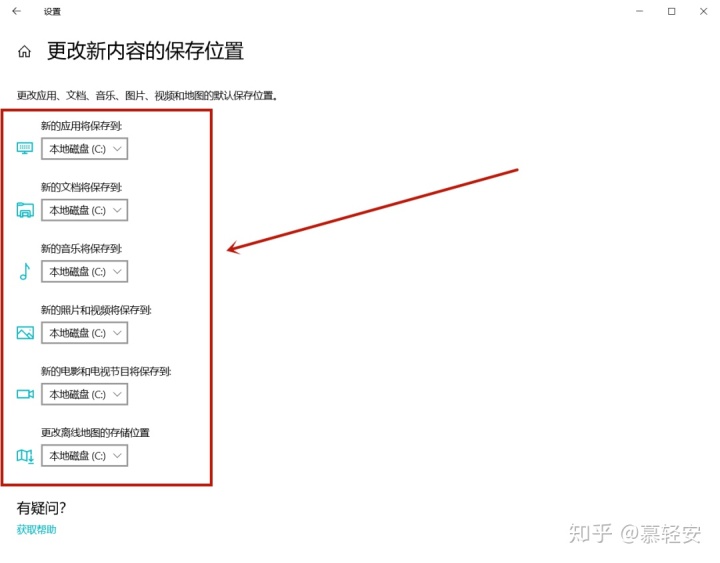

还是刚刚那个地方,选择更改新内容的保存位置

下拉菜单选择其他盘,哪个盘空选哪个

三.关闭win休眠

其实,不太推荐,但是真的有效,休眠文件是在电脑睡眠或者休眠时期保存的系统运行时的文件,小白不太推荐关闭这个功能。

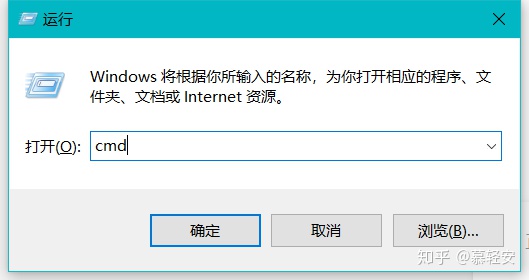

同时按住win键+R,输入cmd

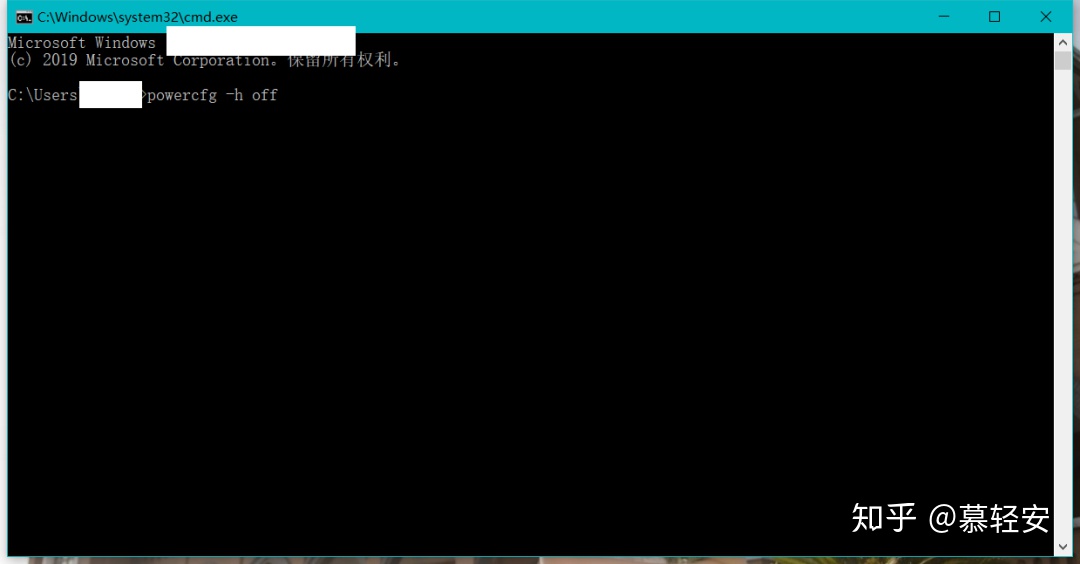

输入:powercfg -h off ,按下回车,重启,休眠文件就会被清除。

四.清理微信缓存

由于现在微信电脑版的用户很多,不得不提一下微信的缓存问题,有的一下就是几十个G,极其占用空间。

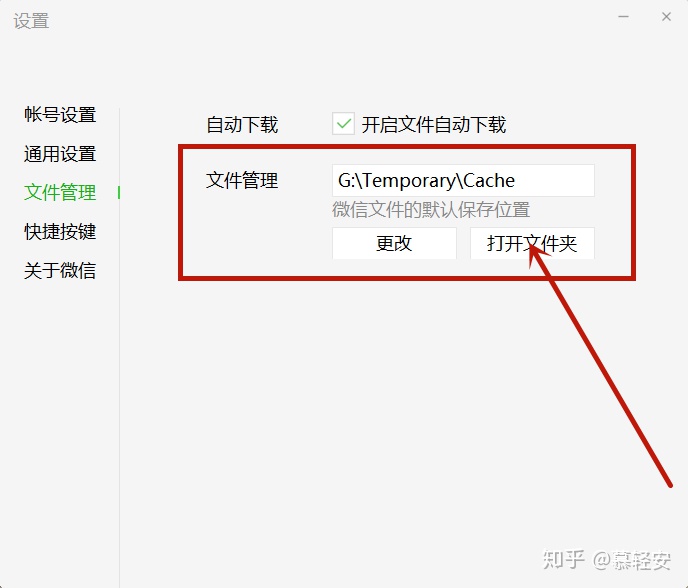

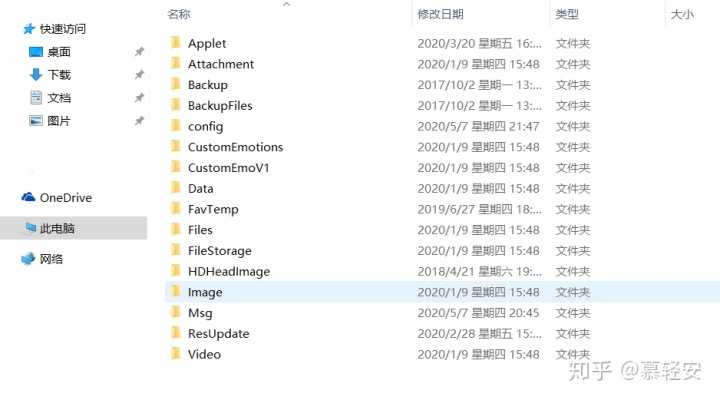

点开微信设置,选择文件管理,打开文件夹。

将文件夹里的所有文件复制到其他盘,然后选择更改,位置指向到复制的位置即可。

五.还是缓存

经常用PS,AI,AE,PR等adobe全家桶的小伙伴可能经常会碰到C盘飚红 的场景,下面以PS为例,教大家释放下C盘空间。

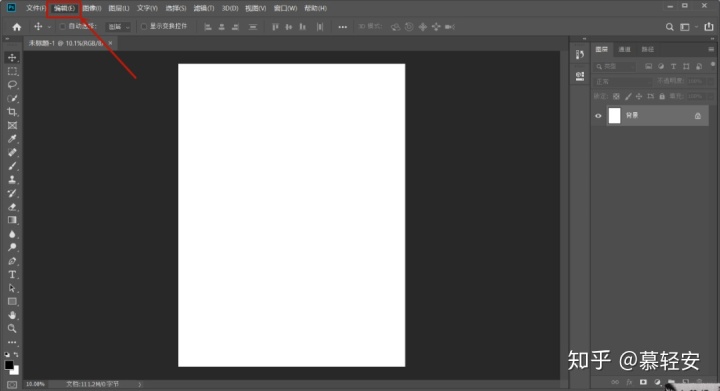

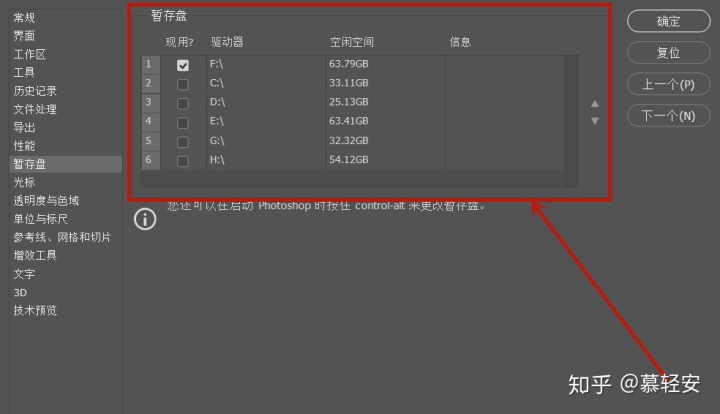

打开PS,选择编辑,点击首选项,然后选择暂存盘

选择除C盘以外的空闲盘符即可。

AI,AE,PR同理。

以上就是一些基础的清理教程,当然还有很多深度的,像清理更新缓存啊,nvidia驱动缓存啊,压缩软件缓存,虚拟内存,查找大文件等等,相对比较复杂,以上正常情况下就能给C盘清理出十几个G空间了。

如果本教程对您有帮助,请多多转发并关注 “抹茶科技” ,感谢!

【声明】部分文章和信息来源于互联网,不代表本订阅号赞同其观点和对其真实性负责。如转载内容涉及版权等问题,请立即与我们联系,我们将迅速采取适当措施

·END·

抹茶科技点亮你的科技生活

公众号 抹茶科技(matchatech),感谢关注!

1043

1043

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?