包括特殊情况直接转换, 位权相加法, 短除法, double-dabble算法.

考虑一个 N 位的 w 进制正整数 x , 令

用递归表示就是:

再考虑 x 在 k 进制表示下的分解, 和上面一样, 即:

上式用递归表示就是:

其中

而进制转换算法就是已知

特殊情况直接转换

如果 w 进制和 k 进制对正整数 n 满足

我们可以预先求出

一个 n 位的 w 进制数刚好可以表示

这里为了与

也就是说每位

位权相加法

已知

或:

短除法

由

其中

所以也能通过计算

double-dabble算法

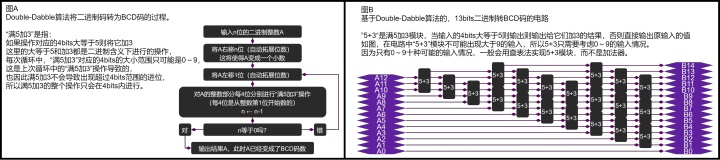

double-dabble 算法的实现可参考上图. 通常所说的 double-dabble 算法是指二进制转十进制的 double-dabble 算法 (如上图那样) , 所以下面先讨论二转十的 double-dabble 算法:

关于 double-dabble 算法, 其原理是直接在k进制下计算计算

但硬件实现上, 二转十的 double-dabble 算法使用了“逻辑左移 (所有bit左移一位) ”与“满5加3”电路模块实现 BCD 码下的

具体而言, “满5”判断的是当前十进制位

这里再讨论实现中的一些细节:

- 对一个十进制数

显然至多导致到下一位的进位, 而不会继续传递下去, 所以“满5加3”器可以每4位单独处理.

- 对于 8421BCD 码, 进行

后, 在处理进位前, 每位 8421BCD 码都应该是一个偶数, 所以每位 8421BCD 码的最低位必然是 0 .

- 如果上一位产生了进位, 只需要将其对应的最低位设置为 1 即可, 对于每次迭代引入的

, 则只需要设置到最低位的 8421BCD 码的最低位即可.

- 在整个迭代周期中, 所有“满5加3”模块显然都只可能接受 8421BCD 码的输入. 显因为然在整个算法迭代过程中,

一直都是保持以 8421BCD 码的形式表示的.

- 由于“满5加3”只可能接受 8421BCD 码的输入, 即只可能有 0~9 共 10 种输入情况. 也可以使用查表法而不是加法器来实现“满5加3”.

double-dabble 算法是显然可逆的, 二进制转十进制的 double-dabble 算法过程的逆过程就是十进制转二进制的算法 (double-dabble 算法的逆过程类似短除法) .具体而言, 就是将所有的“满5加3”模块替换为“满8减3”模块, 然后将所有模块的输入和输出对调即可.

这里我只讨论了正整数的进制转换算法, 但是小数情况其实也差不多. 另外, double-dabble算法也只讨论了二进制和十进制的情况, 但显然它可以推广到其它情况.

除此之外就是算法的时间开销, 空间开销, 电路面积开销的分析.

以后有空就把这些也写了, 这些就先留给读者吧!

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?