make命令:

make用于执行Makefile文件,用于工程中的管理,可以让新文件进行编译,而不需要将所有文件都编译。

make是以时间戳作为执行的判断条件,如果未修改则不会被执行。

Makefile文件:(必须叫makefile,大小写都可以)

目标文件:依赖文件1 依赖文件2 依赖文件3

<TAB>执行命令

Makefile文件中,多个目标文件可以使用多个上述命令编写。

注:

.PHONY:目标文件

使用这个可以强制执行指定目标文件的命令

make命令执行:

make

直接使用make将会执行Makefile文件,并且生成文件中的第一个目标。

make 目标

将会生成指定目标的内容,不涉及其他文件。多人协作工程中测试自己的文件。

在makefile文件中需要考虑目标和依赖,主要是需要生成编译后的文件,将所有编译的文件进行链接生成一个可执行的文件。

有关编译顺序的文章:ROOT-ZH:gcc编译步骤

在makefile中主要使用-c参数生成编译后的文件,文件后缀名是.o

将所有的.o的编译文件链接在一起则可以生成可执行文件。

clean:可以在makefile中加入清理功能

clean:rm *.o test -f

通过make clean 命令可以执行清理功能

如果目标目录下存在clean目录,那么使用.PHONY编写强制执行命令。

例如:

.PHONY:clean

clean:

<TAB>rm *.o test -f

Makefile中的特殊符号:(常用)

$@ 表示目标文件

$^ 表示所有的依赖文件

$< 表示第一个依赖文件

$? 表示比目标还要新的依赖文件列表

创建和使用变量:在Makefile文件中

这里的变量名更像是C语言中的宏

创建变量:

①递归展开式:变量名=变量值

②简单方式:变量名:=变量值

使用变量的值:$(变量名)

make命令参数:

-C dir 读入dir目录下的Makefile

-f file 读入file文件作为Makefile文件

-i 忽略所有执行错误命令(保证其他文件正常编译)

-n 只打印要执行的命令,但是不实际执行

其他方法:

在Makefile中创建的变量,可以将变量都放到一个文件中如config.mk。

在原始的Makefile文件中加入命令:include config.mk

隐含规则:

规则一:".o"的目标依赖文件会自动推到成".c"文件,并且其生成命令是:

$(CC) -c $(CPPFLAGS) $(CFLAGS)

规则二:"<n>"目标依赖于"<n>.o",通过C编译器来运行链接,其生成命令是:

$(CC) $(LDFLAGS) <n>.o

相当于target目标可以由target.o自动生成,target.o也可以由target.c自动生成。

但是必须要名称一致,target目标的依赖文件中必须包含target.o文件,target.o的依赖文件中也必须要由target.c文件,否则将会出现错误。

VPATH:虚路径

make在寻找源文件的时候,先在当前路径寻找,找不到就会去虚路径下面寻找。

VPATH=目录1 目录2 目录3

例如:

文件所在路径:

f1.c src1/f1.c

f2.c src2/f2.c

main.c main/main.c

VPATH=src1 src2 main

main:mian.o f1.o f2.o

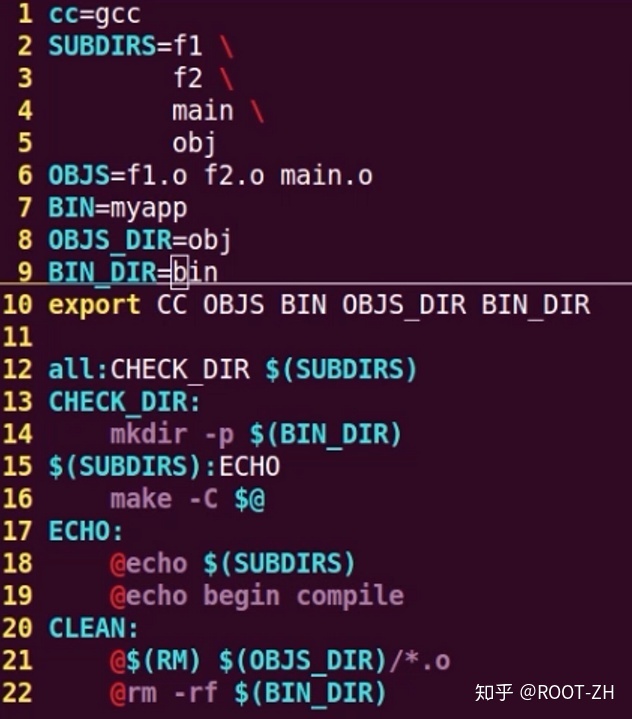

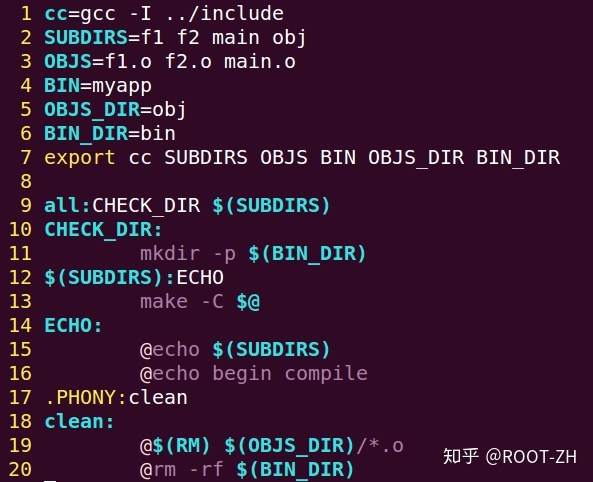

嵌套Makefile文件:(容易理解,编写困难,多多练习)

在每一个目录中写一个Makefile,通过外层的Makefile来控制和执行内部的Makefile文件。

示例:

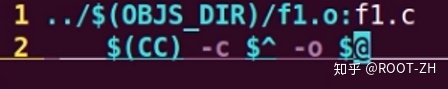

f1目录的Makefile文件:(f2,main目录都是类似的写法

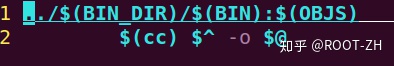

obj目录的Makefile文件:

外层的Makefile文件:

@ 符号表示不显示这个命令

make -C 表示调用指定目录下的Makefile

export 使变量可以在子Makefile中也可以使用

注:最后在个人测试中,在gcc命令后面加入了补充的命令

gcc -I ../include //此处有一个头文件写在了include文件中,需要加入编译否则报错

个人版:

181

181

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?