1)资料下载:点击资料即可下载

2)对正点原子Linux感兴趣的同学可以加群讨论:935446741

3)关注正点原子公众号,获取最新资料更新

http://weixin.qq.com/r/hEhUTLbEdesKrfIv9x2W (二维码自动识别)

本章,我们将向大家介绍探索者 STM32F4 开发板的网口及其使用。本章,我们将使用

ALIENTEK 探索者 STM32F4 开发板自带的网口和 LWIP 实现:TCP 服务器、TCP 客服端、UDP

以及 WEB 服务器等四个功能。本章分为如下几个部分:

60.1 STM32F4 以太网以及 TCP/IP LWIP 简介

60.2 硬件设计

60.3 软件设计

60.4 下载验证

60.1 STM32F4 以太网以及 TCP/IP LWIP 简介

本章,我们需要用到 STM32F4 的以太网控制器和 LWIP TCP/IP 协议栈。接下来分别介绍

这两个部分。

60.1.1 STM32F4 以太网简介

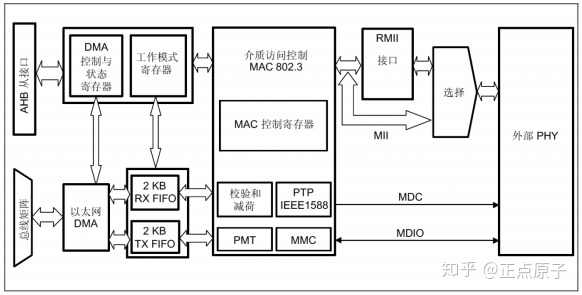

STM32F407 芯片自带以太网模块,该模块包括带专用 DMA 控制器的 MAC 802.3(介质访

问控制)控制器,支持介质独立接口 (MII) 和简化介质独立接口 (RMII),并自带了一个用于

外部 PHY 通信的 SMI 接口,通过一组配置寄存器,用户可以为 MAC 控制器和 DMA 控制器选

择所需模式和功能。

STM32F4 自带以太网模块特点包括:

➢ 支持外部 PHY 接口,实现 10M/100Mbit/s 的数据传输速率

➢ 通过符合 IEEE802.3 的 MII/RMII 接口与外部以太网 PHY 进行通信

➢ 支持全双工和半双工操作

➢ 可编程帧长度,支持高达 16KB 巨型帧

➢ 可编程帧间隔(40~96 位时间,以 8 为步长)

➢ 支持多种灵活的地址过滤模式

➢ 通过 SMI(MDIO)接口配置和管理 PHY 设备

➢ 支持以太网时间戳(参见 IEEE1588-2008),提供 64 位时间戳

➢ 提供接收和发送两组 FIFO。

➢ 支持 DMA

STM32F4 以太网功能框图如图 60.1.1.1 所示:

从上图可以看出,STM32F4 是必须外接 PHY 芯片,才可以完成以太网通信的,外部 PHY

芯片可以通过 MII/RMII 接口与 STM32F4 内部 MAC 连接,并且支持 SMI(MDIO&MDC)接 口配置外部以太网 PHY 芯片。

接下来分别介绍 SMI/MII/RMII 接口和外部 PHY 芯片。

SMI 接口,即站管理接口,该接口允许应用程序通过 2 条线:时钟(MDC)和数据线(MDIO)

访问任意 PHY 寄存器。该接口支持访问多达 32 个 PHY,应用程序可以从 32 个 PHY 中选择

一个 PHY,然后从任意 PHY 包含的 32 个寄存器中选择一个寄存器,发送控制数据或接收状态 信息。任意给定时间内只能对一个 PHY 中的一个寄存器进行寻址。

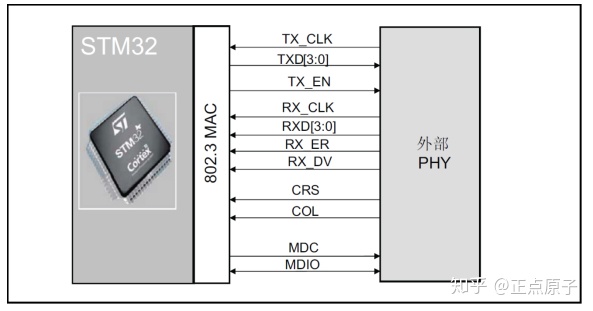

MII 接口,即介质独立接口,用于 MAC 层与 PHY 层进行数据传输。STM32F407 通过 MII

与 PHY 层芯片的连接如图 60.1.1.2 所示。

⚫ MII_TX_CLK:连续时钟信号。该信号提供进行 TX 数据传输时的参考时序。标称频率为:

速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz。

⚫ MII_RX_CLK:连续时钟信号。该信号提供进行 RX 数据传输时的参考时序。标称频率为:

速率为 10 Mbit/s 时为 2.5 MHz;速率为 100 Mbit/s 时为 25 MHz。

⚫ MII_TX_EN:发送使能信号。

⚫ MII_TXD[3:0]:数据发送信号。该信号是 4 个一组的数据信号,

⚫ MII_CRS:载波侦听信号。

⚫ MII_COL:冲突检测信号。

⚫ MII_RXD[3:0]:数据接收信号。该信号是 4 个一组的数据信号

⚫ MII_RX_DV:接收数据有效信号。

⚫ MII_RX_ER:接收错误信号。该信号必须保持一个或多个周期(MII_RX_CLK),从而向 MAC

子层指示在帧的某处检测到错误。

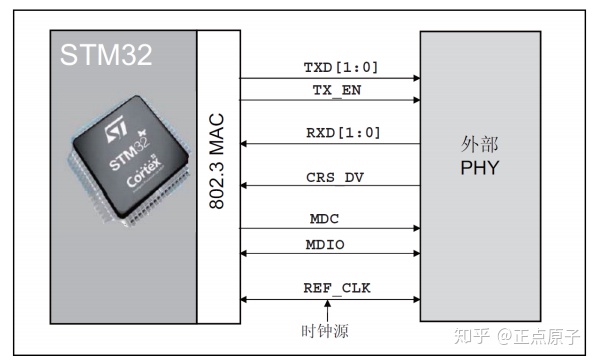

RMII 接口,即精简介质独立接口,该接口降低了在 10/100 Mbit/s 下微控制器以太网外设与

外部 PHY 间的引脚数。根据 IEEE 802.3u 标准,MII 包括 16 个数据和控制信号的引脚。RMII

规范将引脚数减少为 7 个。

RMII 接口是 MAC 和 PHY 之间的实例化对象。这有助于将 MAC 的 MII 转换为 RMII。

RMII 具有以下特性:

1,支持 10Mbit/s 和 100Mbit/s 的运行速率

2,参考时钟必须是 50 MHz

3,相同的参考时钟必须从外部提供给 MAC 和外部以太网 PHY

4,它提供了独立的 2 位宽(双位)的发送和接收数据路径

STM32F407 通过 RMII 接口与 PHY 层芯片的连接如图 60.1.1.3 所示:

从上图可以看出 RMII 相比 MII,引脚数量精简了不少。注意,图中的 REF_CLK 信号,是 RMII 和外部 PHY 共用的 50Mhz 参考时钟,必须由外部提供,比如有源晶振,或者 STM32F4 的 MCO 输出。不过有些 PHY 芯片可以自己产生 50Mhz 参考时钟,同时提供给 STM32F4,这 样也是可以的。

本章我们采用 RMII 接口和外部 PHY 芯片连接,实现网络通信功能,探索者 STM32F4 开发

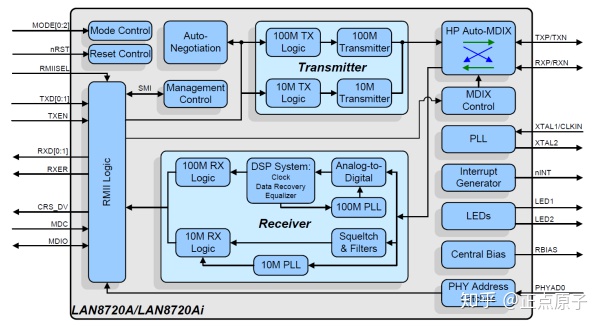

板使用的是 LAN8720A 作为 PHY 芯片。接下来,我们简单介绍一下 LAN8720A 这个芯片。

LAN8720A 是低功耗的 10/100M 以太网 PHY 层芯片,I/O 引脚电压符合 IEEE802.3-2005 标

准,支持通过 RMII 接口与以太网 MAC 层通信,内置 10-BASE-T/100BASE-TX 全双工传输模

块,支持 10Mbps 和 100Mbps。

LAN8720A 可以通过自协商的方式与目的主机最佳的连接方式(速度和双工模式),支持 HP

Auto-MDIX 自动翻转功能,无需更换网线即可将连接更改为直连或交叉连接。LAN8720A 的主

要特点如下:

⚫ 高性能的 10/100M 以太网传输模块

⚫ 支持 RMII 接口以减少引脚数

⚫ 支持全双工和半双工模式

⚫ 两个状态 LED 输出

⚫ 可以使用 25M 晶振以降低成本

⚫ 支持自协商模式

⚫ 支持 HP Auto-MDIX 自动翻转功能

⚫ 支持 SMI 串行管理接口

⚫ 支持 MAC 接口

LAN8720A 功能框图如图 60.1.1.4 所示。

LAN8720A 的应脚数是比较少的,因此,很多引脚具有多个功能。这里,我们介绍几个重

要的设置。

1,PHY 芯片地址设置

LAN8720A 可以通过 PHYAD0 引脚来配置,该引脚与 RXER 引脚复用,芯片内部自带下

拉电阻,当硬复位结束后,LAN8720A 会读取该引脚电平,作为器件的 SMI 地址,接下拉电阻

时(浮空也可以,因为芯片内部自带了下拉电阻),设置 SMI 地址为 0,当外接上拉电阻后,

可以设置为 1。本章我们采用的是该引脚浮空,即设置 LAN8720 地址为 0。

2,nINT/REFCLKO 引脚功能配置

<

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?