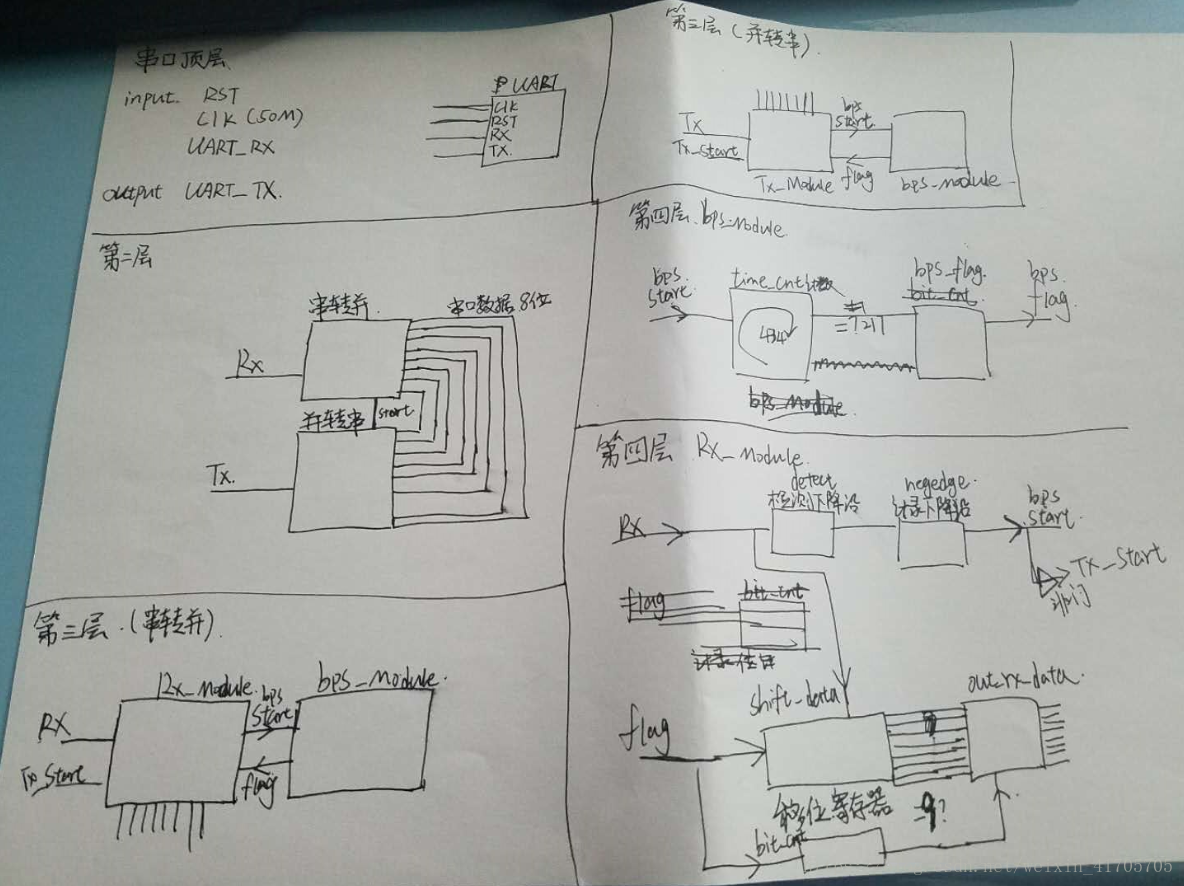

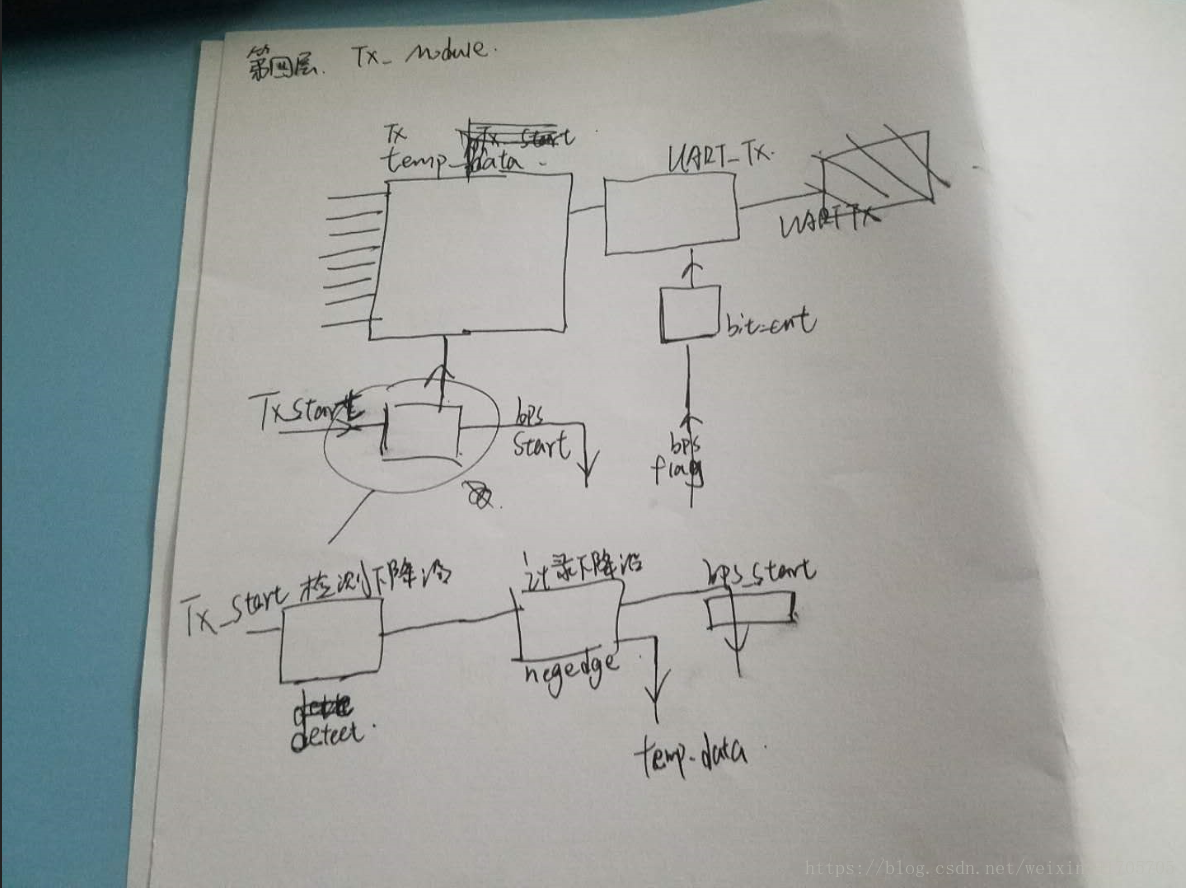

1.根据功能需要设计模块,自上而下不断细化,确定端口、子模块、连线,最好就是画图出来,这里是设计的是把收到的串口数据重新发送出去

2.根据自己画的图,转换成verilo代码,并描述出来

//---------------------------------------------------------------------------

//-- 文件名 : Uart_Test_Top.v

//-- 作者 : LIZIYI

//-- 描述 : 串口收发测试顶层文件

//-- 修订历史 : 2018-7-23

//---------------------------------------------------------------------------

module Uart_Test

(

//输入端口

RST,CLK,UART_RX,

//输出端口

UART_TX

);

//---------------------------------------------------------------------------

//-- 外部端口声明

//---------------------------------------------------------------------------

input RST; //复位

input CLK; //时钟50M

input UART_RX; //串口接收

output UART_TX; //串口发送

//---------------------------------------------------------------------------

//-- 内部端口声明

//---------------------------------------------------------------------------

wire [7:0] data; //八位数据线

wire tx_start; //串口发送标志

wire rx_bps_start; //Rx波特率启动

wire rx_bps_flag; //Rx读取标志

wire tx_bps_start; //Tx波特率启动

wire tx_bps_flag; //Tx读取标志

//---------------------------------------------------------------------------

//-- 逻辑功能实现

//---------------------------------------------------------------------------

//例化RX波特率模块

Bps_Module Rx_Bps_Module_Init

(

.CLK (CLK),

.RST (RST),

.bps_start (rx_bps_start),

.bps_flag (rx_bps_flag)

);

//例化TX波特率模块

Bps_Module Tx_Bps_Module_Init

(

.CLK (CLK),

.RST (RST),

.bps_start (tx_bps_start),

.bps_flag (tx_bps_flag)

);

//例化Rx模块

Rx_Module Rx_Module_Init

(

.CLK (CLK),

.RST (RST),

.UART_RX (UART_RX),

.rx_bps_start (rx_bps_start),

.rx_bps_flag (rx_bps_flag),

.tx_start (tx_start),

.out_rx_data (data)

);

//例化Tx模块

Tx_Module Tx_Module_Init

(

.CLK (CLK),

.RST (RST),

.UART_TX (UART_TX),

.tx_bps_start (tx_bps_start),

.tx_bps_flag (tx_bps_flag),

.tx_start (tx_start),

.out_tx_data (data)

);

endmodule

//---------------------

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?