在之前对于同步计数器的设计中, 我从未验证过输出Y对于下一位(较高位)计数器的影响. 之前对于计数器的输出Y值的设定就有一定的疑惑, 今日终于有了更进一步的理解. 我们通过同步十进制加法计数器和同步六进制加法计数器的有机组合来看一下这其中的奥妙.

对于同步十进制加法计数器的设计, 我们都知道在1001->0000时, Y由0->1: 那么问题来了, 究竟是电路状态为1001时Y=1还是电路状态为0000时Y=1呢——我的课本上告诉我是1001. 可真正将该结论应用到实际中时, 我发现, 这是错误的: 若按书上的思路来, 电路状态来到08后, 会变到19, 而后再变为10(这很显然是不对的); 电路状态在18、28、38、48、58时都会面临这一问题.

根据出现的问题, 我将同步十进制加法计数器部分的输出Y改为Y=Q3n'Q2n'Q1n'Q0n', 再模拟电路波形后发现, 上述问题已不存在. 吸取了这一教训后, 我又将同步六进制加法计数器部分的输出Y改为Y=Q2n'Q1n'Q0n'.

当然, 我也只是用multisim7模拟了电路的运行情况, 并不是真正意义上的运行, 所以我的结论有可能不完全正确, 还请各位朋友帮我分析这一问题, 在这向提供宝贵意见的朋友们表示衷心的感谢!

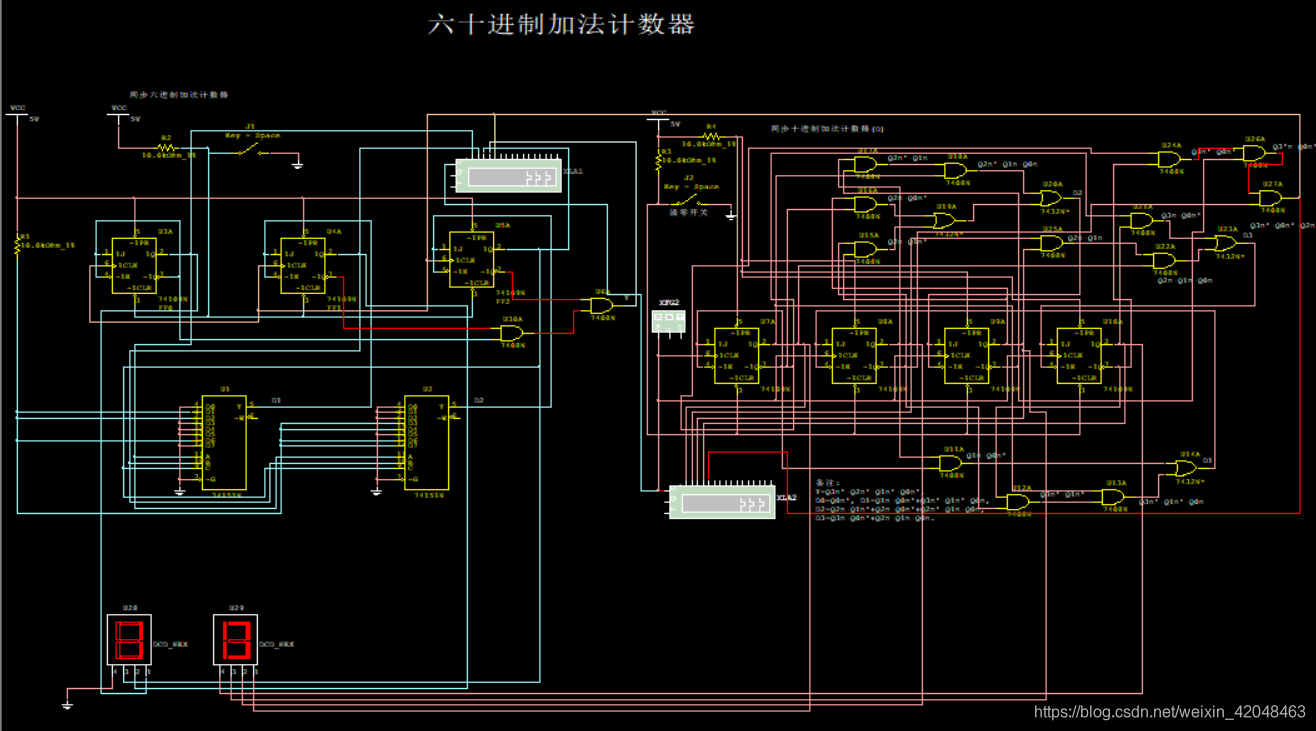

最后, 我们来看一下该如何有机组合这两个电路.

(1)准备好统一使用上升沿触发的D触发器构成的同步十进制加法计数电路,

(2)准备好统一使用上升沿触发的D触发器构成的同步六进制加法计数电路,

(3)将信号发生器的输出端接到每个同步十进制加法计数电路中的D触发器的CLK端,

(4)将同步十进制加法计数电路的输出Y接到每个同步六进制加法计数电路中的D触发器的CLK端,

(5)用两个4输入数码管, 实时显示两个电路的状态.

由于电路版图过大, 下面只展示电路图的缩略版本, 若想获取更加详细的电路图, 可从本博客的资源中找到该电路的详细设计过程及电路逻辑图.

3992

3992

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?