题目给出的逻辑表达式只涉及2个变量(A、B), 而要求我们使用3变量输入的3-8译码器74LS138来实现, 所以我们须先将2变量(A、B)的逻辑表达式等价转换为3变量(A、B、C)的逻辑表达式.

Y1(A,B)=∑m(0,3)=A'B'+AB=A'B'(C+C')+AB(C+C')=A'B'C+A'B'C'+ABC+ABC',

Y2(A,B)=∑m(1,2,3)=A'B+AB'+AB=A'B(C+C')+AB'(C+C')+AB(C+C')=A'BC+A'BC'+AB'C+AB'C'+ABC+ABC',

将Y1、Y2转换为3变量的逻辑函数, 有:

Y1(A,B,C)=A'B'C+A'B'C'+ABC+ABC',

Y2(A,B,C)=A'BC+A'BC'+AB'C+AB'C'+ABC+ABC',

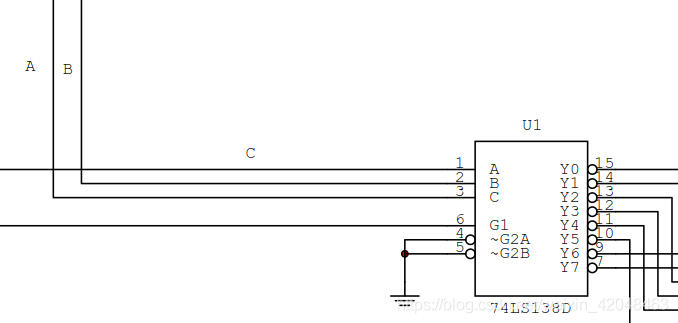

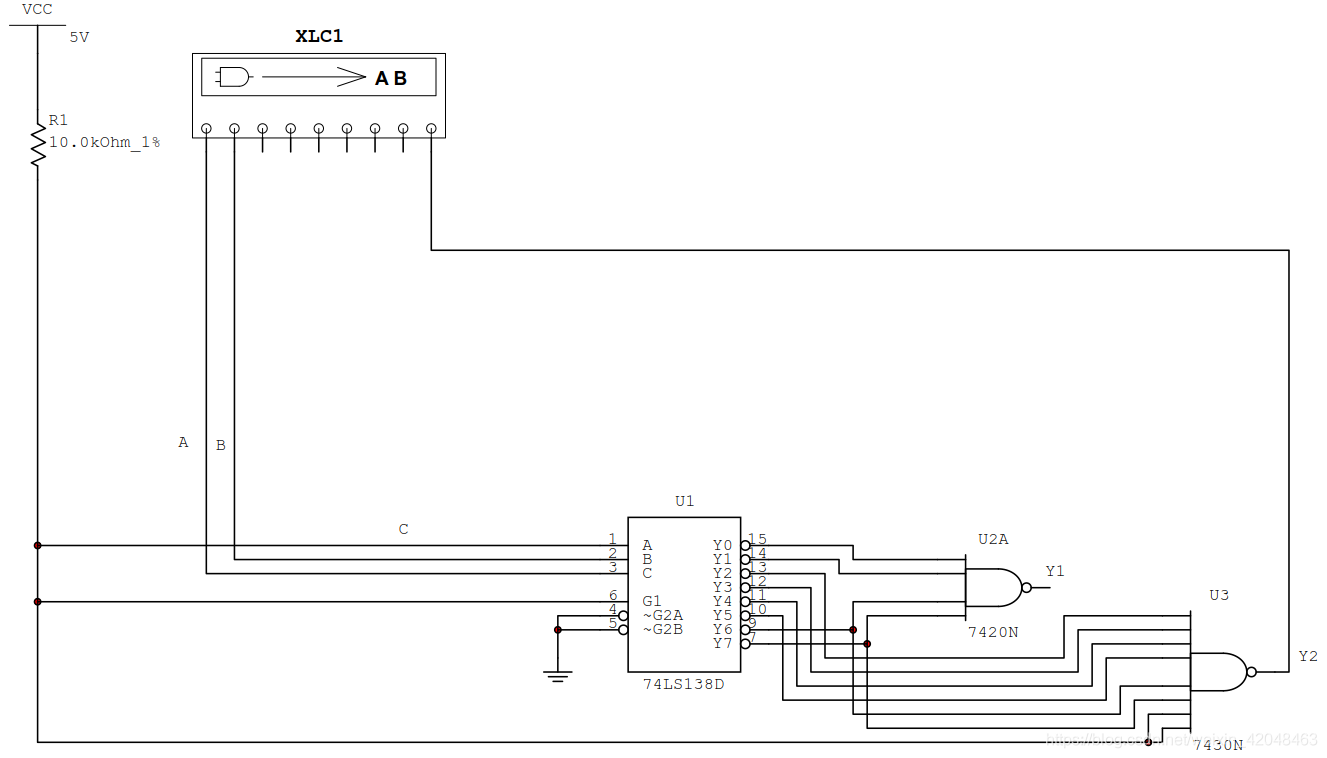

要使Y1(A,B,C)、Y2(A,B,C)分别与Y1(A,B)、Y2(A,B)等价, 则使C=1(或C=0). 按照下图示接线:

Y1(A,B,C)=A'B'C+A'B'C'+ABC+ABC'=∑m(0,1,6,7)=m0+m1+m6+m7=((m0+m1+m6+m7)')'=(m0'·m1'·m6'·m7')'=(Y0'·Y1'·Y6'·Y7')'.

Y2(A,B,C)=A'BC+A'BC'+AB'C+AB'C'+ABC+ABC'=∑m(2,3,4,5,6,7)=m2+m3+m4+m5+m6+m7=((m2+m3+m4+m5+m6+m7)')'=(m2'·m3'·m4'·m5'·m6'·m7')'=(Y2'·Y3'·Y4'·Y5'·Y6'·Y7')'.

由Y1(A,B,C)=(Y0'·Y1'·Y6'·Y7')', Y2(A,B,C)=(Y2'·Y3'·Y4'·Y5'·Y6'·Y7')', 得到电路原理图:

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?