使用Block Memory进行PS和PL的数据交互或者数据共享,通过zynq PS端的Master GP0端口向BRAM写数据,然后再通过PS端的Mater GP1把数据读出来,将结果打印输出到串口终端显示。

涉及到AXI BRAM Controller 和 Block Memery Generator等IP的使用。

本文所使用的开发板是zedboard

PC 开发环境版本:Vivado 2016.2 Xilinx SDK 2016.2

---------------------

作者:wangdaling

来源:CSDN

原文:https://blog.csdn.net/rzjmpb/article/details/50365915 https://blog.csdn.net/rzjmpb/article/details/50365915

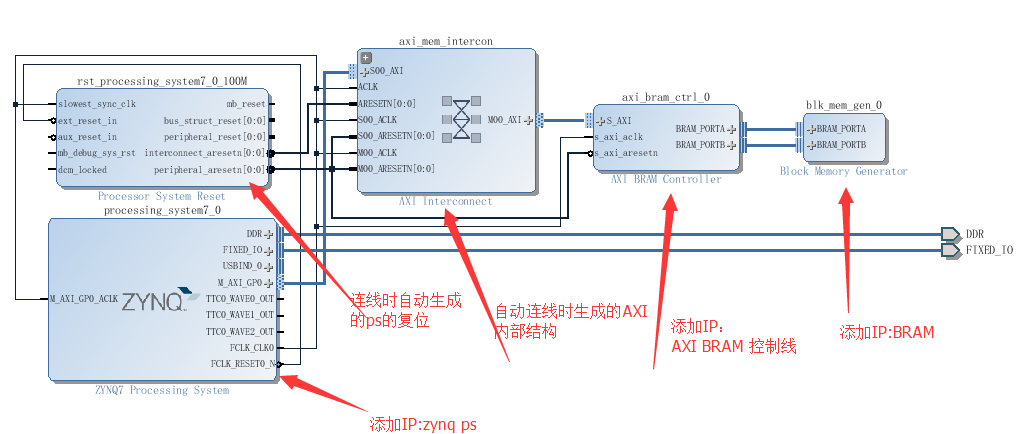

一、实现的结构原理图

1、PL端硬件架构搭建

新建工程后在Create Block Design中添加IP,点击添加IP的按钮后在弹出的搜索框中搜索ZYNQ时添加PS,搜索BRAM时添加AXI BRAM Controller 和Block Memory Generator,然后对PS中的相应接口做参数设置

本文详细介绍了如何在Linux环境下,利用Zynq的PS(Processing System)通过Master GP0和GP1端口与PL(Programmable Logic)进行数据交互,具体操作包括配置AXI BRAM Controller和Block Memory Generator IP,编写并编译SDK代码,以及在Zedboard上进行程序部署和FPGA编程。通过示例代码展示了数据写入BRAM并读取的过程。

本文详细介绍了如何在Linux环境下,利用Zynq的PS(Processing System)通过Master GP0和GP1端口与PL(Programmable Logic)进行数据交互,具体操作包括配置AXI BRAM Controller和Block Memory Generator IP,编写并编译SDK代码,以及在Zedboard上进行程序部署和FPGA编程。通过示例代码展示了数据写入BRAM并读取的过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?