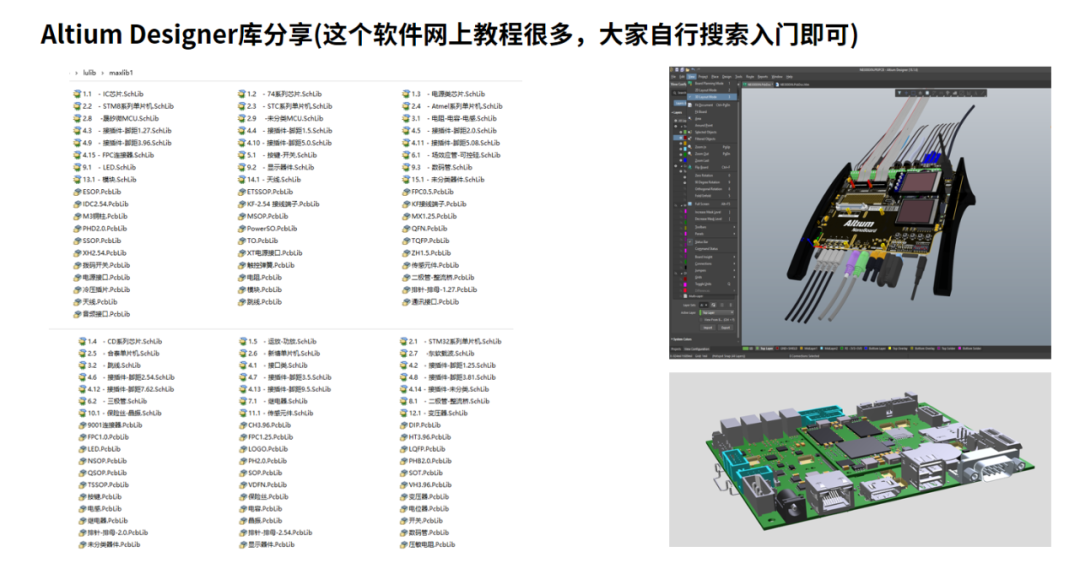

简介:Altium Designer是一款集原理图设计、PCB布局、3D建模、仿真分析与嵌入式开发于一体的电子设计自动化(EDA)工具。本学习资料压缩包内容全面,涵盖从基础操作到高级功能的使用技巧,包含原理图绘制、电气规则检查、元件封装库管理、PCB布线优化、设计规则检查、3D建模、电路仿真、项目管理与嵌入式系统开发等内容。通过实例教程与案例解析,帮助学习者掌握Altium Designer的全流程设计能力,提升硬件开发效率与质量。

1. Altium Designer软件概述与界面操作

Altium Designer 是一款集成化的电子设计自动化(EDA)工具,广泛应用于原理图设计、PCB布局与仿真分析等领域。其发展历程从Protel时代至今,逐步整合了3D PCB设计、信号完整性分析等功能,成为现代电子产品开发的核心平台之一。

1.1 软件安装与配置

安装Altium Designer需确保系统满足最低配置要求,建议使用Windows 10 64位操作系统,16GB以上内存及SSD硬盘。安装包可从Altium官网下载,运行安装程序后选择“自定义安装”以选择所需组件,如FPGA开发、仿真模块等。

安装完成后,首次启动时需激活许可证。可通过Altium账户登录或选择离线激活方式。建议同时配置工作空间路径,设置默认的项目存储位置与库路径,以提升后续工作效率。

1.2 主界面与工具栏功能解析

Altium Designer主界面由菜单栏、工具栏、项目面板、工作区面板及状态栏组成。菜单栏提供文件管理、编辑、视图等核心操作入口;工具栏则集合了常用命令按钮,如新建项目、保存、编译等。

工作区默认打开“开始”页面,提供新建项目、打开已有项目、访问示例工程等功能。通过【File】>【New】>【Project】可创建新项目,并选择原理图或PCB项目类型。

以下是一个新建PCB项目的操作流程示例:

File → New → Project → PCB Project → 保存为"MyFirstProject.PrjPcb"

项目创建后,右键项目面板选择【Add New to Project】>【Schematic】可添加原理图文件,进行后续设计。

1.3 项目管理与基础操作流程

Altium Designer采用项目管理模式,一个项目可包含多个原理图、PCB文件、库文件等资源。项目文件(.PrjPcb)用于组织和管理这些设计文件,并支持编译与错误检查。

基础设计流程如下:

- 创建项目并添加原理图文件;

- 在原理图中放置元器件并完成电气连接;

- 执行电气规则检查(ERC);

- 编译项目并生成网络表;

- 创建PCB文件并导入网络表;

- 进行元件布局与布线;

- 完成DRC检查并输出制造文件。

通过这一流程,用户可以系统性地完成从电路设计到PCB实现的全过程,为后续章节的学习打下坚实基础。

2. 原理图设计流程与ERC检查

2.1 原理图设计的前期准备

2.1.1 电路功能分析与元器件选型

在开始绘制原理图之前,首要任务是进行电路功能分析。这一阶段的核心是明确电路的预期功能,包括信号路径、电源管理、接口协议等。设计师需要与系统工程师、硬件工程师密切沟通,确保理解每一部分电路的需求。

在完成功能分析后,进入元器件选型阶段。选型需要考虑以下几个方面:

| 考虑因素 | 说明 |

|---|---|

| 性能参数 | 如电压、电流、频率、精度等 |

| 封装形式 | 与PCB设计兼容的封装,如SOP、QFN、BGA等 |

| 供货稳定性 | 优先选择市场主流、供货稳定的型号 |

| 成本控制 | 控制整体BOM成本,考虑批量采购价格 |

| 可替代性 | 是否有PIN兼容的替代型号,以备后期替换 |

例如,若设计一个5V转3.3V的稳压电路,选型可能如下:

// 示例代码:稳压器选型参考

#include <stdio.h>

int main() {

char* regulator_model = "LM1117-3.3";

float input_voltage = 5.0;

float output_voltage = 3.3;

float max_current = 0.8; // 单位:A

printf("选用稳压芯片:%s\n", regulator_model);

printf("输入电压范围:%.1fV\n", input_voltage);

printf("输出电压:%.1fV\n", output_voltage);

printf("最大输出电流:%.1fA\n", max_current);

return 0;

}

逻辑分析与参数说明:

-

regulator_model:指定选用的稳压芯片型号; -

input_voltage:输入电压为5V,符合典型USB供电标准; -

output_voltage:输出稳定在3.3V,适用于大多数MCU和数字电路; -

max_current:最大输出电流0.8A,适用于中等功耗系统; - 该代码模拟了选型过程,实际中需参考数据手册、供应商信息和设计需求进行综合判断。

选型完成后,应建立元器件清单(BOM),并将其与原理图设计流程进行同步,确保设计与采购环节一致。

2.1.2 设计文档与技术指标确认

在正式绘制原理图前,必须完成详细的设计文档编写与技术指标确认。这包括:

- 功能需求说明书 :描述电路的功能、接口、性能预期;

- 系统框图 :展示各模块之间的连接关系;

- 电气性能指标 :如电压精度、输出电流、工作温度范围等;

- 设计约束条件 :如PCB尺寸、功耗限制、EMC/EMI要求等;

- 测试验证计划 :初步定义测试点、测试方法和验收标准。

文档确认过程应由项目负责人组织多方评审,确保设计目标清晰、无歧义。这一阶段的输出将作为原理图设计的指导性文件。

2.2 原理图绘制技巧

2.2.1 元件放置与连线规范

良好的原理图绘制习惯对于后期PCB设计和调试至关重要。元件放置应遵循以下原则:

- 功能模块化布局 :将电路划分为若干功能模块,如电源、主控、接口、传感器等;

- 信号流向清晰 :从输入到输出,从左到右或从上到下排列;

- 避免交叉连接 :尽量减少导线交叉,使用跳线或网络标签替代;

- 对齐与间距统一 :使用Altium Designer的对齐工具,保持整齐美观;

- 标注清晰 :每个元件应标注清晰的符号、型号和值,便于阅读和后续BOM生成。

示例:绘制一个ADC采样电路

U1

Part: ADC0804

Value: 8-bit ADC

Pin 1: VCC

Pin 2: GND

Pin 3: Vin

Pin 4: CS

Pin 5: RD

Pin 6: WR

Pin 7: INTR

Pin 8: D0-D7 (数据输出)

逻辑分析与参数说明:

-

ADC0804:8位模数转换器,常用于嵌入式系统中; -

Vin:输入模拟电压,需接入待测信号; -

CS、RD、WR:控制信号,用于与MCU通信; -

INTR:中断输出,表示转换完成; - 数据输出引脚D0-D7应连接至MCU的并行接口;

- 原理图中应添加电源去耦电容,如100nF陶瓷电容靠近VCC引脚。

2.2.2 总线与网络标签的使用

Altium Designer支持使用总线(Bus)和网络标签(Net Label)来简化复杂电路的连接关系。使用技巧如下:

- 总线 :适用于多条信号线,如地址总线、数据总线等;

- 网络标签 :用于标识相同的网络,避免长线连接;

- 层次化设计 :通过Sheet Symbol和Sheet Entry实现多层原理图连接。

使用网络标签的示例:

Net Label: VCC

Connected to: U1.VCC, C1.1, R1.1

Net Label: GND

Connected to: U1.GND, C1.2, R1.2

逻辑分析与参数说明:

-

VCC和GND是常见的电源网络标签; - 所有连接到该网络的元件引脚都应标注相同的标签;

- 网络标签的使用可以减少重复连线,提高可读性和后期修改效率;

- 在ERC检查中,未连接的网络标签会被识别为错误,便于及时修复。

2.2.3 层次化设计方法

层次化设计是将一个复杂系统拆分为多个子系统,通过Sheet Symbol进行调用和连接的设计方式。其优势包括:

- 结构清晰 :便于团队协作与版本控制;

- 易于维护 :修改某一模块不影响其他部分;

- 可复用性强 :相同功能模块可重复使用。

层次化设计流程:

- 创建顶层原理图(Top Sheet);

- 添加Sheet Symbol作为模块占位符;

- 为每个Sheet Symbol创建子原理图(Child Sheet);

- 使用Sheet Entry定义输入输出端口;

- 编译项目,检查连接关系。

示例:使用层次化设计绘制一个电源管理模块

graph TD

A[Top Sheet] --> B[Sheet Symbol: Power Module]

A --> C[Sheet Symbol: MCU Module]

A --> D[Sheet Symbol: Communication Module]

B --> E[Child Sheet: Power Management]

C --> F[Child Sheet: STM32F103 Control]

D --> G[Child Sheet: UART to USB]

流程图说明:

- 顶层原理图包含三个模块:电源、主控、通信;

- 每个模块通过Sheet Symbol调用子原理图;

- 子原理图中定义具体的电路结构和接口;

- Sheet Entry用于定义模块之间的连接关系;

- 层次化设计使得原理图结构清晰、易于管理。

2.3 电气规则检查(ERC)

2.3.1 ERC检查设置与规则配置

电气规则检查(Electrical Rule Check, ERC)是Altium Designer提供的自动检查工具,用于发现原理图中的电气错误。启用ERC的步骤如下:

- 打开原理图项目;

- 点击菜单栏“Project” -> “Validate PCB Project”;

- 在“Project Options”中设置ERC规则;

- 查看Messages面板中的错误和警告信息。

常见ERC规则配置参数:

| 规则类别 | 描述 | 示例 |

|---|---|---|

| Unconnected Pins | 检查是否有未连接的引脚 | 某个电源引脚未连接 |

| Floating Nets | 检查是否有悬空网络 | 未接地的模拟输入 |

| Power Nets | 检查电源网络连接 | 未连接到电源的VCC |

| Duplicate Nets | 检查重复网络标签 | 两个相同名称的网络 |

| Sheet Entry Connections | 检查层次化连接 | 子图未正确连接到顶层 |

示例配置代码:

[ERC]

UnconnectedPins=Warning

FloatingNets=Error

PowerNets=Error

DuplicateNets=Error

SheetEntryConnections=Error

逻辑分析与参数说明:

-

UnconnectedPins:设置为Warning,便于后期排查; -

FloatingNets:设置为Error,悬空网络可能导致电路异常; -

PowerNets:设置为Error,电源网络必须连接; -

DuplicateNets:设置为Error,避免命名冲突; -

SheetEntryConnections:设置为Error,确保层次化连接正确。

2.3.2 常见电气错误类型及修复方法

在ERC检查过程中,常见的错误类型包括:

| 错误类型 | 描述 | 修复方法 |

|---|---|---|

| Unconnected Pin | 引脚未连接 | 检查是否遗漏连接或是否需要保留悬空 |

| Floating Net | 网络未连接 | 添加上拉/下拉电阻,或连接至地或电源 |

| Duplicate Net Label | 网络标签重复 | 修改标签名称,确保唯一性 |

| No Net Assigned | 未分配网络 | 为引脚或导线分配正确的网络标签 |

| Mismatched Sheet Entry | 层次化连接不匹配 | 检查子图Sheet Entry与父图连接是否一致 |

示例修复过程:

假设ERC报告某ADC芯片的VREF引脚未连接:

U1.ADC0804.VREF -> [Unconnected Pin]

解决方法:

- 查看数据手册,确认是否需要外部参考电压;

- 若需要,添加一个10kΩ上拉电阻连接至VCC;

- 若不需要,可添加一个“no ERC”标记,避免误报。

R1

Part: RES

Value: 10k

Pin 1: U1.VREF

Pin 2: VCC

2.3.3 ERC报告解读与优化建议

ERC检查完成后,Altium Designer会生成一份详细的报告,列出所有错误和警告。理解并正确处理这些信息是确保原理图正确性的关键。

典型ERC报告内容:

| 类型 | 严重性 | 描述 | 位置 |

|---|---|---|---|

| Error | High | 悬空网络:ADC_IN未连接 | Sheet1.U1.Pin3 |

| Warning | Medium | 未连接引脚:U2.GPIO未使用 | Sheet2.U2.Pin10 |

| Error | High | 重复网络标签:VCC出现在两个Sheet中 | Sheet1.NetLabel1 |

优化建议:

- 逐项修复错误 :优先处理Error级别的问题;

- 忽略合理警告 :如某些引脚确实不需要连接;

- 统一网络命名 :避免不同Sheet中网络标签冲突;

- 定期执行ERC :在每次修改后重新验证;

- 使用“Comment”标注原因 :便于后期维护人员理解。

示例优化流程:

graph LR

A[完成原理图绘制] --> B[执行ERC检查]

B --> C{是否有错误?}

C -->|是| D[定位错误位置]

D --> E[分析错误原因]

E --> F[修复错误]

F --> G[重新验证ERC]

C -->|否| H[原理图验证通过]

流程图说明:

- 每次绘制完成后都应执行ERC检查;

- 如果存在错误,定位并分析原因;

- 根据错误类型采取修复措施;

- 修复完成后重新验证,确保无遗留问题;

- 通过流程化管理,提升原理图质量与可靠性。

3. 元器件库管理与封装制作

在Altium Designer中,元器件库的管理与封装制作是电子设计流程中的关键环节。一个结构清晰、内容完整的元器件库不仅能提升设计效率,还能显著减少因封装错误导致的设计返工。本章将从元器件库的整体架构出发,深入讲解集成库与分离库的使用场景与管理流程,并逐步引导读者掌握如何创建自定义原理图符号与PCB封装,以及如何有效管理元器件参数信息与供应链数据。

3.1 元器件库的结构与管理

Altium Designer支持多种类型的元器件库格式,包括集成库(Integrated Library)、分离库(如原理图符号库、PCB封装库)等。不同的库结构适用于不同规模和复杂度的设计项目,理解它们的组成结构和管理方式,有助于提升元器件调用的灵活性与一致性。

3.1.1 集成库与分离库的比较

在Altium Designer中,元器件库可以分为 集成库 (.IntLib)和 分离库 (如.SchLib、.PcbLib)。两者在结构和使用方式上有显著区别。

| 特性 | 集成库(.IntLib) | 分离库(.SchLib + .PcbLib) |

|---|---|---|

| 结构 | 单一文件包含原理图符号与PCB封装 | 多文件结构,分别存储符号与封装 |

| 管理 | 所有元器件集中管理,便于版本控制 | 分开管理,便于协作与维护 |

| 编辑性 | 无法直接编辑,需反编译后修改 | 可直接编辑,便于快速修改 |

| 适用范围 | 中小型项目或封装固定不变的元器件 | 大型项目、团队协作、频繁修改封装 |

| 性能 | 调用速度快,适合稳定库 | 需加载多个文件,性能略低 |

示例:创建集成库

要创建集成库,需先准备好原理图符号库(.SchLib)和PCB封装库(.PcbLib),然后通过Altium Designer的集成库编译功能将其合并。

// 在Altium Designer中创建集成库

1. 打开原理图符号库和PCB封装库

2. 点击“文件” -> “新建” -> “项目” -> “集成库”

3. 在项目中添加已有的.SchLib和.PcbLib文件

4. 右键点击项目 -> “Compile Integrated Library”

逻辑分析与参数说明:

- 第1步 :确保每个元器件的Symbol与Footprint名称一致,以保证集成成功。

- 第2~4步 :编译后会生成一个.IntLib文件,该文件可直接导入到其他设计项目中使用。

- 注意事项 :集成库一旦生成,不能直接修改,需回到原始分离库中修改后重新编译。

3.1.2 库文件的创建与更新流程

无论是集成库还是分离库,良好的库管理流程对于长期项目至关重要。以下是一个标准的库文件创建与更新流程:

graph TD

A[创建原理图符号] --> B[创建PCB封装]

B --> C[绑定符号与封装]

C --> D[保存为分离库]

D --> E{是否需要集成库?}

E -->|是| F[编译生成.IntLib]

E -->|否| G[直接导入项目使用]

F --> H[版本管理与更新]

G --> H

流程图说明:

- 从创建符号开始,逐步完成封装绑定,最终根据需求决定是否生成集成库。

- 所有库文件应统一命名规范,并设置版本控制机制(如Git或SVN),以确保多人协作时的版本一致性。

示例:更新库文件并同步到项目

// 更新分离库中的某个封装

1. 打开.PcbLib文件

2. 修改所需元器件的封装尺寸或焊盘位置

3. 保存更改

4. 回到项目中,右键点击元器件 -> "Update PCB from Schematics"

逻辑分析与参数说明:

- 第1~3步 :封装修改完成后,必须在项目中执行更新操作,以确保PCB中的封装与库保持一致。

- 第4步 :此操作将更新所有引用该封装的元器件,避免因封装不一致导致的制造错误。

3.2 原理图符号与PCB封装设计

元器件的电气连接信息和物理尺寸信息分别由原理图符号和PCB封装承载。因此,正确地创建和管理这两个部分是确保电路功能与PCB物理实现一致的关键。

3.2.1 创建自定义原理图符号

原理图符号用于表示元器件的电气连接关系,创建时应遵循一定的命名规范与图形设计标准。

示例:创建一个4引脚电阻的原理图符号

1. 打开.SchLib文件

2. 点击"工具" -> "新元器件"

3. 输入元器件名称,如"R_4P"

4. 在工作区绘制矩形代表电阻本体

5. 添加4个引脚(Pin),并设置Pin编号为1~4

6. 设置引脚电气类型为"Passive"

7. 保存元器件

逻辑分析与参数说明:

- 第3步 :元器件名称建议与PCB封装名称一致,便于后期绑定。

- 第5步 :引脚编号应与PCB封装焊盘编号一一对应,确保连接正确。

- 第6步 :电气类型用于后续ERC检查,Passive表示为被动元件。

3.2.2 PCB封装设计规范与尺寸标注

PCB封装定义了元器件在PCB上的物理尺寸与焊盘布局,设计时需参考厂商提供的数据手册,确保封装尺寸与实际元器件一致。

示例:创建一个0805贴片电阻封装

1. 打开.PcbLib文件

2. 点击"工具" -> "新元器件"

3. 输入封装名称,如"RES_0805"

4. 使用"Top Layer"绘制元器件外框

5. 添加两个焊盘,编号为1和2,尺寸为0.9mm x 1.0mm

6. 设置焊盘间距为2.0mm

7. 保存封装

逻辑分析与参数说明:

- 第5步 :焊盘尺寸应根据数据手册推荐值设置,避免焊接不良。

- 第6步 :焊盘间距必须精确,否则可能导致元器件无法正确贴装。

graph LR

A[元器件手册] --> B[确定焊盘尺寸与间距]

B --> C[绘制Top Layer外框]

C --> D[放置焊盘并编号]

D --> E[保存为.PcbLib组件]

流程图说明:

- 从数据手册获取物理参数,依次完成封装设计流程,确保封装准确性。

3.2.3 焊盘与引脚的匹配设置

在Altium Designer中,原理图符号的引脚(Pin)必须与PCB封装的焊盘(Pad)一一对应,否则在导入PCB时会出现“未匹配引脚”错误。

示例:绑定原理图符号与PCB封装

1. 打开.SchLib文件

2. 右键点击元器件 -> "描述"

3. 在"模型"选项卡中点击"添加"

4. 类型选择"PCB封装"

5. 浏览并选择对应的.PcbLib文件和封装名称

6. 确认引脚与焊盘编号一致

逻辑分析与参数说明:

- 第3~5步 :绑定模型后,元器件在导入PCB时将自动调用该封装。

- 第6步 :若引脚编号与焊盘编号不一致,需手动调整或修改封装,否则导入后会出现电气连接错误。

3.3 元器件信息管理

元器件的参数信息不仅影响设计的可读性和后续制造流程,还对供应链管理、BOM生成等环节至关重要。Altium Designer提供了丰富的属性字段和导出功能,便于工程师对元器件进行统一管理。

3.3.1 元器件参数填写与属性管理

Altium Designer允许在元器件属性中添加多个自定义参数,如制造商、型号、价格、库存等,这些参数可在BOM中导出。

示例:为元器件添加自定义参数

1. 打开.SchLib文件

2. 编辑元器件属性

3. 点击"参数"选项卡

4. 点击"添加",输入参数名称如"Manufacturer"

5. 填写参数值,如"Vishay"

6. 保存元器件

逻辑分析与参数说明:

- 第4~5步 :参数名称应统一命名规范,如Manufacturer、PartNumber、Supplier等。

- 第6步 :所有参数信息在生成BOM时可直接导出,便于供应链管理。

3.3.2 导出BOM与供应链数据整合

Altium Designer支持将设计中的元器件信息导出为Excel或CSV格式的BOM表,并可与供应链系统集成。

示例:导出BOM表

1. 打开原理图或PCB文件

2. 点击“报告” -> “Bill of Materials”

3. 在弹出窗口中选择需要导出的字段

4. 点击“导出”按钮,保存为Excel文件

逻辑分析与参数说明:

- 第3步 :建议导出字段包括元器件名称、数量、封装、制造商、型号、价格等。

- 第4步 :导出的BOM可用于采购、生产、成本核算等业务流程。

示例:BOM表格样例

| 元件编号 | 名称 | 数量 | 封装 | 制造商 | 型号 | 价格(元) |

|---|---|---|---|---|---|---|

| R1 | 电阻 | 1 | RES_0805 | Vishay | CRCW080510K | 0.15 |

| C1 | 电容 | 1 | CAP_0603 | Murata | GRM188R71H | 0.22 |

表格说明:

- 上表为典型BOM导出格式,包含关键供应链信息。

- 通过字段匹配,可将该BOM导入ERP或MES系统,实现自动化采购与库存管理。

graph LR

A[设计完成] --> B[导出BOM]

B --> C[上传至ERP系统]

C --> D[采购下单]

D --> E[生产排程]

流程图说明:

- 设计完成后,BOM信息可无缝对接企业资源计划系统,提升整体项目执行效率。

4. PCB布局与自动/手动布线技巧

PCB(Printed Circuit Board,印刷电路板)设计是电子产品研发过程中的关键环节,直接影响电路性能、信号完整性、热管理和可制造性。本章将从PCB设计的前期准备入手,深入讲解PCB布局策略、自动布线与手动优化技巧,帮助读者掌握从原理图到PCB设计的完整流程,提升设计效率和质量。

4.1 PCB设计前期准备

在正式开始PCB布局与布线之前,必须完成一系列前期准备工作,确保原理图与PCB的一致性,并合理设置板框和层结构。这部分内容是整个PCB设计流程的基石,任何疏漏都可能导致后续布线失败或功能异常。

4.1.1 原理图与PCB的同步更新

在Altium Designer中,原理图(Schematic)与PCB之间的同步更新是通过“工程变更订单”(ECO,Engineering Change Order)机制实现的。以下是一个标准的同步更新流程:

1. 打开项目并确保原理图与PCB文件处于打开状态。

2. 在原理图界面点击菜单栏的【Design】→【Update PCB Document】。

3. 系统会弹出“Engineering Change Order”对话框,显示所有需要同步的变更。

4. 点击【Validate Changes】进行校验,确认无误后点击【Execute Changes】执行更新。

5. 完成后关闭对话框,返回PCB编辑器查看同步结果。

逻辑分析 :

该流程确保了原理图中元器件的添加、删除、属性修改能够准确无误地反映在PCB上。

- Validate Changes :用于检查是否存在冲突或错误,如引脚未连接、封装缺失等。

- Execute Changes :执行实际更新操作,将变更写入PCB数据库。注意事项 :

- 原理图中元器件必须已指定正确的PCB封装。

- 若存在未分配封装的元件,ECO会报错并提示用户补充。

4.1.2 板框定义与层结构设置

Altium Designer支持灵活的板框定义和层结构配置,适用于多层PCB设计。以下是板框定义与层结构设置的操作步骤:

板框定义流程:

1. 在PCB编辑器中选择【Design】→【Board Shape】→【Define from Selected Objects】。

2. 在机械层(Mechanical Layer)绘制闭合轮廓,作为PCB外形。

3. 选择该轮廓,执行定义命令,系统将自动生成板框。

层结构设置流程:

1. 点击菜单栏【Design】→【Layer Stack Manager】打开层栈管理器。

2. 点击【Add Layer】或【Add Plane】添加信号层或电源/地层。

3. 设置每层的材料、厚度、介电常数等参数。

4. 配置层名称、类型(Signal、Power、Mixed等)以及是否为盲埋孔层。

5. 完成设置后点击【Apply】保存并关闭。

参数说明 :

- Layer Type :信号层(Signal)、电源层(Power)、混合层(Mixed)。

- Material :板材类型,如FR4、Rogers等,影响信号完整性分析。

- Dielectric :介质厚度,影响阻抗匹配计算。

- Blind/Buried Vias :是否启用盲孔/埋孔,适用于高密度设计。

| 层类型 | 用途说明 | 典型应用场景 |

|---|---|---|

| Signal | 信号走线层 | 高速信号传输、数据线 |

| Power | 电源层 | 为整个系统提供稳定电压 |

| Mixed | 混合层(电源+信号) | 成本敏感型设计 |

| Plane | 地层 | 降低噪声、提高EMI性能 |

技巧提示 :

- 对于四层板,通常采用Top Layer(信号)、Power Plane、GND Plane、Bottom Layer(信号)的结构。

- 使用完整的地平面可显著改善信号完整性,降低串扰和电磁干扰。

4.2 PCB布局策略

PCB布局是决定电路性能和可制造性的关键阶段,合理的布局可以减少布线难度、提升散热效果,并增强抗干扰能力。本节将从核心元件优先布局、模拟与数字分区、热管理与机械安装三个方面详细阐述。

4.2.1 核心元件优先布局原则

在布局阶段,应优先放置对电路功能起关键作用的核心元件,如:

- 微控制器(MCU)

- 电源模块(如DC-DC、LDO)

- 高速接口芯片(如USB、Ethernet)

- 晶振与时钟发生器

布局建议 :

- 将MCU置于PCB中心区域,便于与其他外围器件连接。

- 电源模块靠近输入端口,避免长线走线带来的压降和噪声。

- 高速信号相关元件应集中布局,减少走线长度。

- 晶振应紧贴MCU放置,并远离大电流和高噪声元件。

流程示例 :

1. 使用Altium的【Component Placement】工具拖动元件到合适位置。

2. 按F键可快速旋转元件。

3. 使用【Align】工具对齐多个元件,保持整齐布局。

IF component_type == "MCU"

PLACE at center of board

ELSE IF component_type == "Power"

PLACE near power input

ELSE IF component_type == "Clock"

PLACE close to MCU

END IF

逻辑分析 :

上述伪代码模拟了核心元件布局的基本逻辑,实际中应结合电路功能和布线路径进行综合判断。

4.2.2 模拟与数字电路分区布局

混合信号PCB中,模拟电路和数字电路应进行物理分区,以减少噪声耦合和串扰。

分区原则:

| 区域 | 电路类型 | 设计建议 |

|---|---|---|

| 模拟区 | ADC、DAC、传感器、放大器 | 使用独立地平面或单点接地 |

| 数字区 | MCU、FPGA、存储器 | 高速信号集中,远离敏感模拟电路 |

| 接口区 | USB、Ethernet、RS485等 | 靠近连接器,布线短而直 |

布局策略流程图(mermaid):

graph TD

A[开始布局] --> B{是否存在模拟电路?}

B -- 是 --> C[划分模拟区与数字区]

B -- 否 --> D[统一布局]

C --> E[模拟元件优先布局]

C --> F[数字元件分区布局]

E --> G[模拟地与数字地单点连接]

F --> H[高速信号集中处理]

G --> I[完成分区布局]

H --> I

注意事项 :

- 模拟地与数字地应在一点连接,通常选择电源入口处。

- 模拟电路附近避免走高速数字信号线。

4.2.3 热管理和机械安装考虑

在高功率或高密度设计中,热管理是布局阶段必须考虑的因素。

热管理布局策略:

- 高功率元件(如MOSFET、稳压器)应放置在通风良好、便于散热的位置。

- 多个发热元件应均匀分布,避免局部过热。

- 可使用大面积铜箔、散热孔(Thermal Via)辅助散热。

- 使用Altium的【PCB Panel】→【Nets】查看电源网络,优化走线宽度。

机械安装考虑:

- 安装孔(Mounting Holes)应避开高密度布线区域。

- 连接器、开关、指示灯等外部接口应靠近板边,便于插拔。

- 散热器或风扇应预留安装空间,避免与元件干涉。

参数说明 :

- 走线宽度计算公式(基于IPC-2221):

$$

W = \frac{I}{k \cdot \Delta T^{0.44}}

$$

其中:

- $ W $:走线宽度(mm)

- $ I $:电流(A)

- $ k $:常数,内层取0.024,外层取0.048

- $ \Delta T $:允许温升(℃)

4.3 自动布线与手动优化

在完成PCB布局后,进入布线阶段。Altium Designer提供强大的自动布线器(Auto Router)和丰富的手动布线工具,本节将讲解自动布线器的使用方法、手动优化技巧以及差分对与高速信号布线方法。

4.3.1 自动布线器的使用与参数设置

Altium的自动布线器(ActiveRoute或Route → Auto Route)可根据预设规则自动完成大部分走线任务,适用于中低密度设计。

启用自动布线步骤:

1. 打开PCB编辑器,点击菜单栏【Route】→【Auto Route】→【All】。

2. 弹出自动布线设置对话框,选择布线策略(如Length Minimization、High-Speed Optimization等)。

3. 设置最大布线层数、布线方向(Horizontal/Vertical)、过孔使用规则等。

4. 点击【Route】开始自动布线。

参数说明 :

- Routing Strategy :布线策略,影响布线优先级和路径选择。

- Max Layers :最大布线层数,影响布线密度。

- Routing Grid :布线网格,影响布线精度。

- Via Usage :控制是否允许使用过孔,以及过孔类型。

自动布线优缺点分析:

| 优点 | 缺点 |

|---|---|

| 快速完成基础布线 | 布线路径可能不够优化 |

| 节省手动布线时间 | 高速信号路径可能不符合要求 |

| 适用于简单电路 | 对复杂电路需手动干预 |

技巧提示 :

- 在布线前先设置好布线规则(Design → Rules),包括线宽、间距、层分配等。

- 使用“Route All”前建议先使用“Route Selected”测试部分网络。

4.3.2 手动调整与布线规则应用

自动布线完成后,通常需要手动调整以优化布线质量和信号完整性。

手动布线基本操作:

1. 选择布线工具(快捷键Ctrl + W)。

2. 单击一个焊盘开始布线,按Shift + Space切换布线模式(90°、45°、任意角度)。

3. 按Tab键可修改当前线宽、层、过孔等属性。

4. 使用【Interactive Routing】工具进行差分对布线。

5. 使用【Reroute】工具重新布线已有网络。

布线规则设置(Design → Rules)示例 :

| 规则类别 | 规则名称 | 设置值 | 说明 |

|---|---|---|---|

| Electrical | Clearance | 0.2mm | 最小线间距 |

| Routing | Width | 0.254mm | 默认线宽 |

| Routing | Layer Assignment | Top & Bottom | 布线层设置 |

| High Speed | Matched Net Lengths | ±0.1mm | 差分对长度匹配 |

手动布线技巧:

- 使用Shift + Space切换布线角度,保持布线整洁。

- 按住Shift并单击可选择多个网络同时布线。

- 使用【Place → Via】手动添加过孔,控制过孔位置和类型。

- 对高频信号线使用“Trombone Tuning”进行长度匹配。

4.3.3 差分对与高速信号布线技巧

在高速PCB设计中,差分对布线至关重要,直接影响信号完整性和抗干扰能力。

差分对布线规则设置:

1. 在PCB面板中选择【Nets】,右键选择要设置为差分对的网络。

2. 选择【Create Differential Pair】,输入正负网络名称。

3. 在【Design】→【Rules】→【High Speed】中设置差分对规则:

- Differential Pairs Routing

- Matched Net Lengths

- Parallel Segment

差分对布线技巧:

- 差分线应保持等长、等距,避免交叉和绕行。

- 尽量减少过孔使用,若必须使用,应在两线间对称添加。

- 使用Altium的交互式布线工具(Interactive Routing)进行差分对布线。

- 使用【Trombone Tuning】工具自动调整线长。

高速信号布线流程图(mermaid):

graph TD

A[开始布线] --> B{是否为差分信号?}

B -- 是 --> C[设置差分对规则]

B -- 否 --> D[普通信号布线]

C --> E[使用交互式布线工具]

D --> F[使用快捷键布线]

E --> G[应用Trombone Tuning调整长度]

F --> H[设置线宽与间距规则]

G --> I[完成高速信号布线]

H --> I

参数说明 :

- 差分线间距 :一般为线宽的2~3倍。

- 线长匹配误差 :高速接口(如USB 3.0、HDMI)要求误差小于±0.1mm。

- 过孔数量控制 :每对差分线过孔数应尽量一致。

本章系统讲解了PCB设计的前期准备、布局策略与布线技巧,涵盖了从原理图同步到自动/手动布线的完整流程,并通过代码、表格和流程图等方式增强了理解深度。通过掌握本章内容,读者将能够高效、规范地完成复杂PCB设计任务。

5. 电源与接地网络优化设计

在高速电路和复杂系统设计中,电源与接地网络的设计直接关系到系统的稳定性、信号完整性以及电磁兼容性(EMC)。本章将深入探讨Altium Designer中电源和接地网络的优化设计策略,帮助工程师构建低噪声、高稳定性的电路系统。

5.1 电源网络设计原则

电源网络的设计不仅仅是将电源引到各个器件,更是对整个系统能量传输路径的规划。良好的电源设计可以显著提升电路的稳定性和抗干扰能力。

5.1.1 电源层与地层的规划与分配

在多层PCB设计中,通常将完整的铜层用于电源(Power Plane)和地(Ground Plane)。使用电源层有以下优势:

- 低阻抗路径 :大面积铜箔降低电源阻抗,减少电压降和噪声。

- 散热性能好 :有助于器件的热管理。

- 电磁干扰(EMI)抑制 :地层作为参考平面,可减少高速信号的辐射干扰。

在Altium Designer中设置电源层的操作步骤如下:

1. 打开PCB编辑器,进入【Design】 > 【Layer Stack Manager】。

2. 点击【Add Layer】添加新的电源层。

3. 设置层类型为【Power Plane】,选择合适的层名称(如3.3V、5V等)。

4. 在【Properties】中设置该层的默认网络(如GND或VCC)。

5. 使用【Place】 > 【Polygon Pour】绘制电源区域,关联到指定网络。

5.1.2 电源完整性(PI)分析基础

电源完整性(Power Integrity, PI)分析旨在确保电源网络在所有工作频率下提供稳定的电压,并抑制噪声和瞬态干扰。Altium Designer支持通过集成的仿真工具进行初步的PI分析。

关键参数包括:

| 参数 | 描述 |

|---|---|

| PDN阻抗 | 目标是保持在一定频率范围内低于目标阻抗 |

| 去耦电容分布 | 合理布局去耦电容以降低高频噪声 |

| 电源纹波 | 电压波动应在允许范围内 |

在Altium中进行PI分析可通过以下流程图表示:

graph TD

A[准备电源网络布局] --> B[设置去耦电容模型]

B --> C[启动Signal Integrity分析器]

C --> D[选择电源网络进行仿真]

D --> E[查看PDN阻抗曲线]

E --> F[优化去耦方案]

5.2 接地系统设计与优化

接地系统是整个电路的参考电位,其设计直接影响信号完整性和抗干扰能力。

5.2.1 接地方式与噪声抑制

常见的接地方式包括:

- 单点接地 :适用于低频电路,避免形成地环路。

- 多点接地 :适用于高频电路,减少地阻抗。

- 混合接地 :结合单点与多点,适用于混合信号系统。

在Altium Designer中,建议使用 地平面(Ground Plane) 来实现多点接地,以降低高频噪声。例如:

// 示例:在PCB中定义地平面

Polygon Pour {

Net = GND;

Layer = Bottom Layer;

Hatching = Solid;

Remove Islands = True;

}

5.2.2 多层板中的地平面处理

在四层及以上PCB中,推荐将中间层设置为完整的地平面,以提供稳定的参考电位。地平面应避免被信号线切割,否则会增加回路面积,导致EMI问题。

设计建议:

- 高速信号尽量靠近地平面走线。

- 模拟地与数字地应通过磁珠或0Ω电阻隔离,最后在一点连接。

- 地平面应比电源平面小20倍线宽,以防止边缘辐射。

5.3 电源与地的布线优化实践

实际布线过程中,电源与地的处理需要结合具体电路需求进行优化。

5.3.1 电源去耦与滤波电容布局

去耦电容是电源设计中不可或缺的元件。一般建议:

- 高频去耦 :使用0.1μF陶瓷电容,靠近IC电源引脚。

- 低频去耦 :使用10μF电解电容,用于稳压。

在Altium中布局去耦电容的步骤:

1. 在原理图中添加去耦电容元件。

2. 使用【Compile】 > 【Check Project】确保电气连接正确。

3. 在PCB中手动放置电容,优先靠近电源引脚。

4. 使用【Interactive Routing】工具连接电容到电源和地。

5.3.2 过流保护与电源走线宽度计算

电源走线必须满足最大电流承载能力。走线宽度可根据以下公式估算:

Width = (I / (k * ΔT^0.44))^(1/0.725)

其中:

-

I:电流(A) -

k:铜厚系数(内层:0.024,外层:0.048) -

ΔT:允许温升(℃)

例如:1oz铜厚,允许温升10℃,承载3A电流时,走线宽度约为 40mil 。

5.3.3 电源完整性仿真与优化建议

Altium Designer提供Signal Integrity工具进行电源完整性仿真。通过仿真可以发现:

- 电源网络中的噪声峰值

- 去耦电容是否足够

- 是否存在共振频率

优化建议:

- 增加去耦电容,尤其是高频电容。

- 优化电源走线路径,缩短回路长度。

- 使用低ESR电容改善高频响应。

(本章内容未完待续)

简介:Altium Designer是一款集原理图设计、PCB布局、3D建模、仿真分析与嵌入式开发于一体的电子设计自动化(EDA)工具。本学习资料压缩包内容全面,涵盖从基础操作到高级功能的使用技巧,包含原理图绘制、电气规则检查、元件封装库管理、PCB布线优化、设计规则检查、3D建模、电路仿真、项目管理与嵌入式系统开发等内容。通过实例教程与案例解析,帮助学习者掌握Altium Designer的全流程设计能力,提升硬件开发效率与质量。

597

597

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?