一、关于模块

Verilog 的基本设计单元是“模块” (block)。一个模块是由两部分组 成的 ,一部分描述接 口,另一部分描述逻辑功能 ,即定义输入是如何影响输出的 。

如图,verilog 程序包括 4 个主要部分 : 端 口定义 、I/ O 说明、内部信号声明和功能定义 。

引用模块的两种方式:

( 1) 在引用时,严格按照模块定义的端口顺序来连接 ,不用标明原模块定义时规定的端口名,例如 :

模块名( 连接端 口 1信号名 ,连接端 口2 信号名 ,连接端 口 3 信号名 , 。。。)

( 2 ) 在引用时用“.”符号,标明原模块是定义时规定的端口名,例如:

模块名(.端 口 1名( 连接信号 1名), . 端 口2 名( 连接信号 2 名), •.•••..• )'

这样表示的好处在于可以用端口名与被 引用模块 的端口相对应 ,而不必严格按端口顺序对应 ,提高了程序的可读性和可移植性 。

模块中最重要 的部分是逻辑功能定义部分。有 3 种方法可在模块中产生逻辑 :

1) 用“assign ”声明语句

如 :assign a = b & c;这种方法的句法很 简单,只需写一个“assign”,后面再加一个方程式 即可 。例中的方程式 描述了一个有两个输入的与门。

2 ) 用实例元件

如 :and #2 u1 ( q , a , b ) ;

采用实例元件的方法像在电路图输入方式下调入库元件一样 ,键入元件的名字和相连的引脚即可,这表示在设计中用到一个跟与 门(and) 一样的名为u1的与门,其输人端为 a , b,输出 为 q。输出延迟为 2 个单位时间 。要求模块中每个具体化后的实例元件 的名字必须是惟一的,以避免与其他调用与门( and) 的实例混淆 。

3) 用“always”块

如 :always @ (posedge clk or posedge clr);

begin

if ( clr) q <= 0 ;

else if ( en) q <= d ;

end

PS:总结

( 1) 在 Verilog 模块中所有过程块(如 :initial 块 、always 块) 、连续赋值语句 、实例引用都 是并行的;在模块内部,语句是顺序执行的

(2) 它们表示的是一种通过变量名互相连接的关系 ;

( 3) 在同一模块中这三者 出现的先后顺序没有关系 ;

( 4 ) 只有连续赋值语句 assign 和实例引用语句可以独立于过程块而存在于模块的功能定义部分 。

二、数据类型及其常量和变量

verilog中共有19种数据类型,最常用的有4种:reg型、wire型、integer型、parameter型

(1)常量

1、数字

1)整数

8’ b10101100 //位宽为 8 的数的二进制表示 ,’ b 表示二进制

8’ ha2 //位宽为 8 的数的十六进制是示,’ h表示十六进制

2)x和z值

在数字电路中,x代表不定值,z代表高阻值

3)负数

-8 'd5 //这个表达式代表 5 的补数(用八位二进制数表示)

4)下画线

16 ’ h l 010_1011_1111_1010 //合法格式

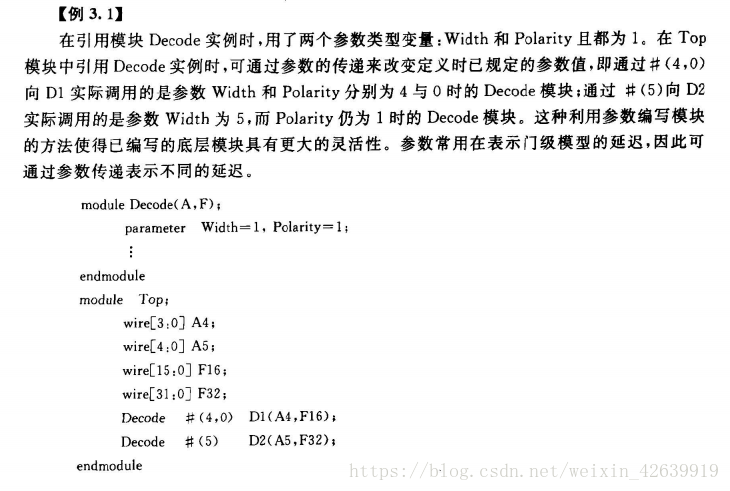

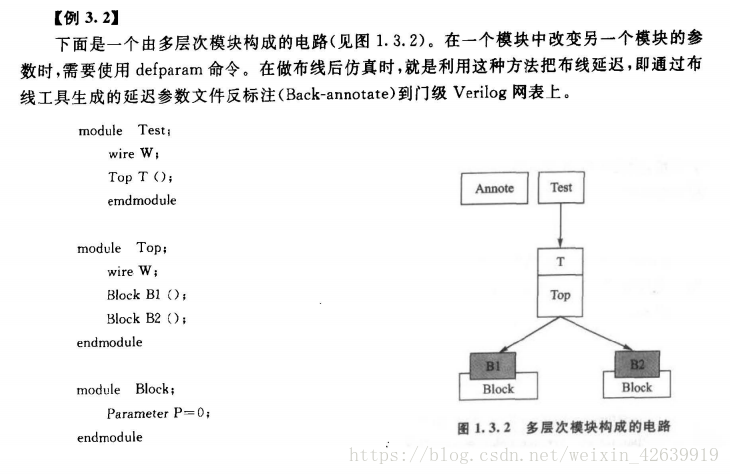

2、参数型(parameter)

格式: parameter 参数名1=表达式,参数名2=表达式,。。。。。

parameter msb= 7 ; //定义参数 msb 为常量 7

parameter e= 25 , f = 29 ;//定义两个常数参数

paramete rr = 5.7 ;//声明 r 为一个实型参数

parameter hyte_ size= 8 , byte_msb= byte_size- l ;//用常数表达式赋值

parameter average_delay = ( r+ f )/2 ; //用常数表达式赋值

(2)变量

1、wire型

wire型数据长用来表示用以assign关键字指定的组合逻辑信号。 网络类型的变量不能存储值,而且它必须受到驱动器(例如门或连续赋值语句,assign)的驱动。

wire a; //定义了一个 1位的 wire 型数据

wire [7:0] b;//定义了一个 8 位的 wire 型数据

wire [4:1] c,d;//定义了两个4位的wire型数据 ;

2、reg类型

reg类型数据的默认初始值为不定值X。

reg型数据常用来表示“always”模块内的指定信号,常代表触发器。

always模块内被赋值的每一个信号都必须定义为reg类型

reg 型数据的缺省初始值是不定值 。reg 型数据可以赋正值 ,也可以赋负值。但当一个reg 型数据是一个表达式中的操作数时,它的值被 当作是无符号值 ,即正值。例如 ,当一个 4 位的寄存器用做表达式中 的操作数时,如果开始寄存器被 赋以值 -1,则在表达式中进行运算时,其值被认为是十 15 。

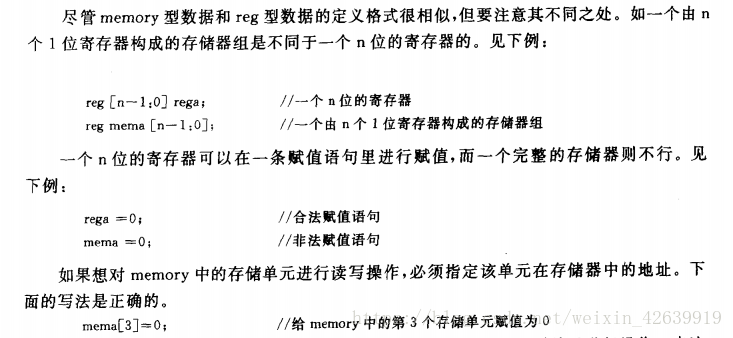

3、memory型

通过对 reg 型变量建立数组来对存储器建模,可以 描述 RAM 型存储器、 ROM 存储存和 reg 文件 。数组 中的每一个单元通 过一个数组索引进行寻址 。在 verilog语言中没有多维数组存在。memory 型数据是通过扩展 reg 型数据的地址范围来生成的 。其格式如下:

reg [n-1:0] 存储器名 [m-1:0];

或 reg [n -1:0] 存储器名[m :1],

例如: reg [7 :0] mema[255 :0];

这个例子定义了一个名为 mema 的存储器 ,该存储器 有 256 个 8 位的存储器 。该存储器 的地址沮围是 0 到 255 。

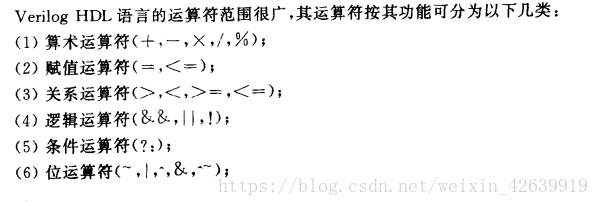

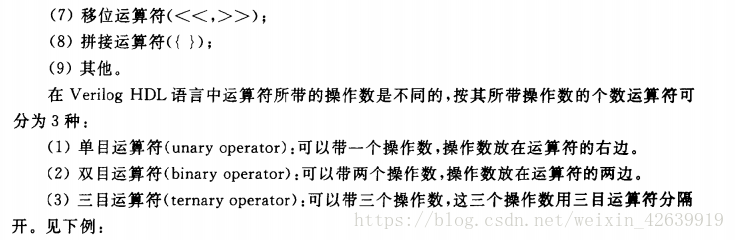

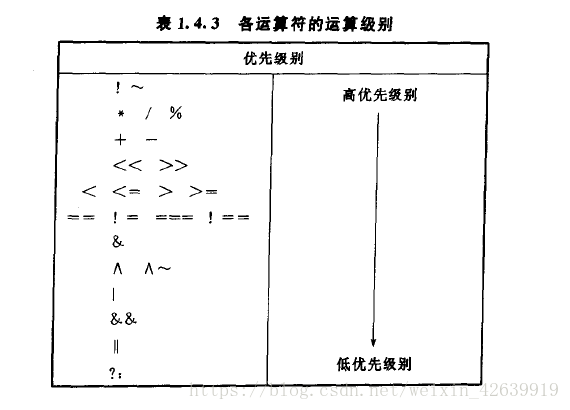

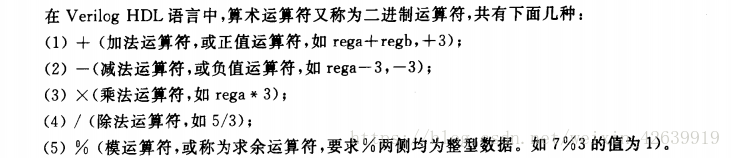

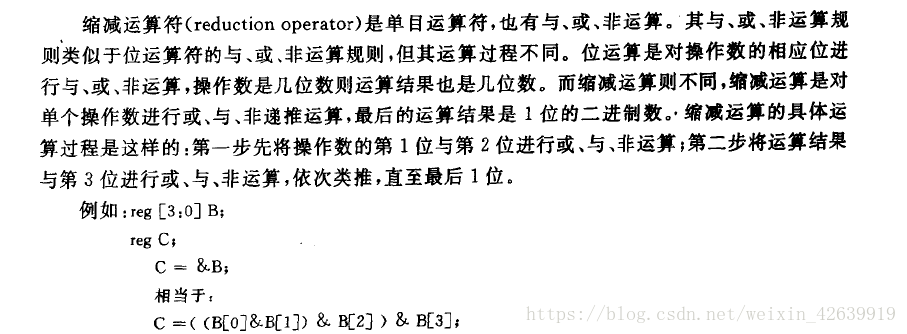

三、运算符及表达式

分别说明

3041

3041

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?