DRAM系列读书笔记,主要记录学习过程中的一些问题和一些自己的理解

Charpter7 Overview of DRAM

7.1 DRAM Basics:internals, Operation

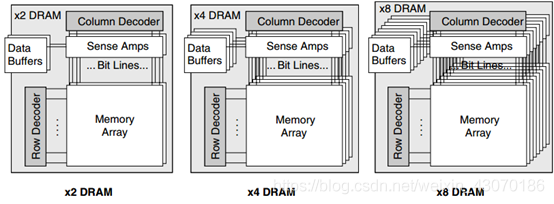

1、X2、X4、X8 dram的概念:

X几的DRAM就表示一个bank是由几memory array组成的,这几个memory array的操作都是同步的,所以X几的DRAM的每一个列地址就相当于可以存储几bit的数据。

如:x2的DRAM表示一个bank是由两个memory array组成的,由于对这两个阵列的操作行为都是一样的,因此,每个列地址的宽度相当于是2.同理,x4、x8的也类似。

X几dram的结构图如图7.1所示:

图7.1 每个bank的内部结构图

2、dram bank的概念

对于某n个memory array,当这n个memory array的操作行为与其它memory array的操作互不影响,那么就把这n个memory array的集合称为一个bank。

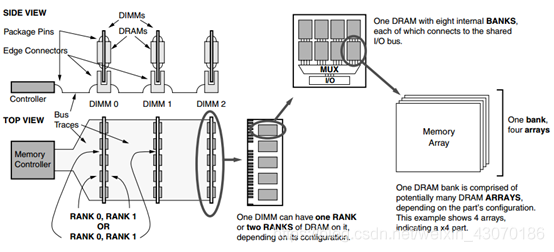

3、rank的概念:

对于一个计算机系统可能拥有多个dimm,每个dimm上又是由多个dram颗粒组成,这些dram颗粒也可能会被划分成几组,每一组的操作互不影响,因此为与dram颗粒的内部bank相区分,就产生了rank的概念。所谓rank就是指每个dimm上的dram的颗粒被分成的组,同一组内的dram颗粒操作都是同步的,不同组的dram颗粒操作互不影响,这就是rank的概念。

可见,bank是对dram颗粒内部进行的memory array进行分组的结果,rank是对dimm上dram颗粒进行分组的结果。

dimm、rank, bank, memory array的关系如图7.2所示:

简单的说,dimm就是内存条;dimm上是由多个dram颗粒构成的,这些dram颗粒会被分成几个小组,每一组的操作是同步的,不同组的操作互不影响,每个组就是一个rank;每个dram颗粒是由多个bank组成的;每个bank又是由多个memory array组成的。

图7.2 dimm、rank、bank、memory array之间的关系

4、CAS latemcy的概念

从DRAM收到CAS命令到数据出现在总线上的时间。

5、On chip DLL作用:

DLL的作用就是将DRAM的读数据和DQS信号与DRAM CROTROLLER与全局时钟相同步。所以DLL只跟读过程有关,跟写过程无关。

DRAM CROTOLLER一般有两个时钟,一个与全局时钟同步,另一个是与全局时钟相位相差90度,猜测与全局时钟同步的是写操作使用的时钟,相位相差90度的是DRAM CROTROLLER从DRAM中读数据的时钟。

至于在读操作时为何要是用DLL进行同步;

读操作过程,数据和DQS信号都是由DRAM给出的,且DQS和读数据是边沿对齐的(写操作DQS和读数据是中心对齐的),所以读操作的DQS不能被MEMORY CONTROLLER直接使用来采样读数据。

DLL具体作用过程分析:

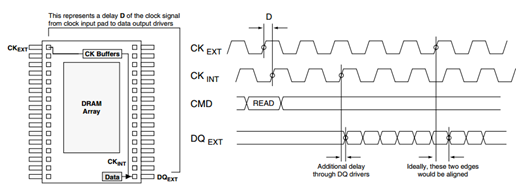

图7.3是未使用DLL的读数据时序;

CKext是全局时钟,就是DRAM CONTROLLER送给DRAM CMD、ACT、PRE、REF的时钟,当使用这个时钟从DRAM中读出数据时,由于一些固有的delay导致CKint与CKext相位的关系不太确定,而CKint就是驱动读数据和DQS的时钟。由于CKint与CKext相位的关系不太确定,当DRAM CROTROLLER使用与全局时钟相差90的时钟来采样读数据时,所采的读数据就可能出问题。

图7.3未使用DLL的读数据时序

图7.4是使用DLL后的读数据时序:

当使用DLL后,就可以保证CKint与CKext基本很接近了,这样从DRAM读出的数据虽然仍然和CKint是沿对齐,但是由于CKint与CKext很接近,当DRAM CONTROLLER使用与全局时钟相位差90度的时钟采样时,也能保证采到数据的中心附近,从而确保采样数据的正确性。

图7.4使用DLL的读数据时序

186

186

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?