文章目录

七、嵌套向量中断控制器和中断控制

7.1 嵌套向量中断控制器概述

我们已经了解了,嵌套向量中断控制器(NVIC)为集成在Cortex-M3处理器中的一部分,它同Cortex-M3的CPU内核逻辑紧密相连,其控制寄存器的访问方法和进行了存储器映射的设备一样。除了用于中断处理的控制寄存器和控制逻辑,NV1C单元还包括 SYSTICK定时器的控制寄存器以及调试控制。本章中,我们会看到用于中断控制的控制逻辑,存储器保护单元和调试控制逻辑将会在后面的章节中讨论。

NVIC支持1-240个外部中断输入(通常还被称作中断请求IRQ),具体数量由芯片生产商在开发Cortex-M3芯片的时候确定。另外,NVIC还有一个不可屏版中断(NMI)输人, NMI的实际功能也由芯片生产商确定。多数情况下,MI是不能被外部控制的。

NVIC可以通过系统控制空间(SCS)地址区域访问,该区域的存储器地址为 0xE000E000。大多数中断控制/状态寄存器只能在特权模式访问,而软件触发中断寄存器(STIR)是个例外,经过设置,在用户模式也能访问。中断控制/状态寄存器可通过多种传输方式访问,包括字、半字和字节传输。

另外,有些其他的中断屏蔽寄存器也同中断有关,它们为第3章中介绍的“特殊寄存器”,而且只能通过特殊寄存器访问指令进行操作:将特殊寄存器送至通用目的寄存器(MRS)和将通用目的寄存器送至特殊寄存器(MRS)指令。

7.2 基本的中断配置

每个外部中断都有与之相关的一些寄存器:

- 使能和清除使能寄存器;

- 设置挂起和清除挂起寄存器;

- 优先等级;

- 活动状态。

另外,其他的多个寄存器也可以影响到中断处理:

- 异常屏蔽寄存器(PRIMASK、FAULTMASK、BASEPRI);

- 向量表偏移寄存器;

- STIR;

- 优先级分组。

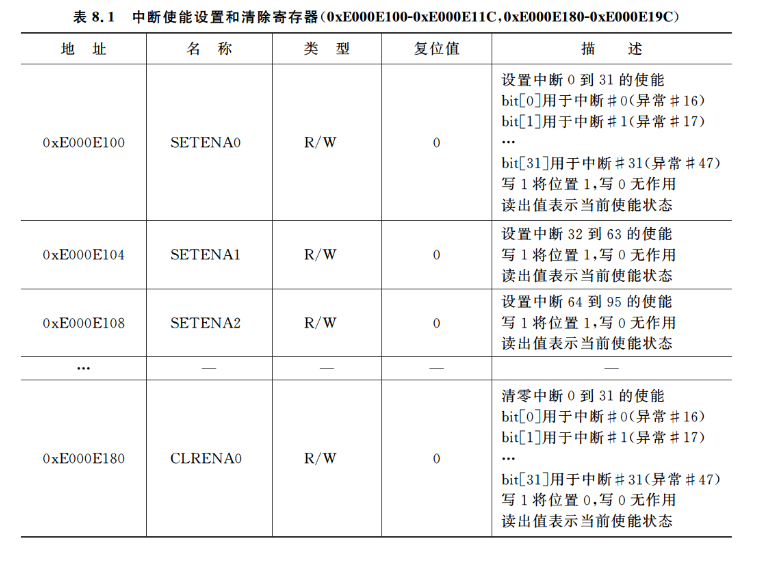

7.2.1 中断使能和清除使能

中断使能寄存器可以通过两个地址编程,要设置使能位,需要写SETENA寄存器地址;而要清除使能位,则需要写CLRENA寄存器地址。这样,使能和禁止中断就不会影响到其他的中断使能状态。SETENA和CLRENA寄存器都是32位宽的,每个位都代表一个中断输入。

由于Cortex-M3的外部中断可能超过32个,SETENA和CLRENA寄存器的个数可能会超过一个,如SETENA0、SETENA1等(见表8.1)。只有存在的中断的使能位才是可用的。所以,若只有32个中断输入,则只需要SETENA0和CLRENA0。SETENA和 CLRENA寄存器可以通过字、半字或字节的方式访问。由于前16个异常类型为系统异常,外部中断#0的起始异常编号为16(见表8.2)。

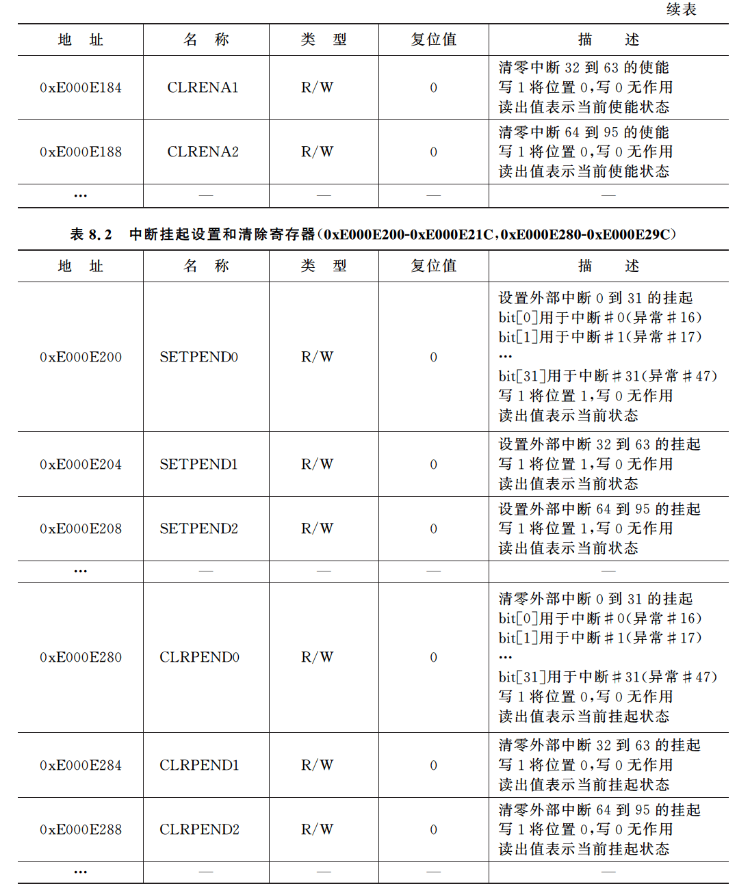

7.2.2 中断设置挂起和清除挂起

如果中断发生了而没有立即执行(例如,若另一个更高优先级的中断处理正在执行),它就会被挂起。中断挂起状态可以通过中断设置挂起(

Cortex-M3嵌套向量中断控制器详解:配置、优先级与SYSTICK定时器,

Cortex-M3嵌套向量中断控制器详解:配置、优先级与SYSTICK定时器,

本文详细阐述了Cortex-M3处理器中的嵌套向量中断控制器NVIC的结构、基本中断配置步骤,包括中断使能、清除、优先级设置、活跃状态管理和特殊寄存器如PRIMASK、FAULTMASK。同时,重点介绍了SYSTICK定时器的使用及其在系统中的角色。

本文详细阐述了Cortex-M3处理器中的嵌套向量中断控制器NVIC的结构、基本中断配置步骤,包括中断使能、清除、优先级设置、活跃状态管理和特殊寄存器如PRIMASK、FAULTMASK。同时,重点介绍了SYSTICK定时器的使用及其在系统中的角色。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

998

998

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?