玩转Zynq连载18——[ex01] 小试牛刀,基于Zynq PL的第一个工程

更多资料共享

腾讯微云链接:https://share.weiyun.com/5s6bA0s

百度网盘链接:https://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw

提取码:ld9c

腾讯微云链接:https://share.weiyun.com/5s6bA0s

百度网盘链接:https://pan.baidu.com/s/1XTQtP5LZAedkCwQtllAEyw

提取码:ld9c

1概述

蜂鸣器是一种最简单的发声元器件,它的应用也非常广泛,大都是作为报警或发声提醒装置。比如台式电脑在刚开机时,通常主板上会发出一声较短的尖锐的“滴……”的鸣叫声,提示用户主板自检通过,可以正常进行后面的启动;而如果是1长1短或1长2短的鸣叫声,则表示可能发生了电脑内存或显卡故障;当然还可以有其他不同的鸣叫声提示其他的故障,总而言之,可别小看了这颗区区几毛钱的蜂鸣器,关键时刻还挺有用的。可以毫不夸张的说,蜂鸣器也算是一种人机交互的手段。

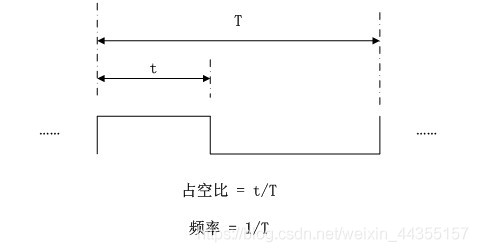

PWM(Pulse Width Modulation),即脉冲宽度调制,如图所示,PWM的输出只有高电平1和低电平0。PWM不停的重复输出周期为T,其中高电平1时间为t的脉冲,t/T是它的占空比,1/T是它的频率。

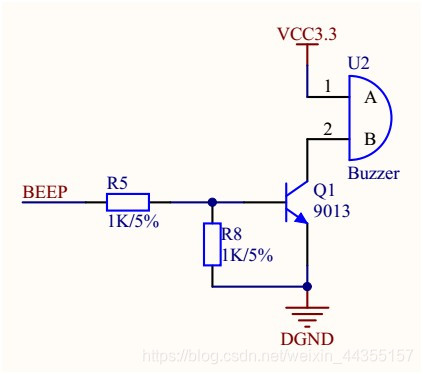

如图所示,这是Zstar板上蜂鸣器的电路原理图,BEEP网络连接到FPGA的IO上,当BEEP = 1时,三极管Q1的BE导通,则CE也导通,蜂鸣器U2就有电流回路,那么蜂鸣器就会发声。同理,BEEP = 0时,Q1截止,蜂鸣器无电流回路,那么蜂鸣器就不会发出声音。

如图所示,基于蜂鸣器在FPGA的IO输出1就发声、0则不发声的原理,我们给IO口一个占空比为10%的PWM的信号,让蜂鸣器间歇性的发声鸣叫。如果它的频率高,则发声就显得相对尖锐急促一些;如果它的发声频率低,则发声就显得低沉平缓一些。

在我们给出的实例代码中,我们期望产生一个输出频率为1Hz(1s)、占空比为10%的PWM信号去驱动蜂鸣器的发声。因此,我们使用系统时钟25MHz进行计数,每计数25,000,000次,这个计数器就清零重新计算。因为这个计数器是2进制的,要能够表达0-24,999,999的每一个计数值,那么这个2进制计数器至少必须是25位的(代码中取计数器为28位)。此外,为了得到输出的PWM占空比为10%,那么我们只要判断计数值小于最大计数值的1/10即2,500,000时,输出高电平1,反之输出低电平0。

创建一个最终可以跑在Zynq的PL上的应用工程,最基本的可以归纳为以下几个步骤。下面我们会逐一进行实践操作。流程不过是一个熟能生巧的过程,只要大家认真走过一遍,后续大量实例中不断操作,反复练习就能轻松掌握。

2 新建Vivado工程

参考文档《玩转Zynq-工具篇:新建Vivado工程.pdf》。

3 创建工程源码

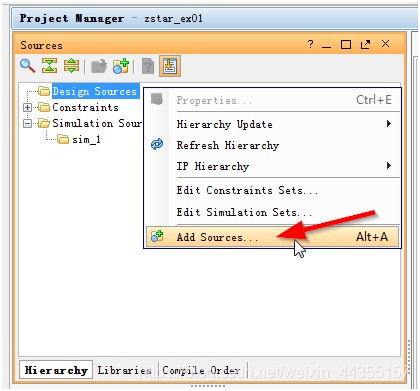

如图所示,选中Project Manager Sources Design Sources,右键单击,弹出菜单中选中Add Sources…。

图新建Verilog源码菜单

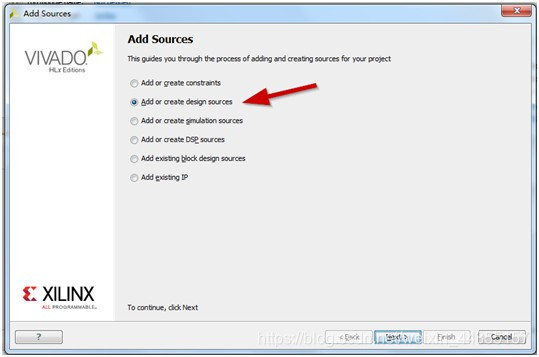

接着如图所示,使用默认选项Add or create design sources,点击“Next”。

图选择文件类型

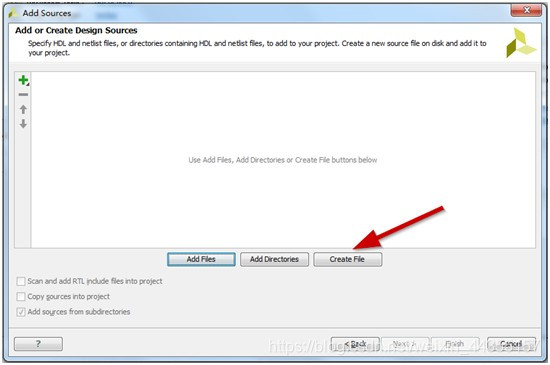

如图所示,单击Create File按钮。

图新建设计文件

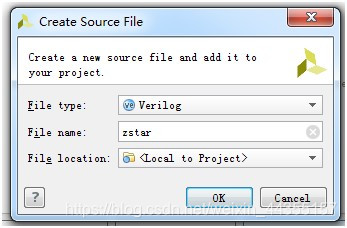

如图所示,设置创建的文件类型(File type)为Verilog;文件名(File name)为zstar;文件路径(File location)为默认的。

图6.20 设置新建文件名称和路径

最后点击Finish按钮完成Verilog源文件创建。

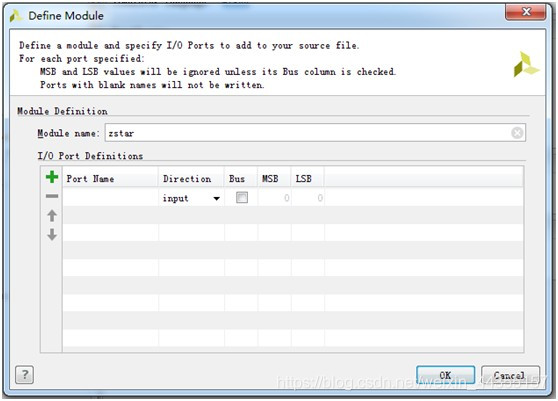

随后还会弹出如图所示的模块端口设置页面,可以直接点击OK不做设置。

图定义模块

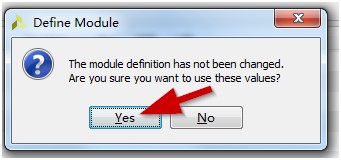

接着还会弹出如图所示的确认对话框,点击Yes。

图定义模块确认对话框

如图所示,双击Design Sources下刚刚创建好的zstar.v文件,将弹出源码,里面有基本的Verilog模块定义,内容空空如也,需要我们来填充。

图6.23 创建好的Verilog源文件

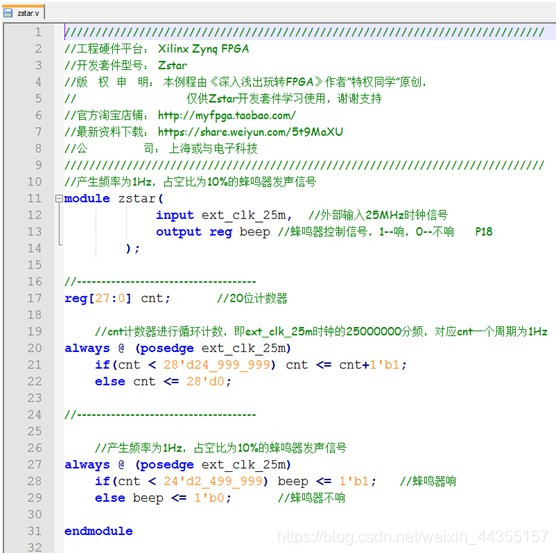

如图所示,将Verilog代码填充进去,实现一个完整的设计源码模块。

图 Verilog源码

4 创建约束文件

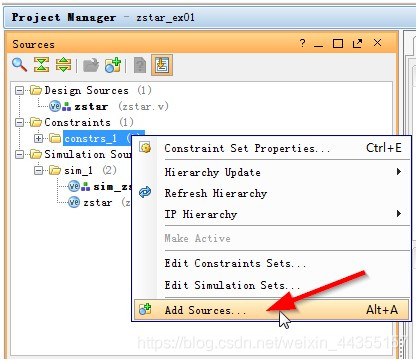

如图所示,选中Project Manager Constraints constrs_1,右键单击,在弹出菜单选择Add Sources…。

图新建约束文件菜单

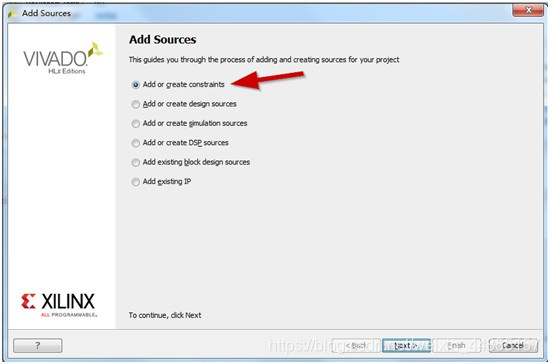

接着如图所示,使用默认选项Add or create constraints。

图选择文件类型

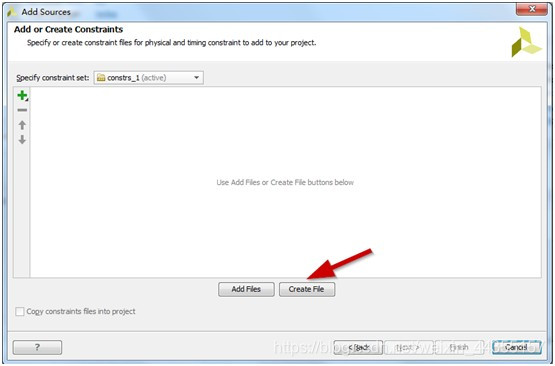

如图所示,单击Create File按钮。

图新建设计文件

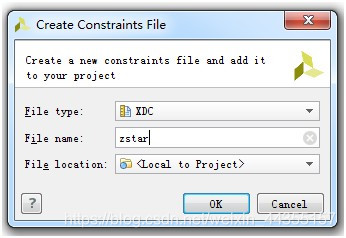

如图所示,设置创建的文件类型(File type)为XDC;文件名(File name)为zstar;文件路径(File location)为默认的。

图设置新建文件名称和路径

最后点击Finish按钮完成约束文件创建。

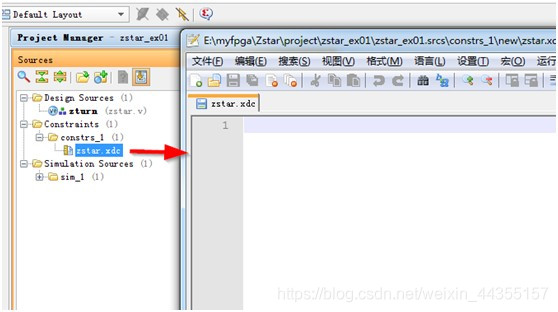

如图所示,双击Constraints下刚刚创建好的zstar.xdc文件,里面是完全空白的。

图创建好的约束源文件

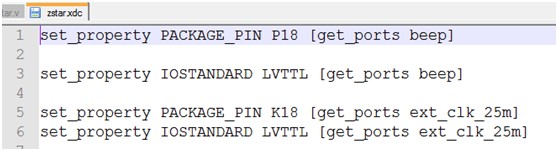

如图所示,将这个实例的引脚约束都写入这个约束文件中。从简单的语法可以看出,这里约束了zstar中顶层接口信号对应Zynq芯片的引脚号(PACKAGE_PIN)以及电平标准(IOSTANDARD)。

图引脚约束脚本

如图所示,工程路径下新产生的zstar.srcs\source_1和zstar.srcs\constrs_1文件夹分别和Project Manager下的Design Source和Constraints相对应。

图工程路径下对应的文件夹

5 功能仿真

参考文档《玩转Zynq:Vivado中PL的功能仿真.pdf》。

6编译

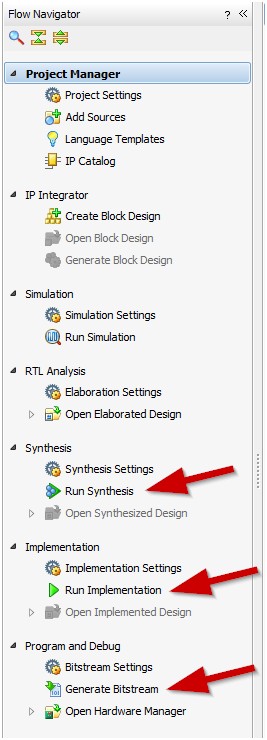

如图所示,Vivado的编译主要分为三步,即Run Synthesis(综合编译)、Run Implementation(实现编译)和Generate Bitstream(生成bit流)。一般而言,我们直接点击Generate Bitstream生成bit文件后就可以进行板级调试。

图编译菜单

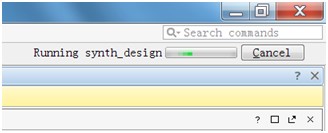

编译过程中,如图所示,在Vivado工具的右上角,有当前编译的状态指示。

图编译状态信息

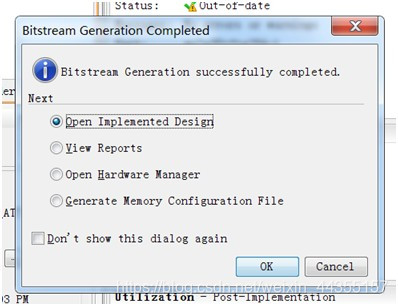

如图所示,编译完成后,会弹出提示选项窗口,该窗口有多个下一步操作执行的选项可供选择。大家可以直接点击Open Hardware Manager进入板级下载调试的界面。

图 bit流生成完成后的选择窗口

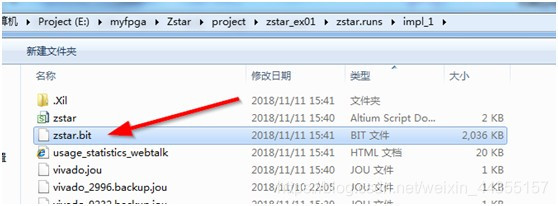

如图示,在工程路径“…/project/zstar_ex01/zstar.uns/impl_1”下就生成了zstar.bit文件,这是用于烧录到FPGA在线运行的比特流。

图生成的bit文件

7 板级调试

参考文档《玩转Zynq-环境篇:XilinxPlatformCableUSB下载器使用指南.pdf》。

2145

2145

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?