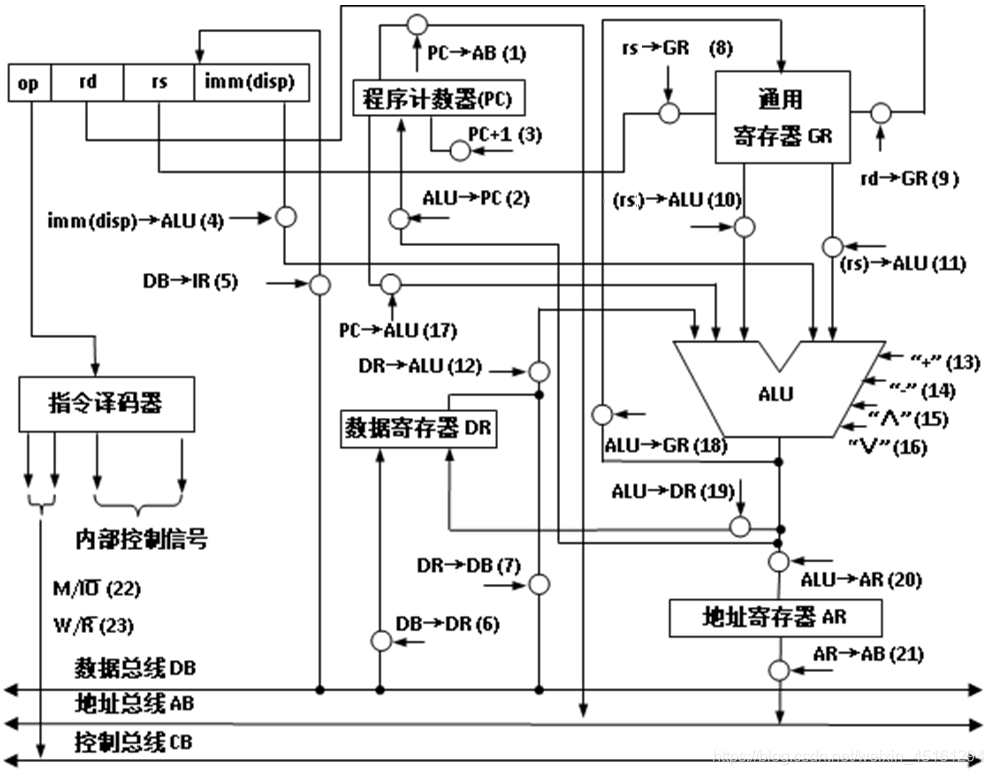

一 冯诺依曼结构CPU图示

二 代码实现的指令

计算机数据总线和地址总线都是16位,指令系统包括4条指令:addi, lw, sw, add,

- addi: (rd) <- (rs) + imm

从寄存器rs中读取数据,和立即数imm相加后,结果放到寄存器rd中。 - lw: (rd) <- memory((rs) + imm)

从地址为(rs) + imm的存储器中读取数据到寄存器rd中。 - sw: memory((rd) + imm) <- (rs)

从寄存器rs中读取数据到地址为(rd) + imm的存储器中。 - add: (rd) <- (rd) +(rs)

从寄存器rd和rs中读取数据,相加结果放到寄存器rd中。

指令的格式固定,单字长(16位),指令格式:op| rd | rs | imm。

其中op为操作码,rd为目的寄存器,rs为源寄存器,imm为立即数。

共8个通用寄存器,寄存器R0的值恒为0,rd和rs是GR中8个寄存器之一(操作码中的rd和rs指的是8个通用寄存器的编号,即地址)。

三 实验报告包含的内容

设计思路描述

1、CPU基本组成

1.1 运算器部分

1.2 控制器部分

1.3 数据通路

2、CPU的工作过程

2.1 CPU的工作时序

2.2 指令的执行过程

2.3 指令说明

3、关键模块定义

3.1 存储器Memory

3.2 时序信号产生模块CLOCK

3.3 取指令模块IFU

3.4 通用寄存器GR

3.5 ALU

3.6 控制器controller

3.7 CPU

程序代码变量说明

CPU各模块的功能和接口

程序代码结构说明

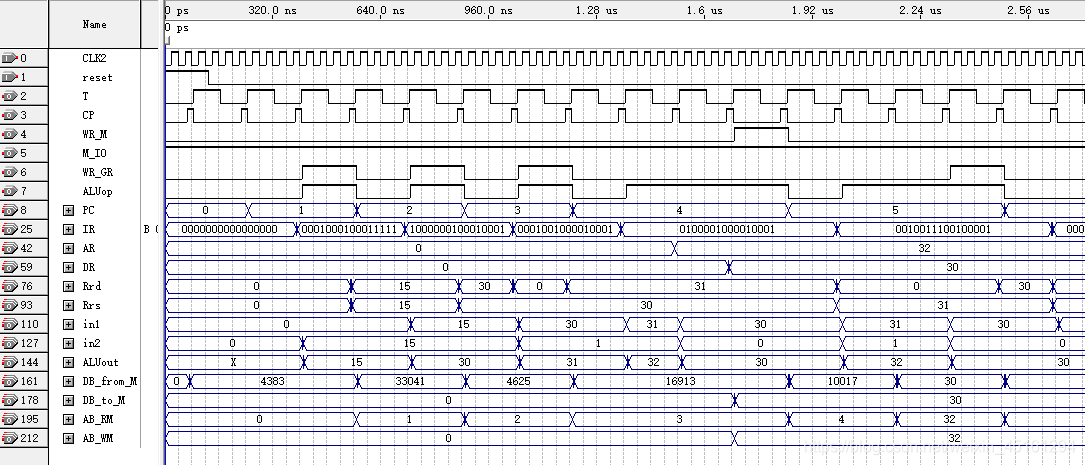

模拟图及分析

软件:Quartus II 9.0

代码下载

含verilog代码、实验报告

2481

2481

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?