第1章 计算机系统概述

(一)计算机系统层次结构

计算机系统的基本组成

计算机系统包括硬件系统和软件系统

软/硬件在逻辑功能上等价:对某一功能,既可用软件实现、又可又硬件实现

硬件实现的功能一般比软件实现具有更高的执行速度

计算机硬件的基本组成

冯诺依曼机基本思想

- 控制流驱动方式:按照指令的执行序列,依次读取指令。冯诺依曼计算机的基本工作方式

- 存储程序:首次提出。按地址访问并顺序执行指令

- 计算机硬件系统由运算器、存储器、控制器、输入设备、输出设备5大部件组成

- 控制器是区分指令和数据的核心部件,主要通过 “取指周期” 和 “执行周期” 的交替来实现。

计算机硬件系统

-

运算器

-

用于进行算术运算和逻辑运算,核心是算术逻辑单元(ALU)

-

包含若干通用寄存器、累加器(ACC)、乘商寄存器(MQ)、操作系寄存器(X)、变址寄存器(IX)、基址寄存器(BR)

-

包括数据总线

-

-

存储器

- 分为主存储器(也称内存储器/主存)和辅助存储器(也称外存储器/外存)

- 主存储器的工作方式:按存储单元的地址进行存取,称为按地址存取方式

- 存储体:存放二进制信息

- 存储器地址寄存器(MAR):存放访存地址,位数与地址码长度相同

- 存储器数据寄存器(MDR):暂存要从存储器中读或写的信息,位数与存储字长相同

- 时序控制逻辑:产生存储器操作所需的各种时序信号

- 地址译码器:将 MAR 中的地址翻译为存储体中具体某一行(存储单元)的访问控制信号

- 相联存储器(又称按内容寻址存储器):既可以按地址寻址又可以按内容寻址

-

控制器

- 由程序计数器(PC)、指令寄存器(IR)、控制单元(CU)组成

- PC:具有自动加1功能。存放下一条指令的地址

- IR:存放当前的指令

-

输入设备

- 将程序和数据以机器能识别和接受的信息形式输入计算机

-

输出设备

- 将计算机处理的结果以人们所能接受的形式或其它系统所要求的信息形式输出

-

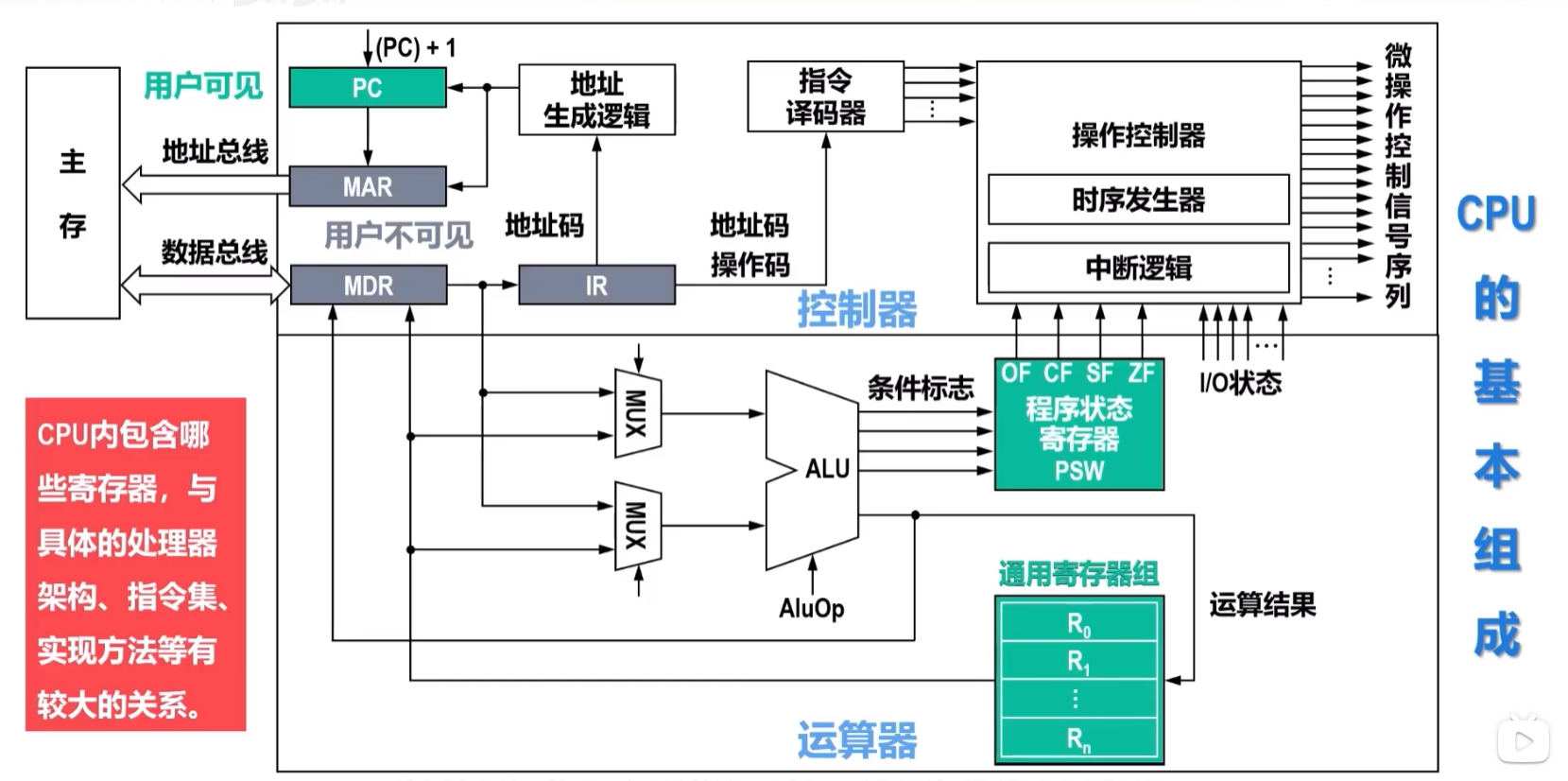

中央处理器(CPU)

- 运算器和+控制器

- 寄存器:是 CPU 内部用来暂存数据、指令和地址的高速存储单元 ,数量相对较少。通常由触发器构成

- Cache(高速缓冲存储器):属于一种高速、小容量的临时存储器,比寄存器的存取速度慢。

- PC、状态寄存器、通用寄存器,用户可见

- IR、MAR、MDR,用户不可见

- 存取速度:寄存器>Cache>内存

- 主机:CPU+主存储器

CPU由运算器和控制器两大部分组成:

计算机软件和硬件的关系

软件按功能分类

- 系统软件:作为系统资源提供用户使用,主要有操作系统(OS)、数据库管理系统(DBMS)等

- 应用软件:用户为解决某个应用领域中的各类问题而编制的程序

计算机语言

- 机器语言(也称二进制代码语言):是计算机唯一可以直接识别和执行的语言

- 汇编语言:用助记符编写的语言

- 高级语言:

指令集体系结构(ISA/软件可见部分):

- 位于软件和硬件之间的界面。ISA定义了所有指令的集合,每条指令规定了计算机执行什么操作

- 硬件相同,操作系统不同,拥有相同的指令集体系结构

- 硬件不同,指令集体系结构一般也会改变

计算机系统的工作原理

“存储程序”工作方式

- 程序执行前,将程序所含的指令和数据送入主存储器,将程序的第一条指令的地址存放到PC中

- 一旦启动,无须操作人员干预,计算机自动取出并执行一条一条指令

高级语言与机器语言程序的转换

翻译过程分为四个阶段:预处理阶段 -> 编译阶段 -> 汇编阶段 -> 链接阶段

翻译程序:把高级语言源程序转换成机器语言程序的软件

- 编译程序:将源程序一次全部翻译成目标程序,并且会生成目标代码文件

- 解释程序:边翻译边执行,不会生成目标代码文件,执行速度相对编译程序慢

- 汇编程序:把汇编语言源程序翻译为机器语言程序

程序和指令的执行过程

(二)计算机的性能指标

缩短指令执行过程中访问内存的时间可以显著缩短 CPU 执行时间,因为内存访问延迟是 CPU 性能的核心瓶颈之一。

机器字长(简称字长)*

“某16位或某32位机器”,字长是指计算机进行一次整数运算所能处理的二进制数据的位数,可以用来评价计算机性能

字长越长、数的表示范围更大,计算精度越高

指令字长:

-

是指 一条机器指令所占的位数或字节数。

-

取决于指令的功能和格式,可以是单字长、半字长、双字长

-

编址方式 编址单位 指令字长建议 核心原因 按字节编址 8 位 8 的倍数 避免指令跨字节,简化 CPU 取指 按 6 位字编址 6 位 6 的倍数 避免指令跨 6 位字,简化 CPU 取指 通用原则 N 位 N 的倍数 与编址单位对齐,兼顾机器字长

数据通路带宽*

外部数据总线一次所能并行传送信息的位数

主存容量*

指主存储器所能存储信息的最大容量,以字节(B)来衡量,也可用字数*字长来表示存储容量

MAR的位数反映了能访问多少个单元(地址范围),MDR的位数反映了每个单元的数据位数(存储字长)

存储字长:即每个存储单元可存储的二进制位数,是由 MDR 的位数决定的;

运算速度

-

吞吐量:指系统在单位时间内处理请求的数量

- 用户观点评价的综合参数

-

响应时间:指从用户向计算机发送一个请求,到系统对该请求做出响应并获得所需结果的等待时间

- CPU 中断总耗时 = 中断响应时间 + 中断处理时间

-

CPU时钟周期:CPU工作的最小时间单位

- 时钟周期数=主频*程序运行时间

-

CPU主频:指CPU使用的时钟频率,单位时间执行的时钟周期数

- 假设时钟周期2ns,则主频=1/2ns=500MHz

-

CPI:执行一条指令所需的时钟周期数

- CPI=总时钟周期数/指令数

- 与系统结构、指令集、计算机组织有关

-

CPU执行时间 = CPU时钟周期数 / 主频 = ( 指令条数 * CPI ) / 主频

- CPU的性能(CPU执行时间)取决于:主频、CPI、指令条数

- CPU执行时间=主频指令数×CPI

- CPU速度提高50%,相当于主频f->1.5f

-

IPS:每秒执行多少条指令,IPS = 主频 / 平均CPI

-

MIPS:每秒执行多少百万条指令

- MIPS=指令条数/(执行时间

*106)=主频/(CPI`*`106)

- MIPS=指令条数/(执行时间

-

FLOPS:即每秒执行多少次浮点运算

- **M **FLOPS:10^6

- **G **FLOPS:10^9

- T FLOPS:10^12

- **P **FLOPS:10^15

- E FLOPS:10^18

- Z FLOPS:10^21

基准程序*

专门用来进行性能评估的一组程序,可以在不同机器上运行相同的基准程序来比较在不同机器上的运行时间,从而评测其性能

- 对于不同的应用场合,应该使用不同的基准程序

- 也存在一些缺陷,可能得不到准确的性能评测结果

专业术语*

- 并行处理技术:当前设计高性能计算机的重要途径

- 系列机:具有相同基本体系结构、基本指令系统的多个不同型号计算机组成

- 兼容:指计算机软件或硬件的通用性,通常在同一系列不同型号的计算机间通用

- 固件:将程序固化在ROM中组成的部件

单位换算*

| 单位 | 类型 | 用途 | 换算规则 | 常见场景 |

|---|---|---|---|---|

| KB/MB | 二进制(Byte) | 存储容量 | 1 KB=1024 B1\ \text{KB}=1024\ \text{B}1 KB=1024 B | 硬盘容量(512GB)、文件大小(2MB) |

| kb/Mb | 十进制(bit) | 数据传输 | 1 kb=1000 b1\ \text{kb}=1000\ \text{b}1 kb=1000 b | 网速(100Mbps)、带宽(500Mb) |

2477

2477

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?