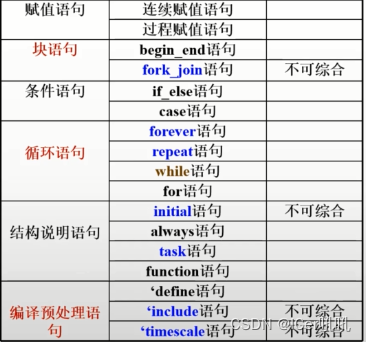

不可综合语句经常用在测试文件中,未注明的语句均是可综合的

赋值语句

1.连续赋值语句——assign语句,用于对wire型变量赋值,是描述组合逻辑最常用的方法之一。

例:assign c=a&b; // a,b,c 均为wire型变量

2.过程赋值语句——用于对reg型变量赋值,有两种方法:

非阻塞赋值方法:符号<=

阻塞赋值方法: 符号为=

阻塞于非阻塞赋值的区别:

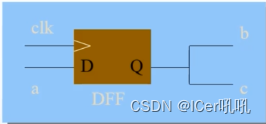

1.非阻塞赋值方式:

always @(posedge clk)

begin

b <= a;

c <= b;

end非阻塞赋值在块结束时才完成赋值操作(c的值比b的值落后一个时钟周期)

2.阻塞赋值方式

always @(posedge clk)

begin

b = a;

c = b;

end阻塞赋值语句在该语句结束时就完成赋值操作(在块语句中,如果有多条阻塞赋值语句,在前面的赋值语句没有完成之前,后面的语句就不能被执行,就像被阻塞一样,因此称为阻塞赋值方式。这里的c和b的值一样。)

非阻塞赋值于阻塞赋值方式的主要区别:

非阻塞赋值:b的值被赋成新值a的操作,并不是立刻完成,而是在块结束时才完成;

块内的多条语句在块结束时同时赋值。

硬件有对应电路。

阻塞赋值: b的值立刻被赋成新值a;

完成该赋值语句后才能执行下一条语句;

硬件没有对应的电路,因而综合结果未知。

块语句

用来将两条或多条语句组合在一起,使其在格式上更像一条语句,以增加程序的可读性

块语句有两种:

begin...end语句——标示顺序执行的语句

fork...join语句——标示并行执行的语句(不可综合)

begin...end:

块内的语句是顺序执行的

每条语句的延迟时间是相对于前一条语句的仿真时间而言的

直到最后一条语句执行完,程序流程控制才能跳出该顺序块

块内语句可以是参数声明,reg变量声明,integer变量声明,real变量声明语句

#可以用在语句块中表示延迟,(在模块调用过程中使用#表示参数的传递)

fork...join:

块内的语句是并行执行的

每条语句的延迟时间是相对于开始仿真时间而言的

如何跳出该顺序块由(fork...join,fork...join_any,fork...join_none)决定

块内语句可以是参数声明,reg变量声明,integer变量声明,real变量声明语句,time变量声明语句和事件(event)说明语句。

6282

6282

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?