-

基本要求:基于DE2-115开发板在Quartus13.1平台上用verilog设计一个24h制数字钟,要求能显示时,分,秒,并可手动调整时和分。

-

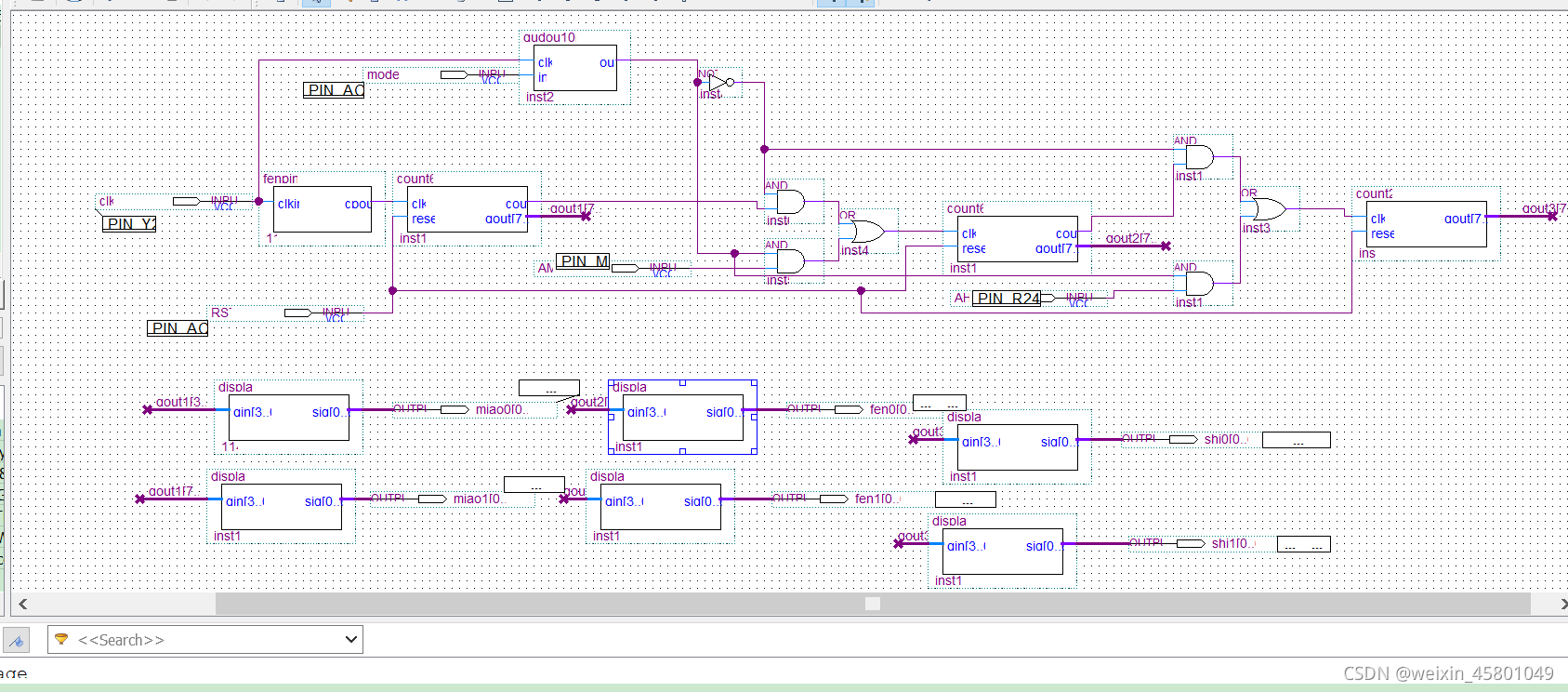

实验分析:利用两个60进制,一个24进制模块,用1Hz分频模块给秒模块自动计时,以秒模块进位信号为分模块时钟,以分模块进位信号为时模块时钟,用6个display数码管显示模块分别显示时,分,秒。

用与非门搭建一个二选一数据选择器,用一个拨动开关mode切换自动,手动状态(无消抖需加消抖模块,否则切换瞬间导致数码管跳变;虽然按键经消抖处理,但调整时间时需要长按按键保持0状态,较为不便,故选择拨动开关),手动调整时,以按键AH,AM为时钟调整时分

效果演示:

eda verilog 数字钟 eda verilog 数字钟_哔哩哔哩_bilibili

原理图及代码:

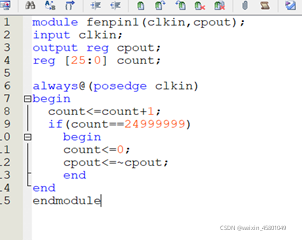

fenpin1:板上50Mh时钟计数25000,000个时翻转一次为1hz。

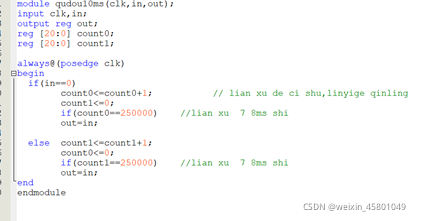

qudou10ms:抖动就是短时间(10ms左右)内在0,1之间发生跳动,可以人为忽略,只输出稳定时间大于10ms的0,1电平。

时间用50Mhz计数表示,每来一个上升沿计一次数,连续计数250000个(大约为10ms稳定的电平才认为其有效,否则不予输出)。

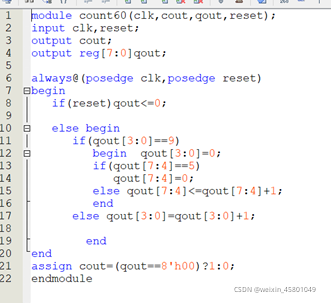

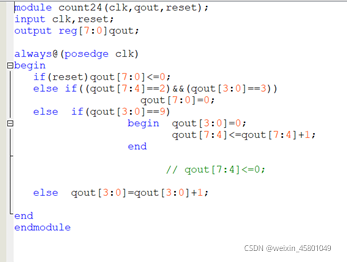

count60与count24类似,先考虑低位,再考虑进位。

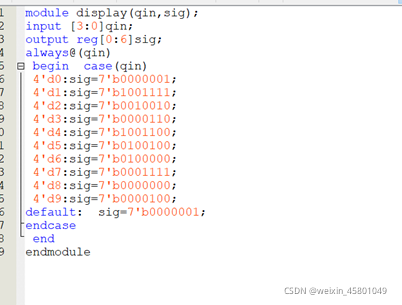

display:开发板数码管低电平点亮对应段选,结合数码管内部电路图译码。

- 设计总结

- 题目手动调整时分功能可以在代码中另设按键直接调整进位信号,设置mode开关不太必要,但在处理问题过程中我学到了不少,即用verilog控制FPGA此类器件直接操作门阵列不同于C语言,它更像是组合门电路,而C语言是单纯逻辑操作。由此便很容易想到用门电路实现数据选择器,若放在C语言中便只是if else,用标志位选择。。消抖处理时经大量查找资料发现大部分采用延时判断,代码复杂,不适用,经过优化改进, 此消抖模块简单使用,可以说这是个不小的收获。

初次发文总结学习心得,感觉不错,一起进步成长啊!

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?