文章目录

一.基本概念

单周期处理机中采用串行方法执行的指令,同一时刻CPU中只有一条指令在执行,各功能部件的使用率不高。现代计算机普遍采用指令流水线技术,同一时刻有多条指令在CPU的不同功能部件中并发执行,大大提高了功能部件的并行性和程序的执行效率。

一条指令的执行过程可分解为若干阶段,每个阶段由相应的功能部件完成。如果将各段视为相应的流水段,那么指令的执行过程就构成了一条指令流水线。

为了提高执行速度,将一条指令的执行过程分为取指令、指令译码、执行和写回四个阶段,就形成了四级流水;若分为取指令IF、指令译码ID、取操作数OF、执行EX、写回WB,就形成了五级流水。

指令流水段的个数以最复杂指令所用的功能段个数为准,流水段的长度以最复杂的操作所花时间为准,因此将每个阶段的耗时取成一样,以最长耗时为准。对于耗时较短的指令,可以将本段处理完成的数据和控制信号保存在流水寄存器/缓冲寄存器/锁存器中,以保证本段的执行结果能在下个时钟周期给下一流水段使用。

每个流水段后面都需要增加一个流水寄存器,用于锁存,

1.多条指令在处理器中的执行方式

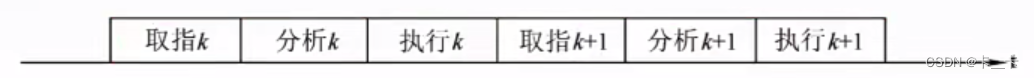

(1)顺序执行方式/串行执行方式

前一条指令执行完才能启动下一条指令。冯·诺依曼采用的就是顺序执行方式

优点:控制简单,硬件代价小

缺点:执行指令速度慢,功能部件的利用率低(若取址时内存忙碌,但执行指令部件是空闲的)

假设取址、分析、执行三个阶段的用时均为t,顺序执行n条指令所用时间T=3tn

(2)流水线执行方式

①一次重叠执行方式

假设取址、分析、执行三个阶段的用时均为t,执行n条指令所用时间T=(n-1)×2t+3t=2nt+t=(2n+1)t

优点:与顺序执行方式相比,程序的执行时间缩短了1/3(当n→∞时),各功能部件的利用率明显提高

缺点:需要付出硬件上较大开销的代价,控制过程也比顺序执行复杂了

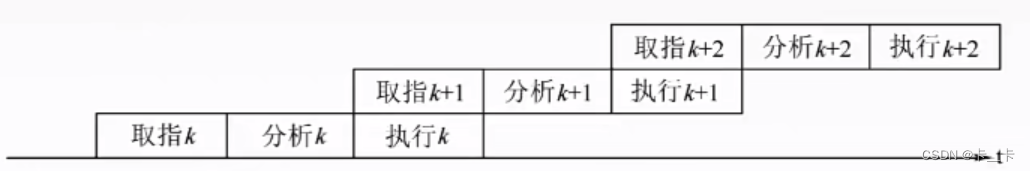

②二次重叠执行方式

T=(n-1)×t+3t=nt+2t=(n+2)t

优点:与顺序执行方式相比,程序的执行时间缩短了2/3(当n→∞时),各功能部件的利用率进一步提高

缺点:需要付出硬件上较大开销的代价,控制过程也比顺序执行复杂了

2.流水线的表示方法(时空图)

时空图用于分析流水线的性能。

横坐标表示时间,即输入流水线中的各个任务在流水线中经过的时间;纵坐标表示空间,即流水线的每个流水段(即各执行部件)。流水线中各个流水段的执行时间都相等。

第一条指令I1在时刻t0进入流水线,在t0-t1时间段内处于取指令阶段,在t1-t2时间段内处于译码阶段,在时刻t4流出流水线。共有4个不同的功能部件(流水段),因此此图叫做4个功能段的指令流水线时空图

本文介绍了指令流水线技术,包括多条指令在处理器中的执行方式,如顺序和流水线执行;流水线的分类,如部件功能级、单功能等;影响流水线的因素,如资源、数据和控制冲突;性能指标,如吞吐率、加速比和效率;还阐述了五段式指令流水线及各类指令执行过程。

本文介绍了指令流水线技术,包括多条指令在处理器中的执行方式,如顺序和流水线执行;流水线的分类,如部件功能级、单功能等;影响流水线的因素,如资源、数据和控制冲突;性能指标,如吞吐率、加速比和效率;还阐述了五段式指令流水线及各类指令执行过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4307

4307

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?