为 8 位输入构建优先级编码器。给定一个 8 位向量,输出应报告向量中的第一个位 1。如果输入向量没有高位,则报告零。例如,输入 8'b10010000 应输出 3'd4,因为 bit[4] 是第一个高位。

从上一个练习(always_case2),案例陈述中将有256个案例。如果支持的事例语句中的事例项不关心位,我们可以将其减少(减少到 9 个事例)。这就是 casez 的用途:它将具有值 z 的位视为在比较中不关心。

通过数字信号处理的学习可知:8-3位二进制优先编码器的真值表如下:

| 输入 | 输出 | |||||||||

| I7 | I6 | I5 | I4 | I3 | I2 | I1 | I0 | Y2 | Y1 | Y0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | x | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 1 | x | x | 0 | 1 | 0 |

| 0 | 0 | 0 | 0 | 1 | x | x | x | 0 | 1 | 1 |

| 0 | 0 | 0 | 1 | x | x | x | x | 1 | 0 | 0 |

| 0 | 0 | 1 | x | x | x | x | x | 1 | 0 | 1 |

| 0 | 1 | x | x | x | x | x | x | 1 | 1 | 0 |

| 1 | x | x | x | x | x | x | x | 1 | 1 | 1 |

其中第一行为default语句。

经过学习笔记8HDLBITS笔记8:4-2优先编码器_炒鸡无敌大美女的博客-CSDN博客

法1:可编写代码如下(使用casez语句块):

module top_module (

input [7:0] in,

output reg [2:0] pos );

always@(*)

begin

casez(in[7:0])

8'bzzzz_zzz1: pos = 3'b000;

8'bzzzz_zz1z: pos = 3'b001;

8'bzzzz_z1zz: pos = 3'b010;

8'bzzzz_1zzz: pos = 3'b011;

8'bzzz1_zzzz: pos = 3'b100;

8'bzz1z_zzzz: pos = 3'b101;

8'bz1zz_zzzz: pos = 3'b110;

8'b1zzz_zzzz: pos = 3'b111;

default: pos = 3'b000;

endcase

end

endmodule

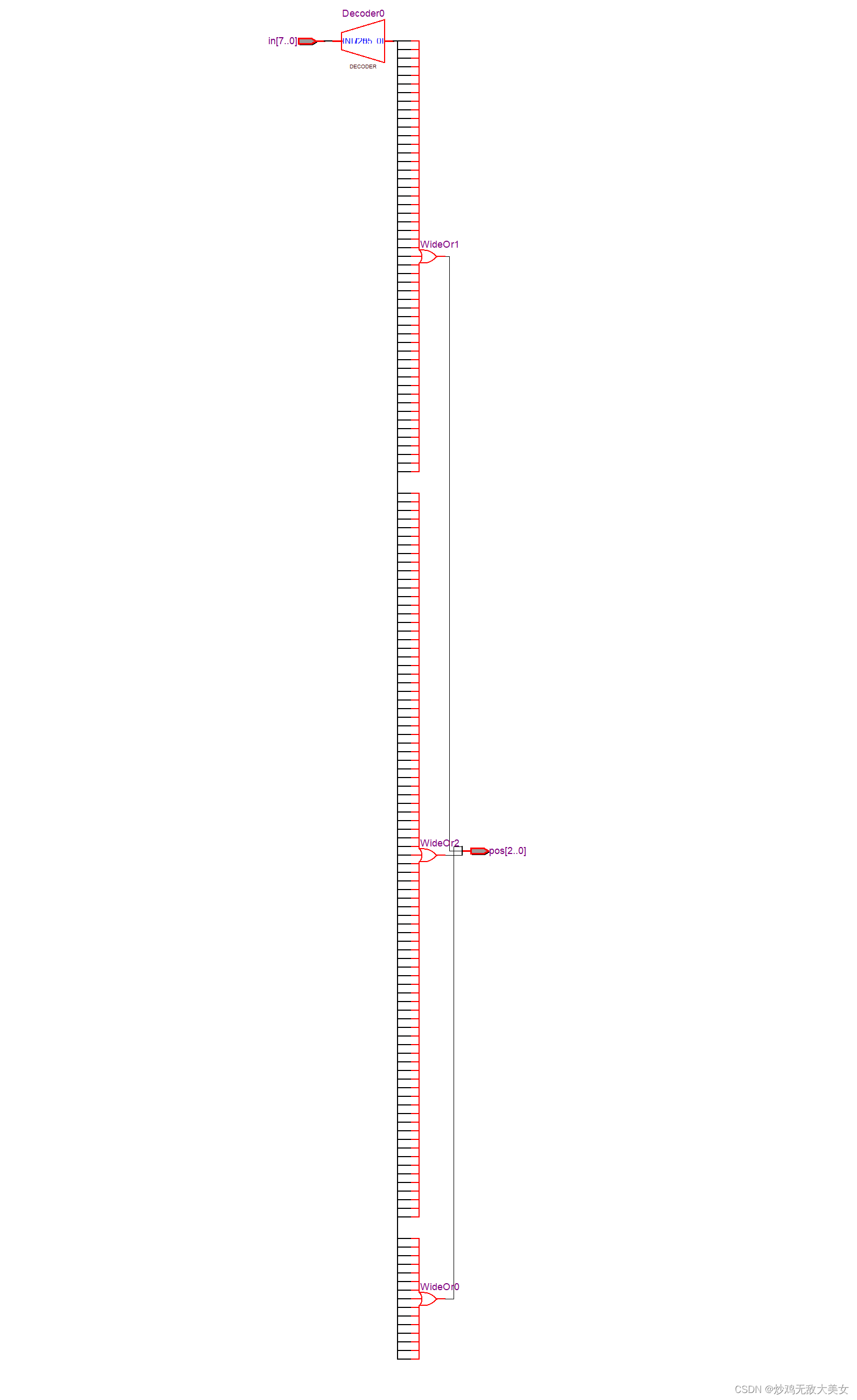

使用quartus ii画出逻辑图:

法2:使用case(1’b1)语句:

// synthesis verilog_input_version verilog_2001

module top_module (

input [7:0] in,

output reg [2:0] pos );

always@(*)

begin

case(1'b1)

in[0]: pos = 3'b000;

in[1]: pos = 3'b001;

in[2]: pos = 3'b010;

in[3]: pos = 3'b011;

in[4]: pos = 3'b100;

in[5]: pos = 3'b101;

in[6]: pos = 3'b110;

in[7]: pos = 3'b111;

default: pos = 3'b000;

endcase

end

endmodule使用quartus ii画出逻辑图:

对比学习笔记8:HDLBITS笔记8:4-2优先编码器_炒鸡无敌大美女的博客-CSDN博客可知:8-3优先编码器仅仅是在4-2优先编码器的基础上堆叠了输入和输出。

本文介绍了如何使用Verilog语言实现8-3位优先编码器,包括使用casez语句块和case(1'b1)语句的方法。案例中详细展示了不同输入下编码器的输出,并提供了Quartus II软件绘制的逻辑图。8-3优先编码器能够找到8位输入中最高位的1,并将其位置作为输出。

本文介绍了如何使用Verilog语言实现8-3位优先编码器,包括使用casez语句块和case(1'b1)语句的方法。案例中详细展示了不同输入下编码器的输出,并提供了Quartus II软件绘制的逻辑图。8-3优先编码器能够找到8位输入中最高位的1,并将其位置作为输出。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?