实验目的:

理解主存地址基本概念,理解存储位扩展基本思想,并能利用相关原理构建能同时支持字节、半字、字访问的存储子系统。

实验内容:

Logisim 中 RAM 组件只能提供固定的地址位宽,数据输出也只能提供固定的数据位宽,访问时无法同时支持字节/半字/字三种访问模式,实验要求利用4个8位的 RAM 组件进行扩展,设计完成既能按照8位、也能按16位、也能按照32位进行读写访问的32位存储器。

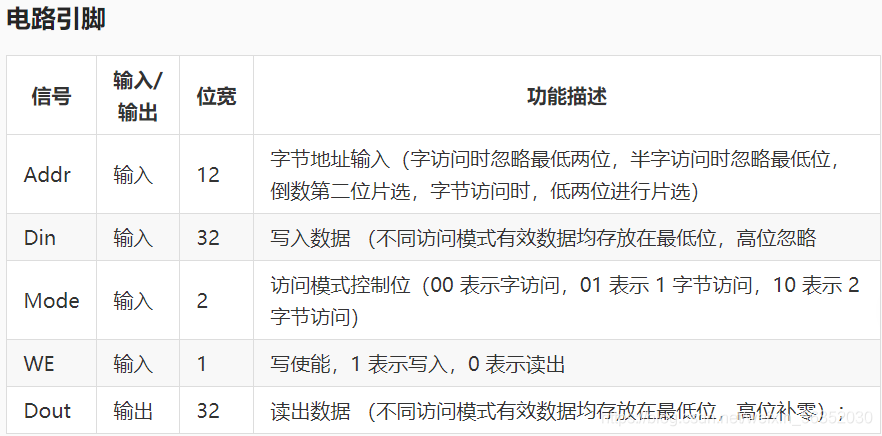

下面为电路输出引脚图:

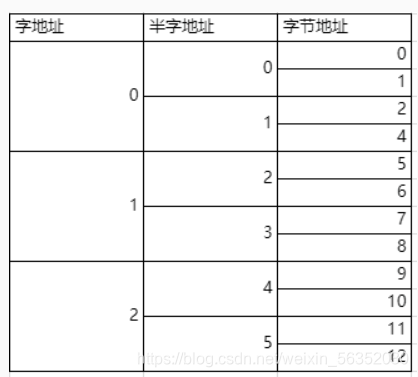

最终实现的地址空间如下图所示,字地址,半字地址,字节地址对应的存储空间是共享的。

实验步骤:

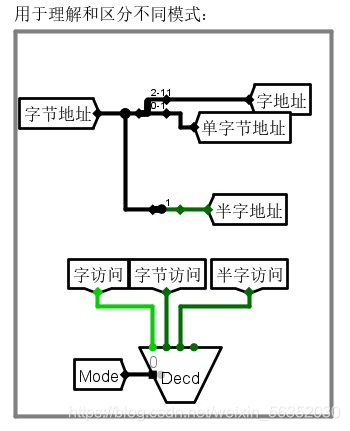

00 表示字访问,01 表示 1 字节访问 (即单字节访问),10 表示 2 字节访问 (即半字访问)。(在实验中 字32bit,单字节8bit,半字为16bit)

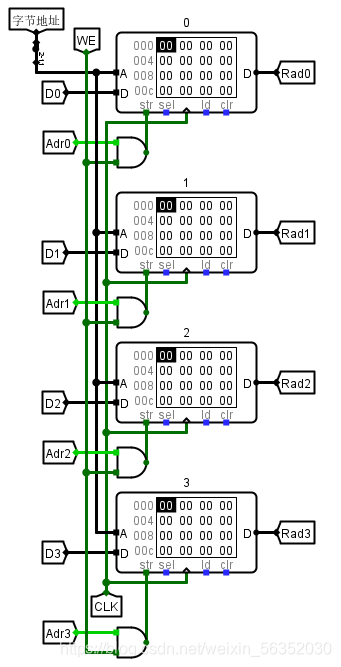

地址在字访问时忽略最低两位;半字访问时忽略最低位,倒数第二位为片选;字节访问时,第二位进行片选。

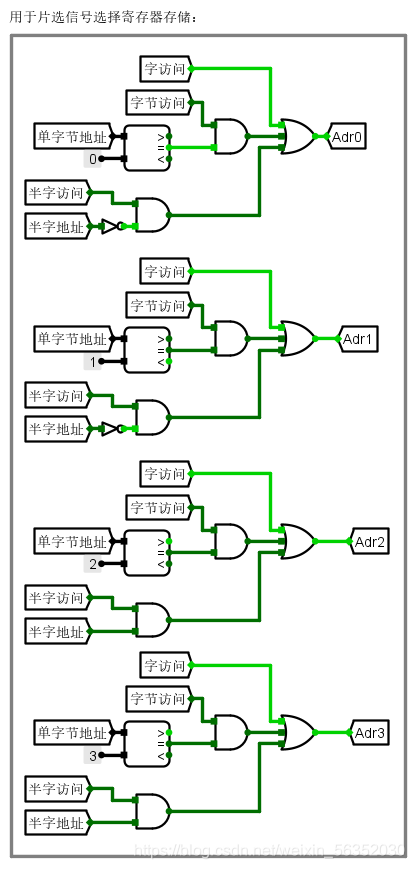

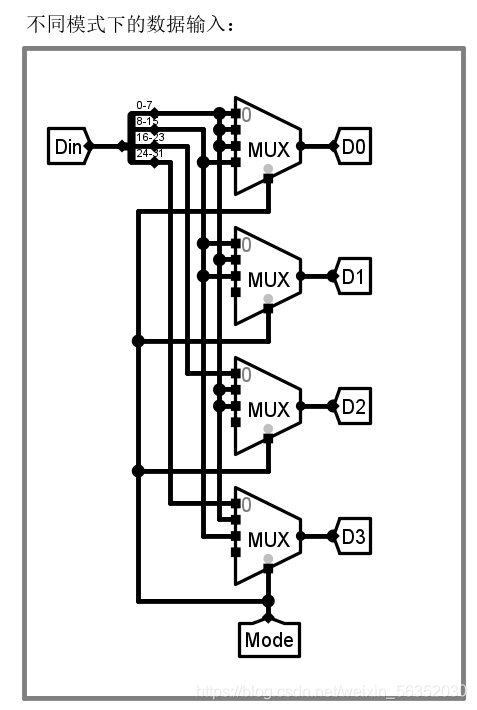

为了避免存储单元中的数据被覆盖,需要根据Mode和低二位决定4个存储器哪一个需要去存储。以最低位存储器的str信号来说,字访问的时候str为高电平;单字节访问的时候当片选信号为0才进行访问;半字访问的时候,片选信号为0时进行访问。

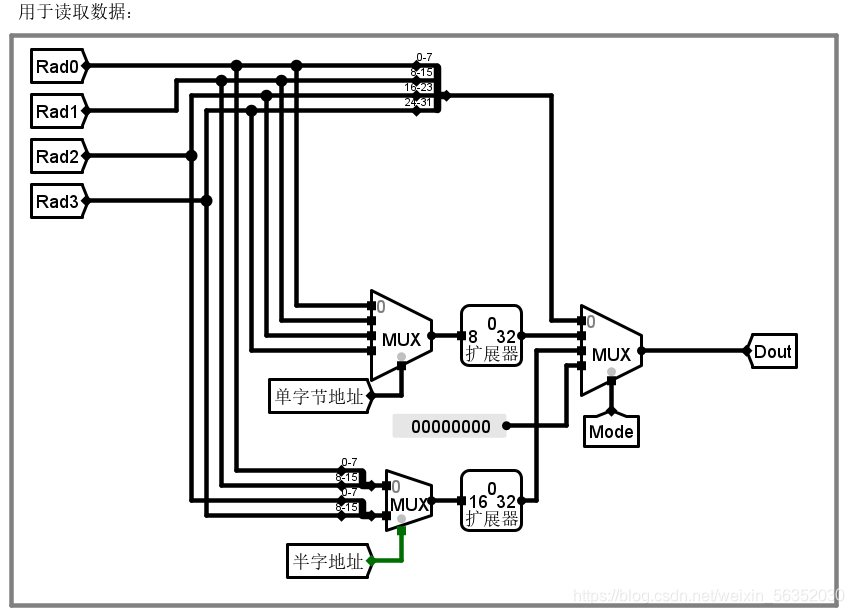

最后读取数据时,根据不同的地址访问来进行选择读取寄存器的内容:

电路完成图如下图所示:

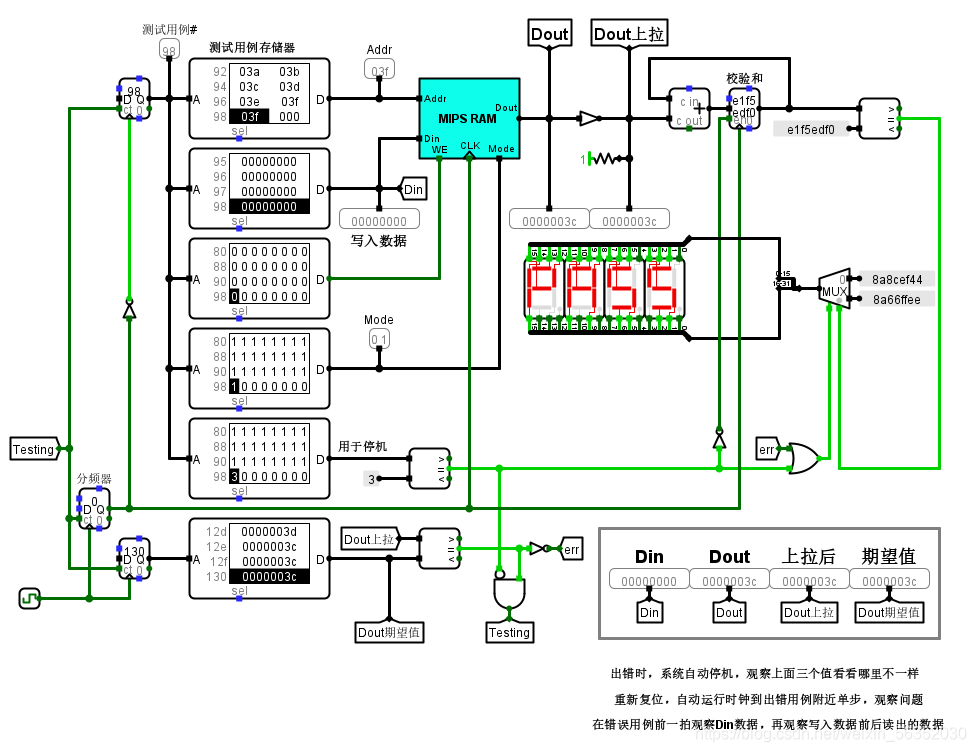

最后用实验里的自动测试库进行测试。

【理解不完善,有不当处请指出 】

469

469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?