一、为什么要满足建立时间和保持时间的要求呢?

要从触发器的结构来进行理解和说明:

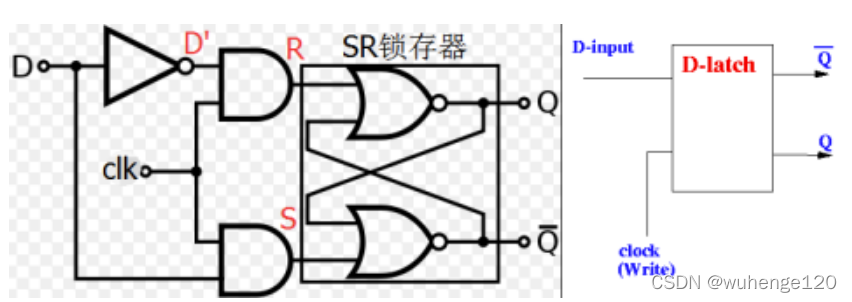

1)D锁存器结构如下: 特点:在clk为0时,R=S=0, 触发器输出为Q=0;

特点:在clk为0时,R=S=0, 触发器输出为Q=0;

在clk为1时,触发器输出为Q=D;

总结:在clk=1时,数据被锁存到Q端;

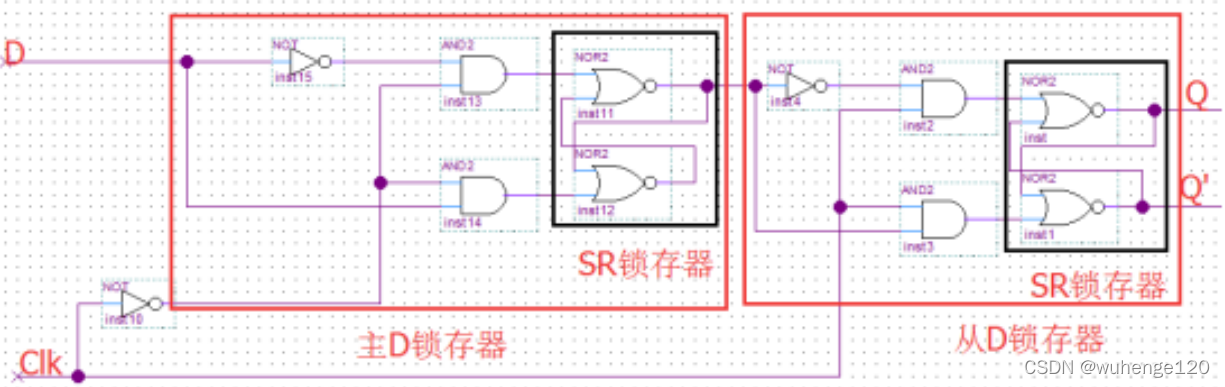

2)D触发器

clk = 0 时,主锁存器打开,数据D传入主锁存器输入端;

clk=0~1时,主锁存器关闭,从锁存器打开,并准备锁存数据;

clk=1时,主锁存器关闭,从锁存器所存数据;

clk=1~0时,从锁存器关闭,主锁存器打开开始锁数据;

clk=0时,主锁存器锁存数据;

总结:clk 从0~1时,整个触发器开始锁存数据,也叫正边沿触发器;

3)建立时间和保持时间的必要性

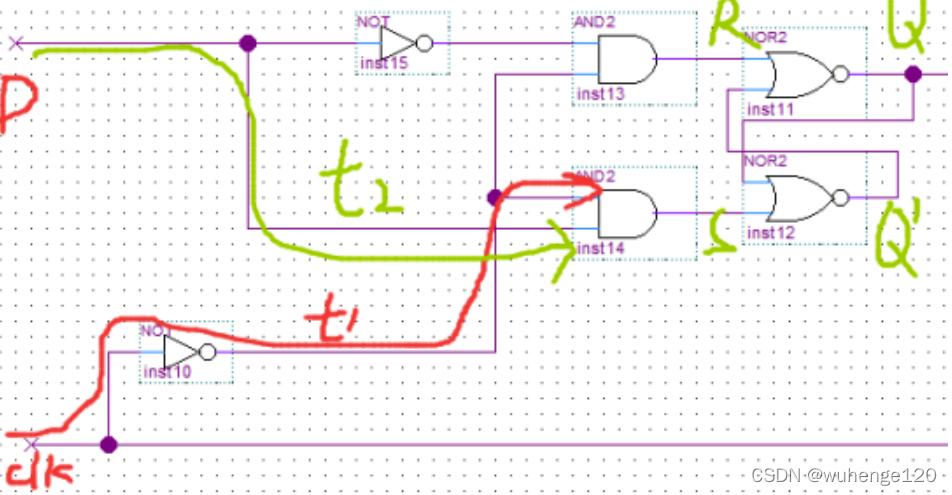

-->为什么要有建立时间?

如上图,在时钟上升沿,对于触发器来讲,主锁存器此时已经锁存数据D,并且从锁存器开始准备锁存数据。 由于主锁存器锁数据也是需要时间的,即在clk上升沿之前,clk=0的时候,主锁存器就开始锁存数据了(数据从D到主锁存器的输出需要时间),所以要有建立时间(即clk上升沿之前数据保持稳定的时间);

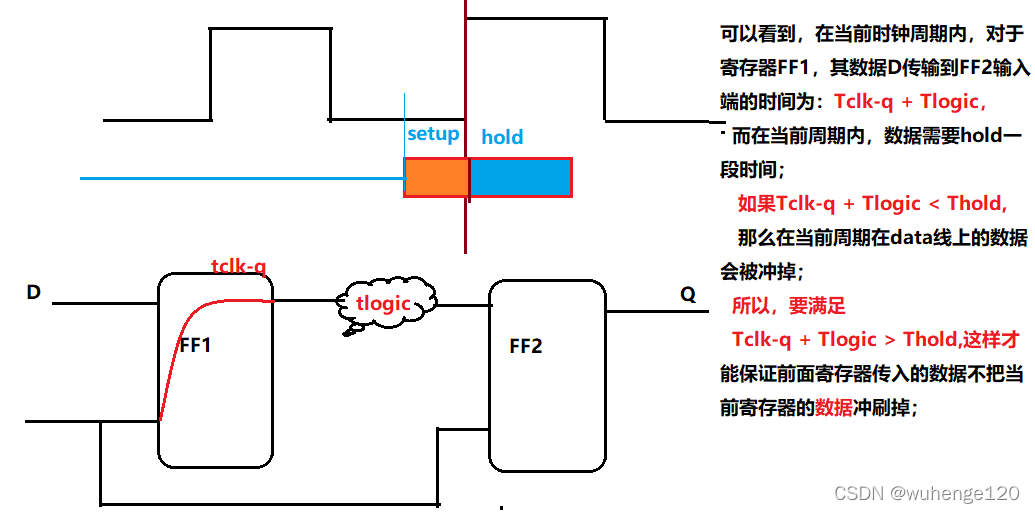

-->为什么要有保持时间?

如下图所示,在clk 从0~1 上升沿变化时,此时AND2 门的输入需要t1时间才会变成1,即需要t1时间才会开始锁存数据D;

如果在上升沿时,数据突然变化(即不满足保持时间要求),那么此时如果D需要在t2时间传到与门AND2处,如果t2 < t1, 那么主锁存器锁存的数据将是数据D变化后的值;所以,clk上升沿后数据需要保持一段时间;

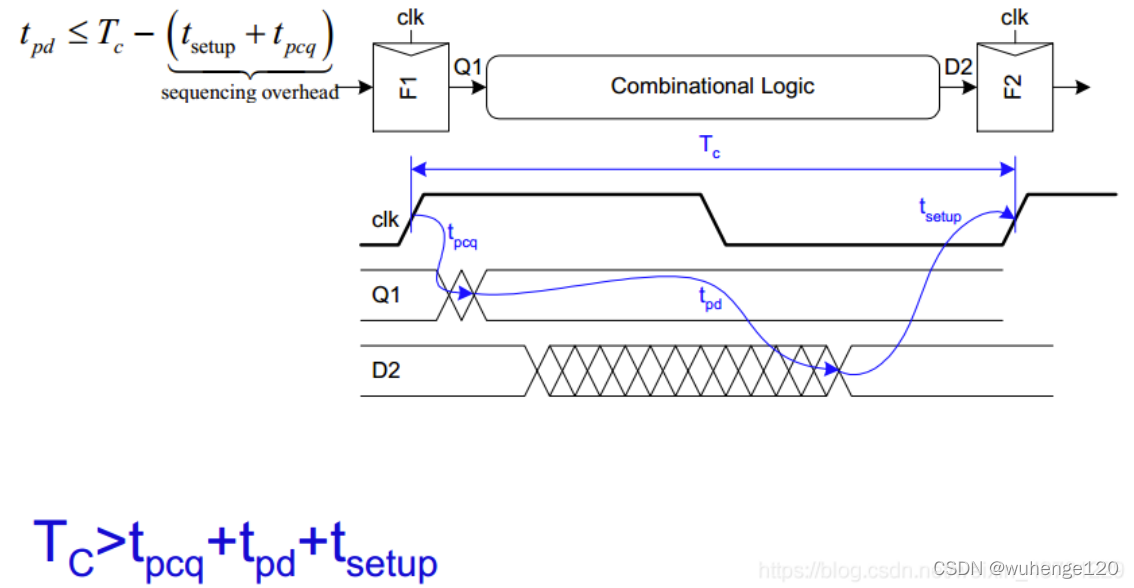

二、组合逻辑延时信息

1)最大延时

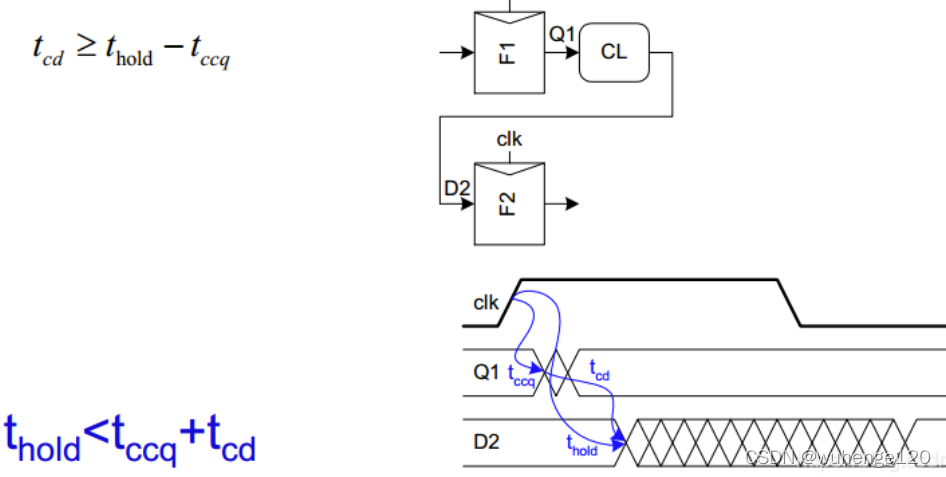

2)组合逻辑最小延时

之前理解最小延时的时候,比较困难,进一步梳理和hold time的关系,如下:

从而能够计算得到组合延时的最大最小时间;

6229

6229

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?