ARM Cortex-M0 异常与中断

-

异常类型及编号

Cortex-M0的每个异常源都有一个单独的编号:

1~15内部系统异常:Reset(1), NMI(2), H/W Error(3), SVC(11), PndSV(14), SysTick(15)其他编号未用;

16~47外部中断: IRQ#0~IRQ#31. -

异常优先级 (Cortex-M0 支持7个)

1). Cortex-M0 支持3个固定的最高优先级(Reset(-3), NMI(-2), H/W Error(-1))和4个可编程优先级;

2). 可编程寄存器有8bit宽,但只有Bit7和Bit6可配置,其余Bits为0. (优先级由高到低:0x00,0x40,0x80,0xC0);

3). 如果两个同时发生的异常的优先级相同,则先执行异常编号小的。(IRQ#0,IRQ#1 则先执行IRQ#0) -

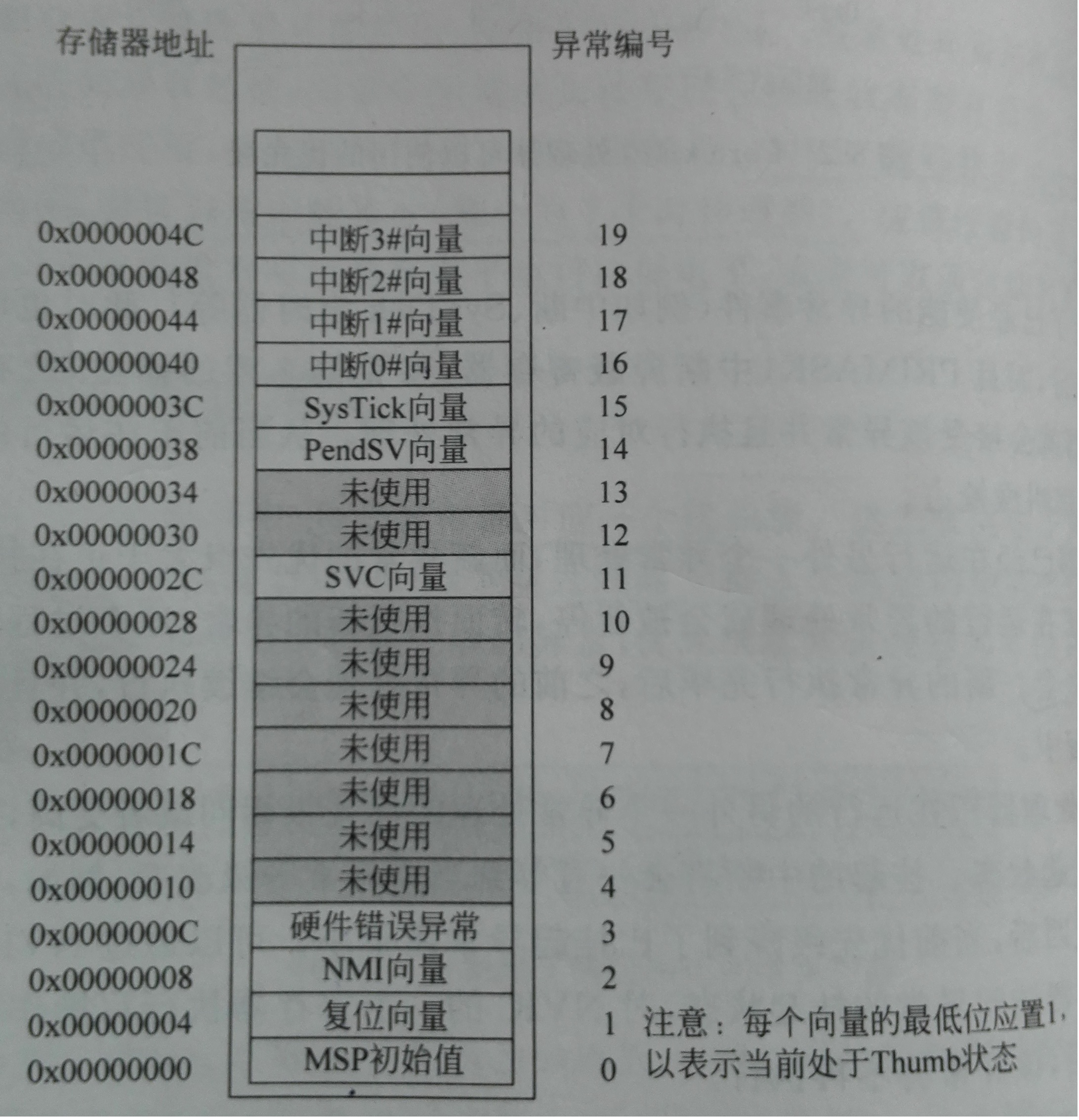

向量表(异常处理所需的起始地址信息)

异常向量的地址为异常编号乘以4(Reset向量的地址为:1*4=0x00000004),其他向量地址如下图所示: -

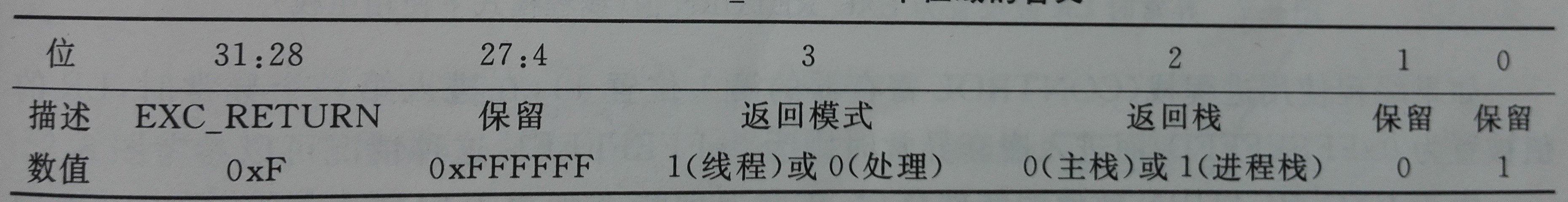

EXC_RETURN(32Bits)

该值用于异常返回机制,下图是其位域的含义:3个合法值:

0xFFFFFFF1 返回处理模式(嵌套异常发生的情况)

0xFFFFFFF9 返回线程模式并在返回中使用主栈(MSP);

0xFFFFFFFD 返回线程模式并在返回中使用进程栈(PSP); -

异常的流程

接受异常请求:

1) 中断和SysTick中断使能;

2) 未被NMI屏蔽掉;

3) 异常优先级大于当前执行的异常优先级。压栈及相关寄存器更新:

1) 压栈并更新栈指针(8个registers被压栈:R0~R3, R12, R14/LR, R15/PC, xPSR);

2) 取出异常向量写入PC中;

3) 3个寄存器更新(LR<–EXC_RETURN, IPSR<–异常编号, NVIC<– 对应的中断控制和状态)执行异常处理:

1) 自动定位异常向量,并处理;

2) 利用EXC_TURN的值来触发异常返回机制。异常退出:

1) 寄存器出栈;

2) 恢复返回地址,并执行异常前程序。 -

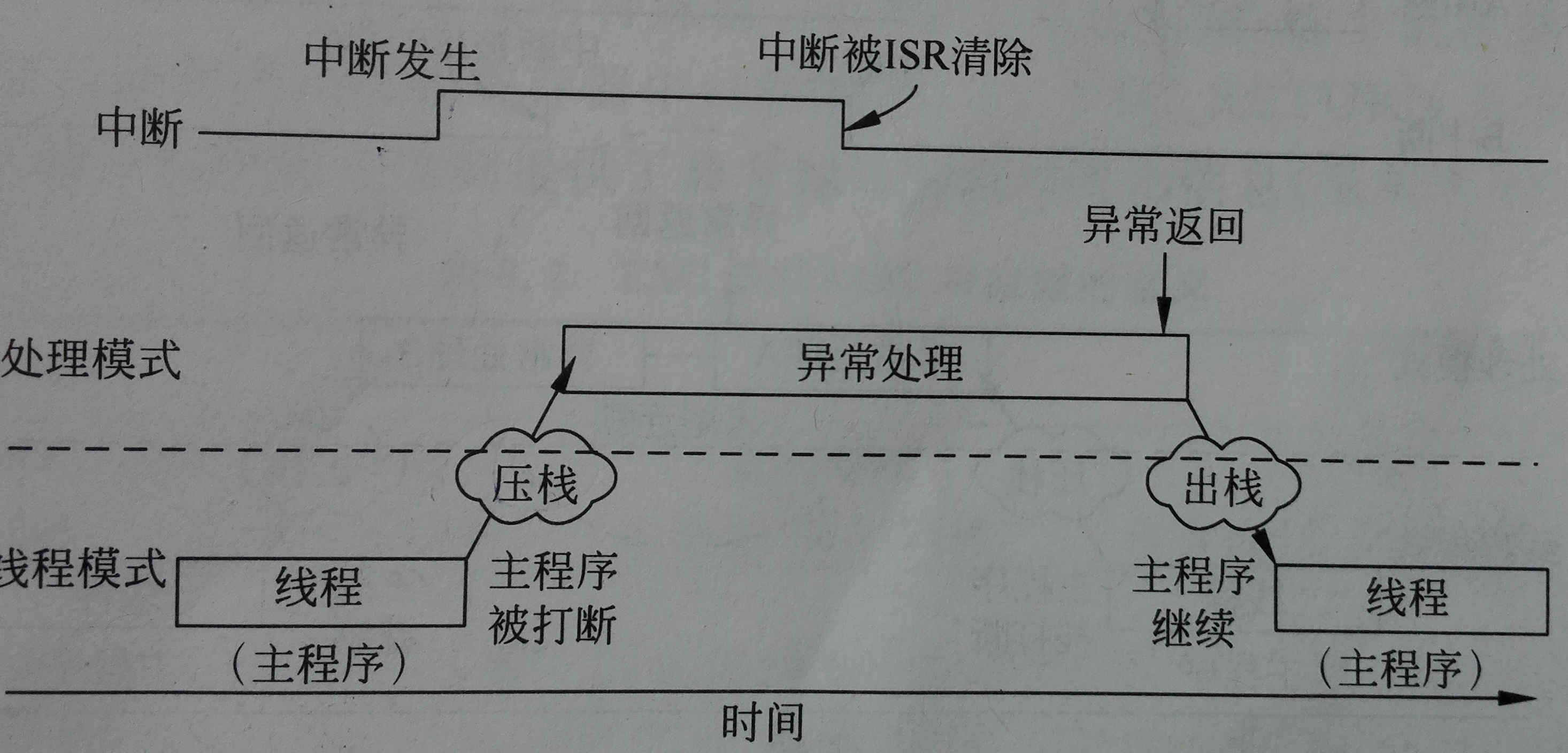

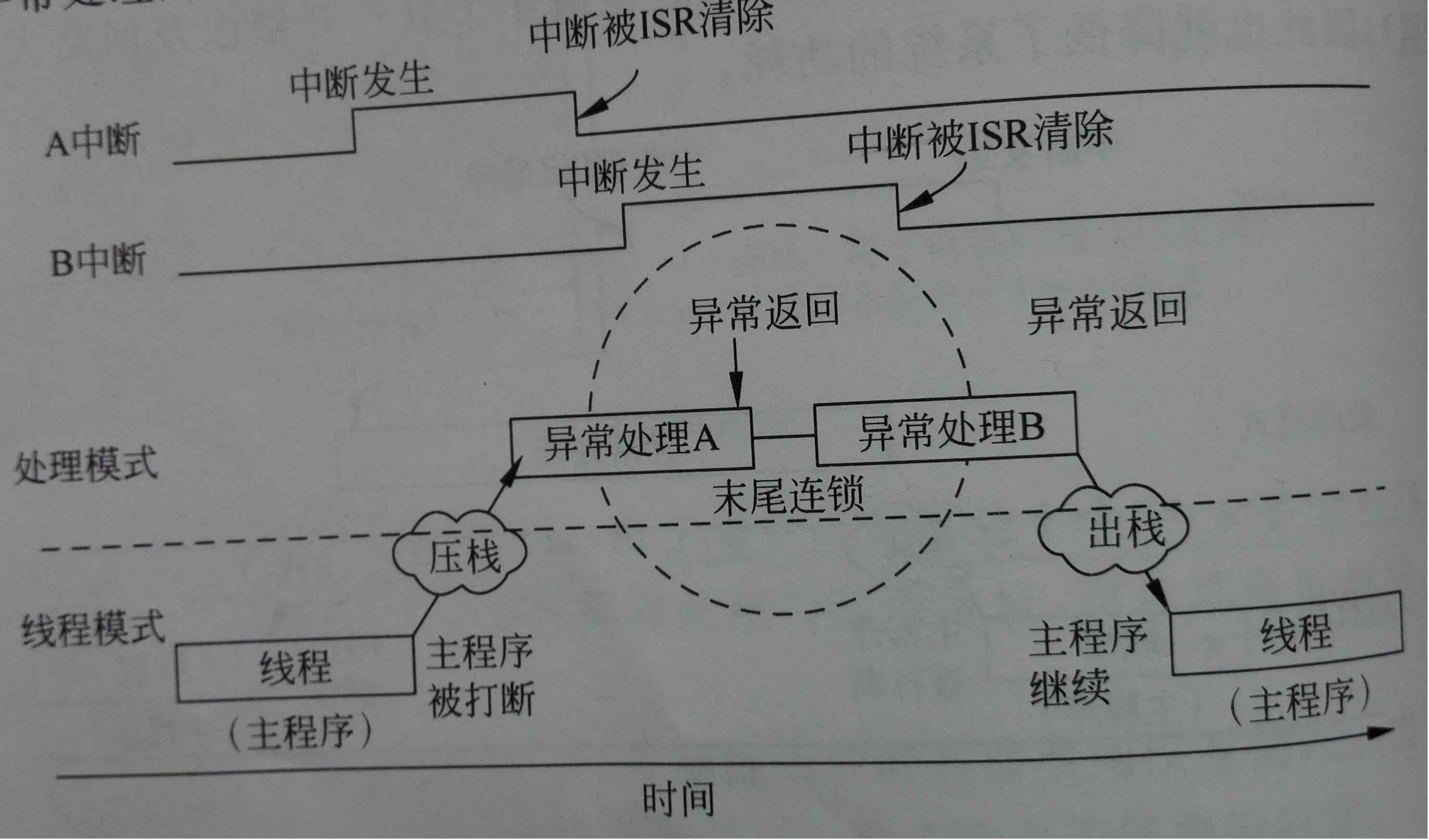

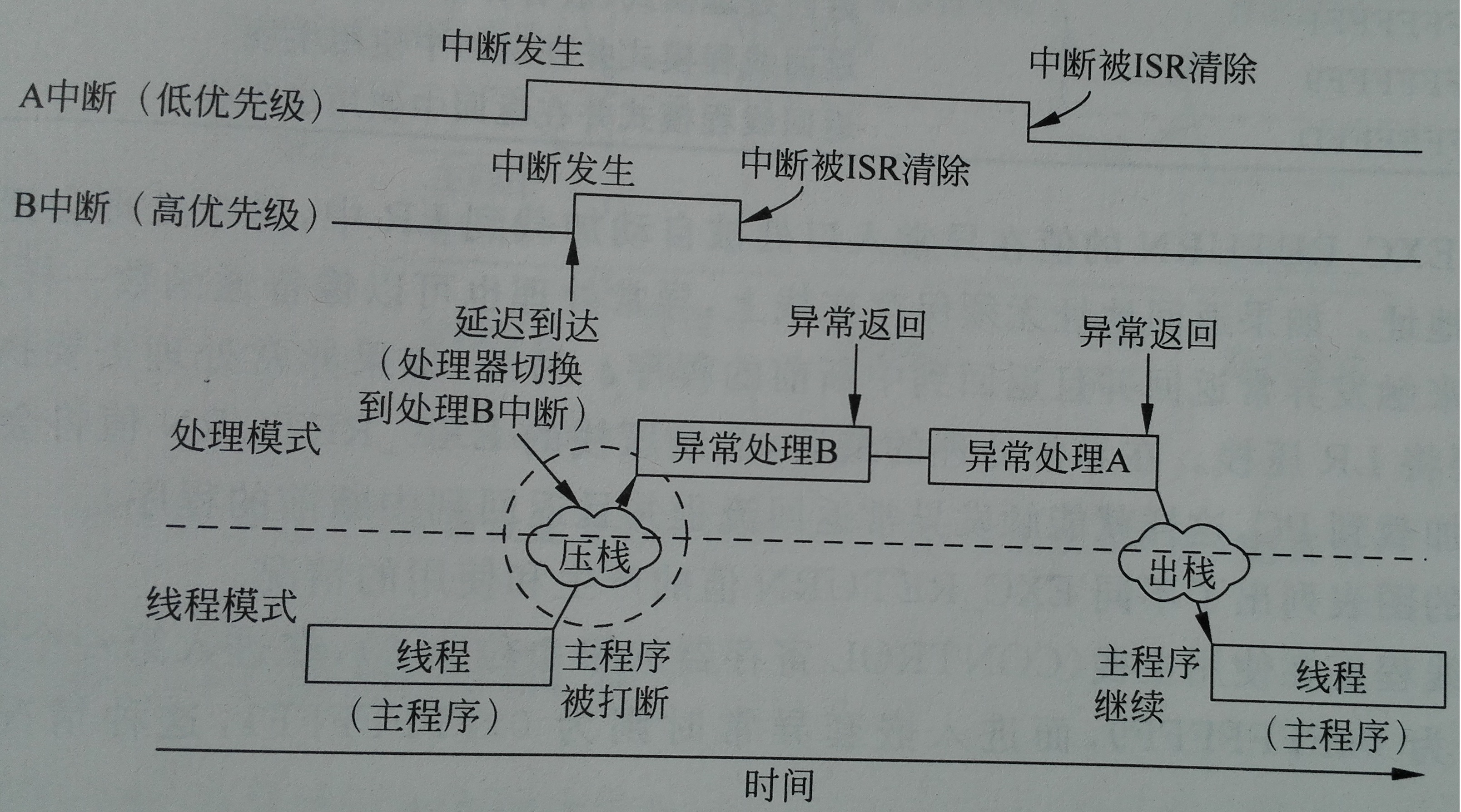

3种主要的异常及其机制:(单异常,末尾连锁,延迟到达)

1)单异常2)末尾连锁

3)延迟到达

1426

1426

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?