一、SATA物理层概述

说OOB之前,首先得了解一下SATA结构以及物理层的含义。

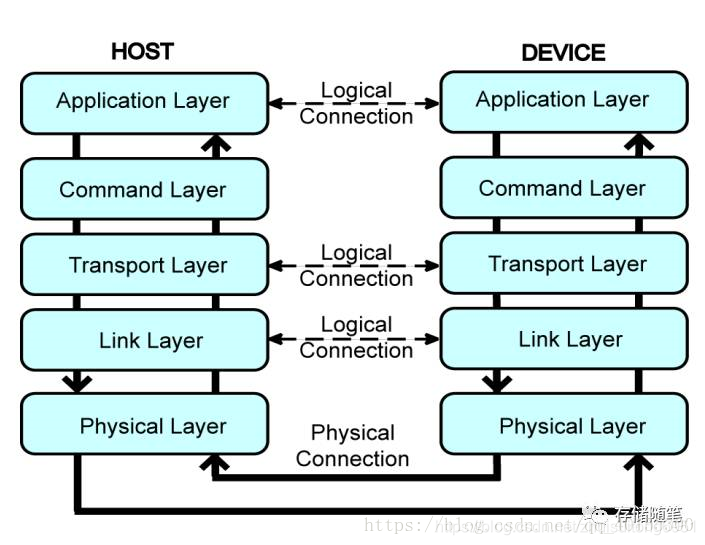

SATA主要包括:应用层(Application Layer), 传输层(Transport Layer),链路层(Link Layer)以及物理层(Physical Layer), SATA结构如下图:

这四个主要部分的作用是什么呢?

Application Layer/Command Layer(可解读为同一层) :

-

最高层级的Layer,进行ATA或ATAPI command的执行,

-

implementation上很多是用软件处理.

Transport Layer :

-

将Application Layer要做的Command转化成FIS的handshake,

-

对FIS的组成和解开.

Link Layer :

-

将要打出去的data做编码, 将收进来的data做解码,

-

维持Link Layer的handshake机制.

Physical Layer :

-

Tx和Rx串行流(serial stream),

-

上电时序,

-

支持SATA电源管理选项,

-

OOB(Out-of-Band)信号的产生与检测.

从上面的介绍中,我们看到物理层中有一个关键的功能就是OOB(Out-of-Band)信号的产生与检测, 这就是我们今天的主角~

二、OOB(Out of Band)信号解析

SATA信号链结的建立主要是靠OOB(Out Of Band)的检测实现的,并且向上层Link Layer提供了物理层的链结情况。

OOB主要的作用包括以下几点:

初始化(initialization),

传输速率的协商与对接(Speed negotiation),

—透过OOB handshake,host与device可以决定要在Gen1,Gen2或Gen3做data传输。

重置(Reset),

从省电状态(Slumer/Partial)的唤醒,

OOB信号实际上主要有COMRESET/COMINIT与COMWAKE三个PHY信号线。

1、COMRESET:Host对Device进行硬件重置以及SATA信号的重新建立。

2、COMINIT:由Device送往Host,要求信号初始化。

3、COMWAKE:Host或是Device装置可以激发该信号来将PHY从省电状态(Slumer/Partial)抽离。

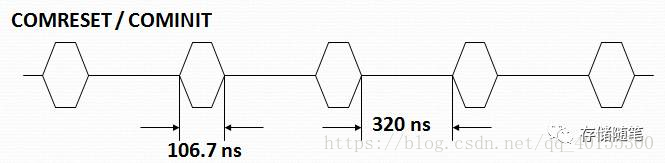

COMRESET/COMINIT由两部分相互间隔构成,一部分是突发长度为160个UI (Unit Interval)约106.7ns的ALIGN,另一部分是长度为480UI约320ns的Idle。

需要注意的是,虽然COMREST和COMINIT形式上是一样的,但COMREST只能从host到device,而COMINIT只能从device到host。

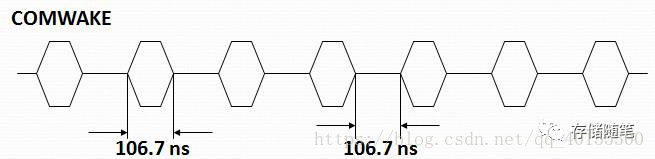

COMWAKE同样是有两部分相互间隔组成,一部分是突发长度为160个UI (Unit Interval)约106.7ns的ALIGN,另一部分是长度为160个UI约106.7ns的Idle。

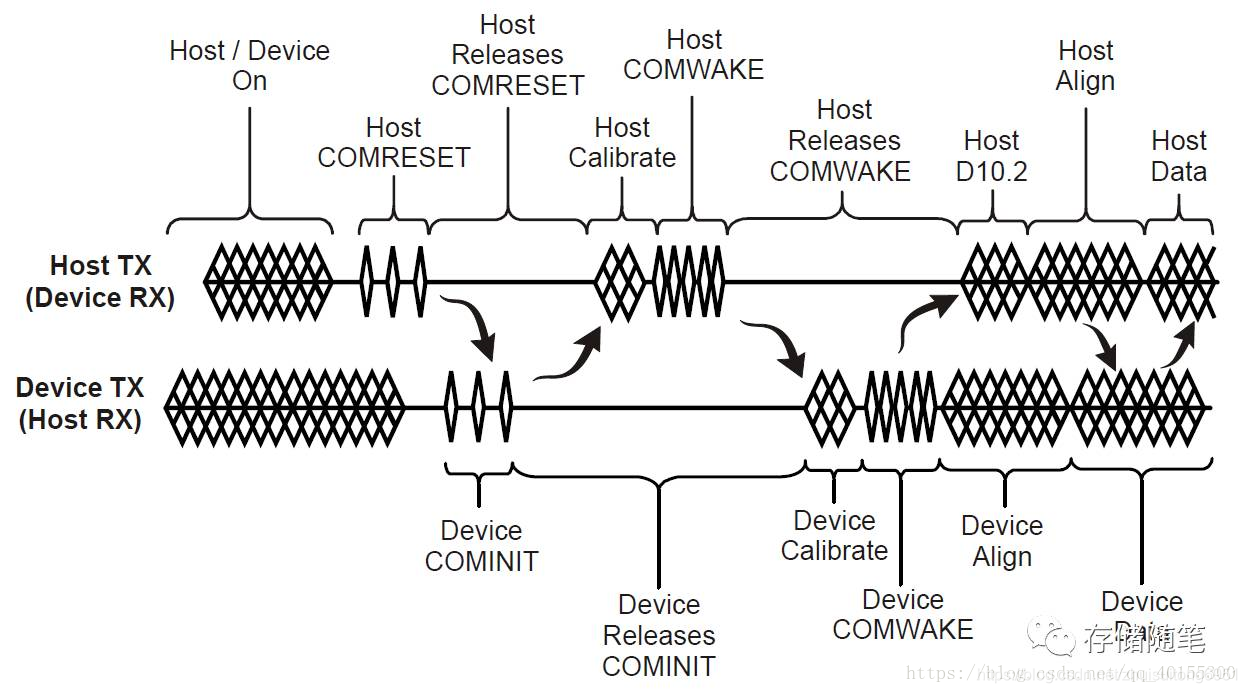

SATA信号通迅链结建立过程是什么?我们先来看一幅图哈~

看不懂?没关系,我们一步步的来解析一下详细的过程:

1、主机重置,发出COMREST。

2、设备检测到COMRESET后以COMINIT回应。

—COMINIT为重新连接开始信号,设备可以在任意时间发送COMINIT重新建立连接。

3、若没有COMINIT的通知,HOST就会重复步骤1,直到DEVICE回复为止,这也是系统允许热插拔的关键。

4、主机calibrate,发出COMWAKE。

5、设备接收到COMWAKE后,设备连续发送6个COMWAKE信号,接着连续发送ALIGN进行传送速度的协商。

6、主机锁存资料。主机接收到COMWAKE后,以支援的最低速率连续发送D10.2资料,同时锁存检测接收的资料,当检测到设备发送的ALIGN后,以接收的速率将ALIGN转发给设备。

注:D10.2是0101010101…这样0和1交替的波形, 可以让device端更容易做clock recovery的动作.

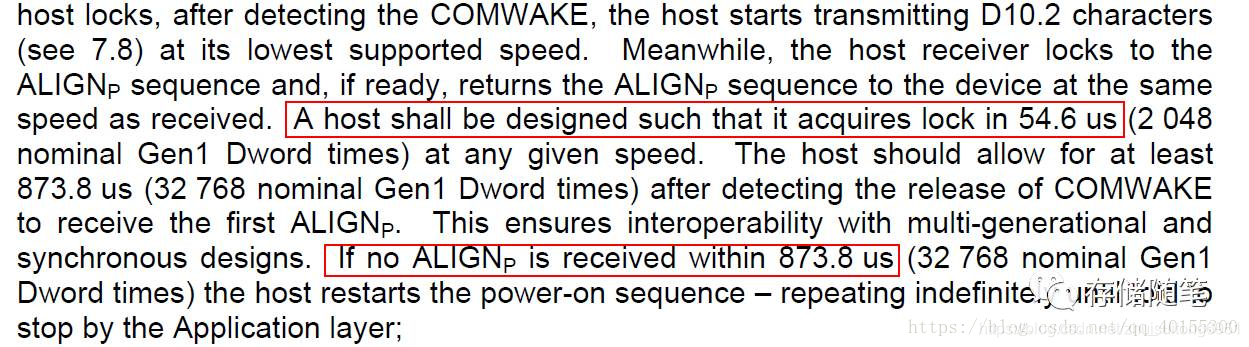

7、主机在发送了COMWAKE后至少要在880ps内接检测到ALIGN,否则主机重启上电序列重新检测设备,直到应用层将其终止。

8、设备锁存资料,检测到ALIGN后发送同步信号SYNC,通讯建立成功,进入到正常操作模式。如在54.6us内未检测到ALlGN,则进入错误处理,等待重新连接。

9、当主机接收到三个非ALIGN后,链结建立完成,进入正常操作。

Device与Host连接是首先从Device支持的最高速开始的,如果最高速不满足则用较低速率再次匹配,直到最低速率也不能匹配后Device将进入error状态; 换速等待时间为54.6us(2048个ALIGN DWORD传输时间);

三、实例分享

我们来看个小编工作中遇到的一个实例–fail现象是正常上电之后SATA SSD无法被识别。

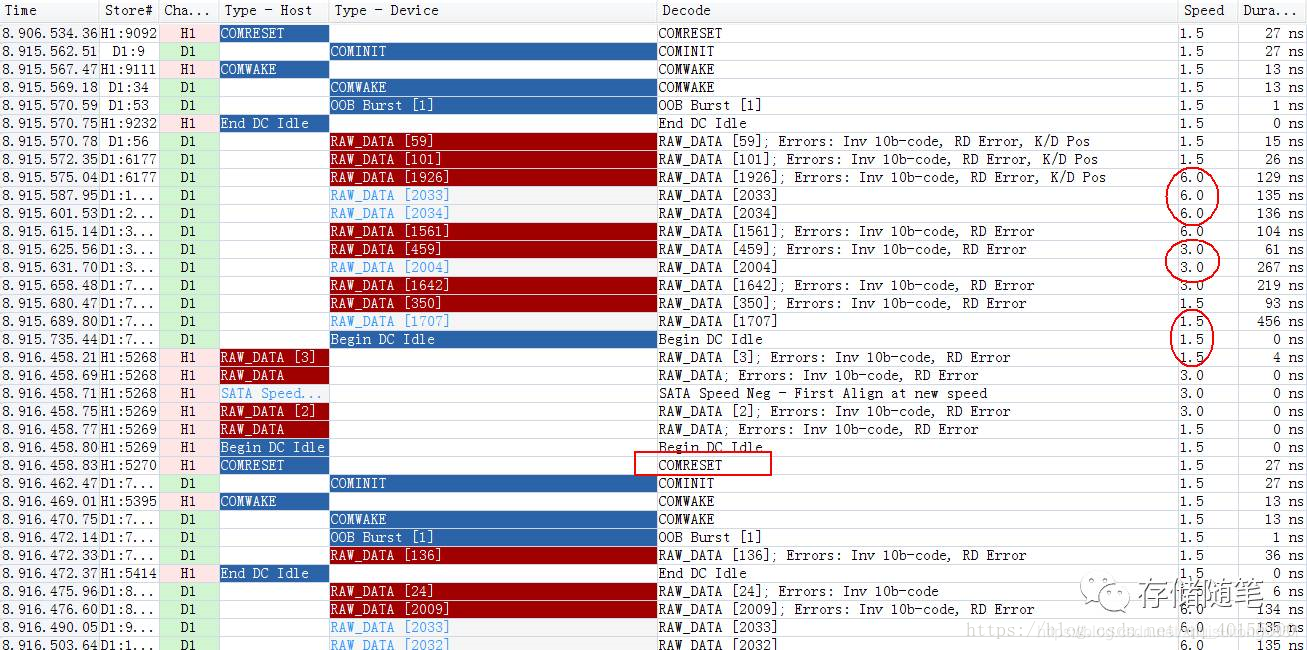

抓取正常上电之后fail sample SATA trace如下:

从上面的SATA trace结合前面SATA通讯链路建立的9个步骤,我们可以发现第六步之后就出问题了:

Device传送最高速度(6.0G)的Align无法顺利被SATA analyzer解析出来,再降速送Align(3.0G, 1.5G)依然无法被SATA analyzer解析, host也没有回应, speed negotiation失败。最终,Host再次发送COMRESET,进入死循环。

正是由于SATA信号通讯链路无法建立,导致SATA SSD在上电之后始终无法被识别到。

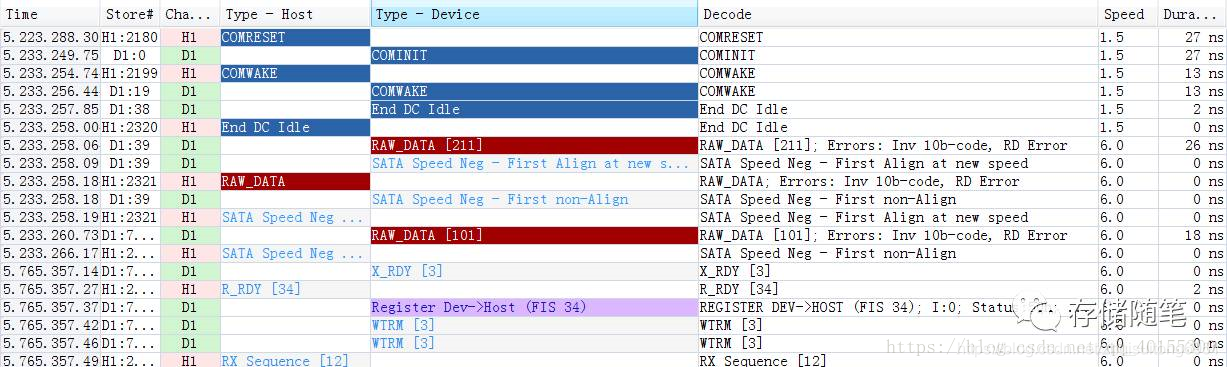

最后附上SSD可以被正确识别的SATA trace供各位看官参考:

2843

2843

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?