3.5 外设中断

本节解释器件的外设中断处理。不可屏蔽中断在 3.6 节介绍。软件中断和仿真中断不在本文档讨论范围内,有关这些内容,请参见《TMS320C28x CPU 和指令集参考指南》。

3.5.1 中断概念

中断是一种信号,它会使 CPU 暂停当前执行的程序,并跳转到称为中断服务程序(ISR)的不同代码段。这是一种处理外设事件的有用机制,与寄存器轮询相比,它涉及的 CPU 开销和程序复杂度更低。然而,由于中断是异步于程序流的,必须采取措施避免在中断和主程序代码中都访问的资源发生冲突。

中断通过一系列标志和使能寄存器传递到 CPU。标志寄存器存储中断,直到中断被处理。使能寄存器阻止中断的传递。当中断信号到达 CPU 时,CPU 从一个称为向量表的列表中获取相应的 ISR 地址。

3.5.2 中断架构

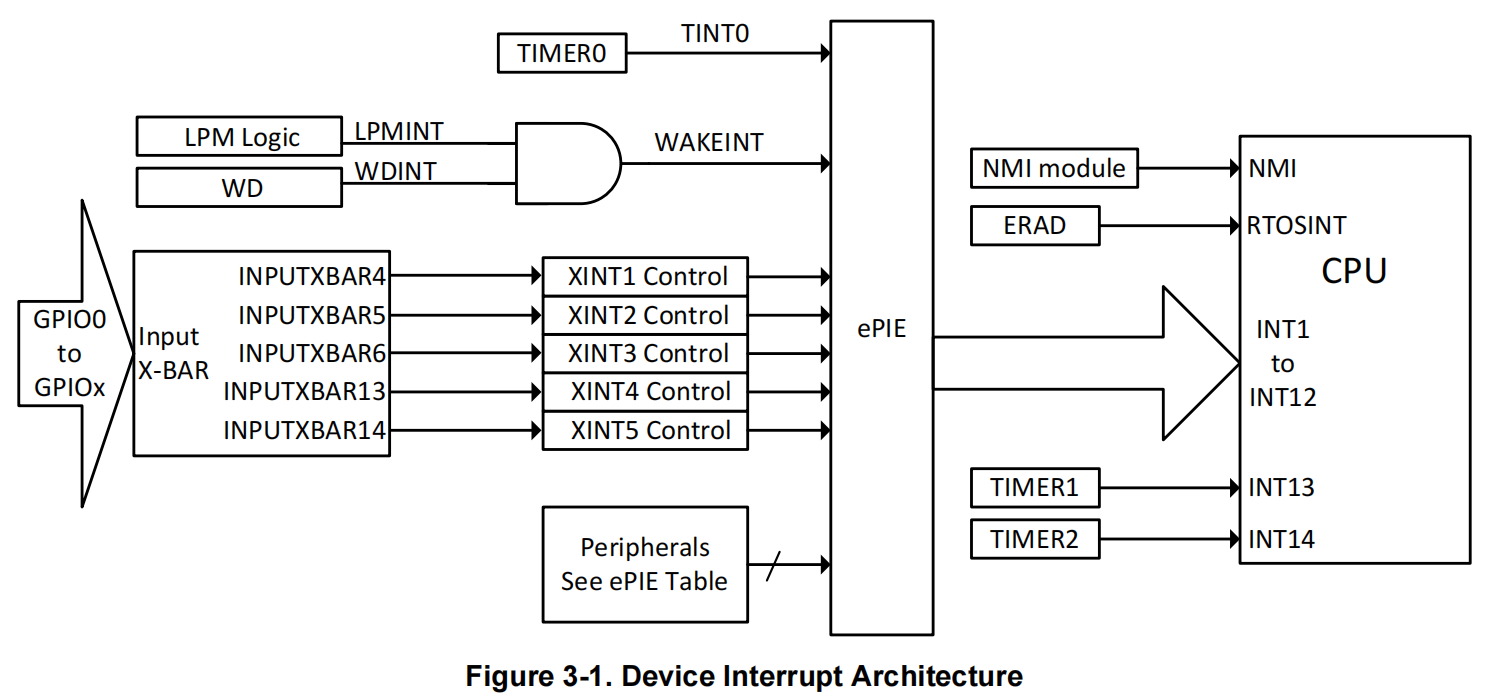

C28x CPU 有 14 条外设中断线。其中两条(INT13 和 INT14)分别直接连接到 CPU 定时器 1 和 2。其余 12 条通过增强型外设中断扩展模块(ePIE,或简称为 PIE)连接到外设中断信号。PIE 将最多 16 个外设中断复用到每条 CPU 中断线上,还扩展了向量表,使每个中断都能有一个 ISR。这允许 CPU 支持大量外设。

中断路径分为三个阶段 —— 外设、PIE 和 CPU。每个阶段都有使能和标志寄存器。该系统允许 CPU 在其他中断处于挂起状态时处理一个中断,在软件中实现和优先处理嵌套中断,并在某些关键任务期间禁用中断。

图 3 - 1 展示了该器件的中断架构。

3.5.2.1 外设阶段

每个外设都有独特的中断配置,这在该外设对应的章节中有描述。一些外设允许多个事件触发同一个中断信号。例如,一个通信外设可以使用同一个中断来表示数据已接收或发生了传输错误。中断的原因可通过读取外设的状态寄存器来确定。通常,在生成另一个中断之前,必须手动清除状态寄存器中的相关位。

3.5.2.2 PIE 阶段

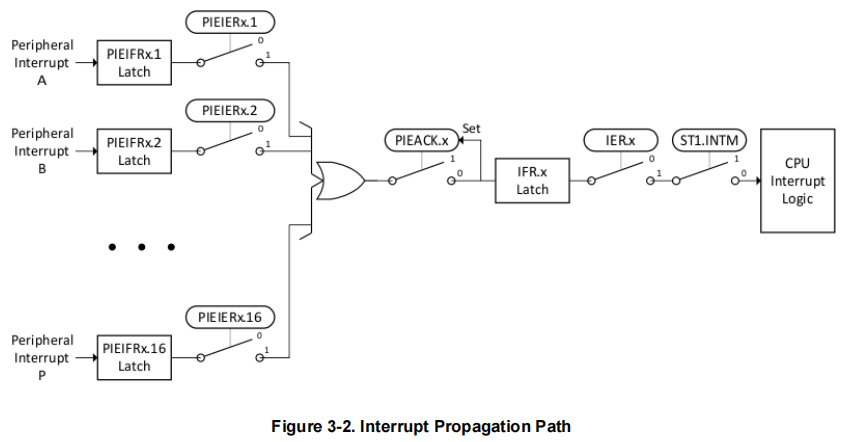

PIE 为每个外设中断信号提供单独的标志和使能寄存器位,这些也被称为 PIE 通道。这些通道根据相关的 CPU 中断进行分组。每个 PIE 组有一个 16 位的使能寄存器(PIEIERx)、一个 16 位的标志寄存器(PIEIFRx),以及 PIE 确认寄存器(PIEACK)中的一位。PIEACK 寄存器中的位作为整个 PIE 组的公共中断掩码。

当 CPU 接收到一个中断时,CPU 从 PIE 获取 ISR(中断服务程序)的地址。PIE 会返回组内编号最小且同时被置标志和使能的通道的向量。这使得当多个中断挂起时,编号较小的中断具有更高的优先级。

如果没有中断同时被置标志和使能,PIE 会返回通道 1 的向量。这种情况只有在中断传播过程中软件修改了 PIE 的状态时才会发生。3.5.4 节包含了在中断使能后安全修改 PIE 配置的步骤。

3.5.2.3 CPU 阶段

与 PIE 类似,CPU 为每个中断提供标志和使能寄存器位。有一个使能寄存器(IER)和一个标志寄存器(IFR),它们都是 CPU 的内部寄存器。还有一个全局中断掩码,由 ST1 寄存器中的 INTM 位控制。这个掩码可以使用 CPU 的 SETC 和 CLRC 指令来置位和清除。在 C 代码中,可以使用 C2000Ware 的 DINT 和 EINT 宏来实现这一目的。

对 IER 和 INTM 的写入是原子操作。特别是,如果 INTM 被置位,流水线中的下一条指令会在中断禁用的情况下运行,无需软件延迟。

3.5.3 中断进入序列

图 3 - 2 展示了外设中断是如何传递到 CPU 的。

当外设产生

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

590

590

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?