摘要

本文叙述了在高通平台LK阶段读取mpp2引脚电平的实现过程,附上实现代码。主要实现过程包括配置引脚功能,读取引脚电压。需要特别注意配置mpp2通道和AIN route的选择。

需要修改的文件:

bootable\bootloader\lk\app\aboot\aboot.c

Pm8x41_adc.c (dev\pmic\pm8x41)

Pm8x41_adc.h (dev\pmic\pm8x41\include)

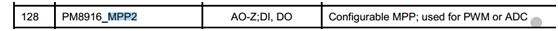

PM8916 MPP2引脚说明

可以看出

MPP2引脚具有ADC输入的功能。

修改过程及例子

在使用mpp2

引脚之前需要配置这个引脚为ADC

功能,在LK

阶段提供了一个操作函数,在Pm8x41_adc.c (dev\pmic\pm8x41)

中实现。

/*

* API: pm8x41_enable_mpp_as_adc

* Configurate the MPP pin as the ADC feature.

*/

void

pm8x41_enable_mpp_as_adc(uint16_t mpp_num)

注意:mpp2

的mpp_num

值为0x01

!

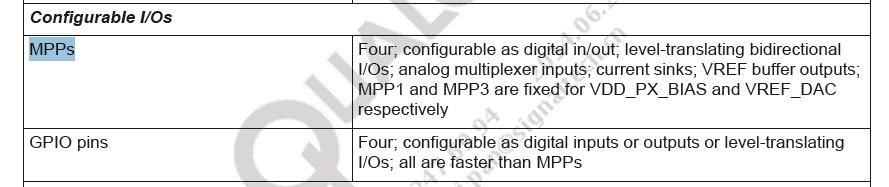

使用pm8x41_adc_channel_read(mpp2_chan);读取该引脚ADC采样得到的电压值

另外

mpp2_chan

的值是33(0x21)

!

这个通道号是根据这个寄存器

VADC1_LC_USR_ADC_CH_SEL_CTL

来的:

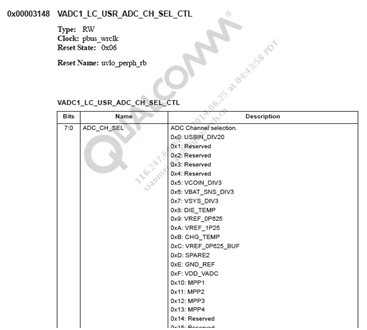

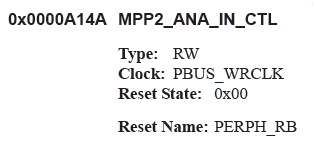

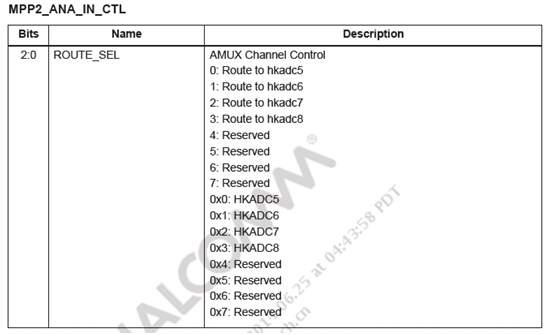

在配置引脚的地方有一个

选择ADC

输入路线选择的地方,根据寄存器信息可知道这里可以选择AMUX5-8!

下面是需要修改的代码:

\bootable\bootloader\lk\app\aboot\aboot.c

void adc_test_selc_lcm()

{

uint32_t vadc_chan3;

uint16_t mpp2_chan = 33;

/*

* TEST: Read the voltage on batt_id & vbat_sns channels

*/

pm8x41_enable_mpp_as_adc_for_mpp2(1);

vadc_chan3 = pm8x41_adc_channel_read(mpp2_chan);

dprintf(INFO, "The channel [%d] voltage is :%d\n",mpp2_chan, vadc_chan3);

}

void aboot_init(const struct app_descriptor *app)

{

……

adc_test_selc_lcm();

……

}

Pm8x41_adc.c (dev\pmic\pm8x41)

/*

* This is the predefined adc configuration values for the supported

* channels

*/

static struct adc_conf adc_data[] = {

CHAN_INIT(VADC_USR1_BASE, VADC_BAT_CHAN_ID, VADC_MODE_NORMAL, VADC_DECIM_RATIO_VAL, HW_SET_DELAY_100US, FAST_AVG_SAMP_1, CALIB_RATIO),

CHAN_INIT(VADC_USR1_BASE, VADC_BAT_VOL_CHAN_ID, VADC_MODE_NORMAL, VADC_DECIM_RATIO_VAL, HW_SET_DELAY_100US, FAST_AVG_SAMP_1, CALIB_ABS),

CHAN_INIT(VADC_USR1_BASE, MPP_8_CHAN_ID, VADC_MODE_NORMAL, VADC_DECIM_RATIO_VAL, HW_SET_DELAY_100US, FAST_AVG_SAMP_1, CALIB_ABS),

CHAN_INIT(VADC_USR1_BASE, MPP_2_CHAN_ID, VADC_MODE_NORMAL, VADC_DECIM_RATIO_VAL, HW_SET_DELAY_100US, FAST_AVG_SAMP_1, CALIB_ABS),

};

void pm8x41_enable_mpp_as_adc_for_mpp2(uint16_t mpp_num)

{

uint32_t val;

if(mpp_num >MPP_MAX_NUM)

{dprintf(CRITICAL,"Error: The MPP pin number is unavailable\n");

return;}

/* set the MPP mode as AIN */

val =(MPP_MODE_AIN <<Q_REG_MODE_SEL_SHIFT)\

|(0x1<<Q_REG_OUT_INVERT_SHIFT)\

|(0x0<<Q_REG_SRC_SEL_SHIFT);

REG_WRITE((MPP_REG_BASE +mpp_num *MPP_REG_RANGE +Q_REG_MODE_CTL),val);

/* Enable the MPP */

val =(MPP_MASTER_ENABLE <<Q_REG_MASTER_EN_SHIFT);

REG_WRITE((MPP_REG_BASE +mpp_num *MPP_REG_RANGE +Q_REG_EN_CTL),val);

/* AIN route to AMUX8 */

val =(0x1<<Q_REG_AIN_ROUTE_SHIFT);//AMUX1

REG_WRITE((MPP_REG_BASE +mpp_num *MPP_REG_RANGE +Q_REG_AIN_CTL),val);

}

Pm8x41_adc.h (dev\pmic\pm8x41\include)

#define MPP_2_CHAN_ID 33

457

457

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?