MMU

MMU(内存管理单元)的功能是将逻辑地址转换成物理地址。其中包括:

- 分段单元,将逻辑地址转换成线性地址;

- 分页单元,将线性地址转换成物理地址;

地址概念:

- 逻辑地址,由段标识符+偏移量组成;

- 线性地址,又称虚拟地址;

- 物理地址,用于内存芯片寻址。

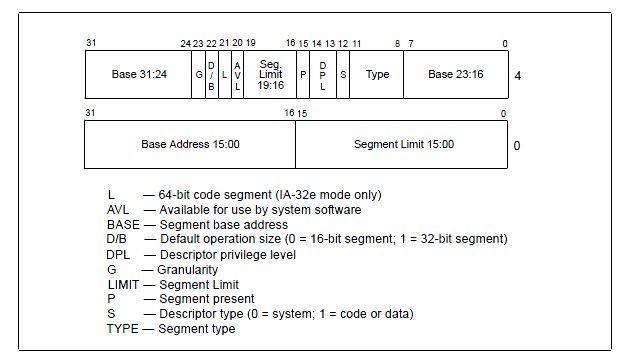

段标识符: | index<15-3> |ti<2> | RPL<1-0> |

段描述符:

(段标识符->index*8+段选择符gdtr或者ldtr寄存器中的基地址) –>得到段描述符–>段描述符->base+offset —>线性地址。

硬件分页

把线性地址分成以固定长度为单位的组。再映射到连续的物理地址中。

- page frame (页框) ram 被分成固定长度

- page 每个页框包含一个页

- page table 线性地址映射到物理地址的数据结构称之为页表

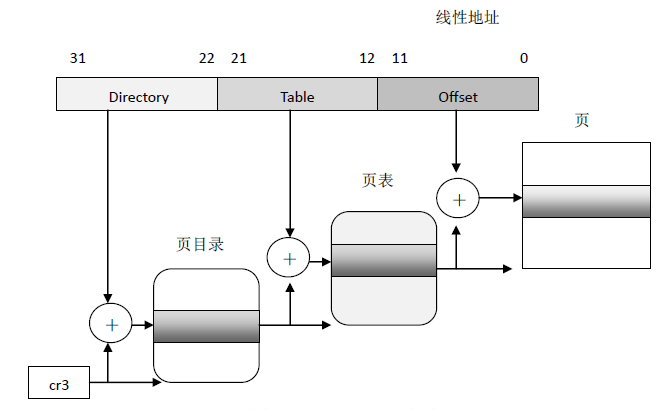

- 常规分页

32位线性地址分为三个域:

Directory 最高10位

Table 中间10位

Offset 最低12位

Directory和Table有相同的数据结构

- present 0 不在主存中(线性地址保存到cr2 产生缺页异常) 1 在主存中

- Accessed

- dirty

- Read/Write 读写执行权限

- User/Supervisor 硬件保护

- PCD/PWT

- Page Size 页大小

- Global

- 扩展分页

Directory 最高10位

Offset 最低22位

页大小由4KB变为4MB

注:cr4 PSE控制分页模式

- 物理扩展分页 PAE

目的: 为了支持4GB以上内存寻址,可高达64GB寻址。

32位线性地址划分为:

cr3 -> PDPT

31-30 指向PDPT4个项中的一个

29-21 页目录512项中的一个

20-12 页表中512项中的一个

11-0 Offset

通过改变cr3 或者 PDPT的值 就可以寻址4GB以上内存

几种加快内存访问速度的技术

-硬件高速缓存

高速缓存在分页单元与主内存之间,有一个高速缓存内存与一个控制器组成。控制器存放着一组缓存表项,每个表项对应着高速缓存内存中的一行,每个表项由一个标签和几个flags组成。每次提出物理地址后,高几位与标签比较,如果一致则命中高速缓存。

-转换后援缓存器(TLB)

目的:加快线性地址到物理地址的转换。在寻址到物理地址后,将物理地址存放在TLB表项中,将来对同一线性地址寻址时,直接从TLB中提取出。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?