快乐虾

http://blog.csdn.net/lights_joy/

lights@hb165.com

本文适用于

ADI bf561 DSP

uclinux-2008r1.5-rc3 (移植到vdsp5)

Visual DSP++ 5.0(update 5)

欢迎转载,但请保留作者信息

/* This section keeps the processor in supervisor mode

* during kernel boot. Switches to user mode at end of boot.

* See page 3-9 of Hardware Reference manual for documentation.

*/

/* EVT15 = _real_start */

p0.l = lo(EVT15);

p0.h = hi(EVT15);

p1.l = _real_start;

p1.h = _real_start;

[p0] = p1;

csync;

p0.l = lo(IMASK);

p0.h = hi(IMASK);

p1.l = IMASK_IVG15;

p1.h = 0x0;

[p0] = p1;

csync;

raise 15;

p0.l = .LWAIT_HERE;

p0.h = .LWAIT_HERE;

reti = p0;

#if ANOMALY_05000281

nop; nop; nop;

#endif

rti;

.LWAIT_HERE:

jump .LWAIT_HERE;

ENDPROC(__start)

这段代码设置了EVT15的入口,打开中断15的掩码,然后直接使用一个软中断,这样在rti之后将跳转到_real_start开始执行。这么做的原因在Hardware Reference manual中说明,看看到底是么回事:

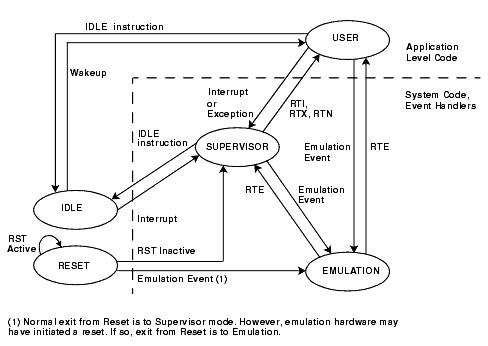

For non-OS environments, application code should remain in Supervisor mode so that it can access all core and system resources. When RESET is de-asserted, the processor initiates operation by servicing the reset event. Emulation is the only event that can pre-empt this activity. Therefore, lower priority events cannot be processed.

One way of keeping the processor in Supervisor mode and still allowing lower priority events to be processed is to set up and force the lowest priority interrupt (IVG15). Events and interrupts are described further in "Events and Sequencing" on another page. After the low priority interrupt has been forced using the RAISE 15 instruction, RETI can be loaded with a return address that points to user code that can execute until IVG15 is issued. After RETI has been loaded, the RTI instruction can be issued to return from the reset event.

The interrupt handler for IVG15 can be set to jump to the application code starting address. An additional RTI is not required. As a result, the processor remains in Supervisor mode because IPEND[15] remains set. At this point, the processor is servicing the lowest priority interrupt. This ensures that higher priority interrupts can be processed.

要理解这段话,先得理解561内核的几种模式及其转换:

在dsp复位后,实际处于RESET的状态,所执行的第一行代码实际是做为reset中断服务例程来运行的,因此在最后使用了一个rti语句结束此中断服务程序,此时将进入user模式,由于在rti之前设置了reti寄存器的值,pc将进入.LWAIT_HERE的这个死循环。又由于之前使用了raise 15触发了一个软中断,因此进入中断15的服务程序,即_real_start。

在使用u-boot引导的时候,由于同样的原因,u-boot的主循环一直是在中断15的服务程序中的,引导内核时同样处于这种状态,此时rti退出的将是u-boot的那个中断服务。

1 参考资料

head.s分析(1):保存u-boot传递过来的指针(2009-1-19)

head.s分析(2):SYSCFG配置(2009-1-19)

head.s分析(3):数据及指针寄存器清0(2009-1-19)

head.s分析(4):关闭CACHE(2009-01-19)

head.s分析(5):关闭串口(2009-01-19)

head.s分析(6):栈指针初始化(2009-01-19)

head.s分析(7):init_early_exception_vectors(2009-1-19)

head.s分析(8):配置PLL及SDRAM(2009-01-20)

head.s分析(9):EBIU配置(2009-01-20)

1730

1730

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?