整理看[《基于FPGA的嵌入式系统设计 – Altera Soc FPGA 》第二版],整理部分很可能有错误。了解FPGA概念参考:认识FPGA Verilog HDL前3段。FPGA(芯片)可被编程配置,如今的EDA为编程配置FPGA提供了许多工具,并遵循着一定的层次设计流程。

0. 总结

(1) 结合EDA对FPGA的学习

- 所有工具的具体用法可参考Quartus II对应版本的 Handbook,结合Altera培训的excise实践。

- FPGA的基础:电子技术基础也。

- 若有条件结合具体的FPGA板子到官网下载FPGA的demo例子实践一把又一把。

(2) 使用FPGA的目的

Quartus II最终会生成到FPGA芯片上的FPGA的配置文件和网表等中途产生的文件。根据设计FPGA的精神,将FPGA配置文件下载到FPGA芯片上后,FPGA芯片就被配置为配置文件所代表的逻辑和功能。

从20世纪90年代末起,在可编程器件内可实现一个用户自定义的系统,这个系统通常包括微处理器(特定的微处理器如Nios II)、片内存储器及外设控制器等。用户自定义的系统经EDA软件产生FPGA配置文件及其它文件,FPGA配置文件用于下载到FPGA芯片内,使芯片被配置为用户所定义的系统的逻辑和功能。用户可以通过FPGA芯片所在开发板来测试所定义的系统是否达到原先所预计的功能。若没有达到,则可通过EDA软件对设计进行修改,生成新的FPGA文件后再重新下载到FPGA芯片内再进行验证。

用户所设计的系统在FPGA开发板上通过验证后,是用具有此系统功能的FPGA芯片还是将EDA软件中所产生网表(或其它文件)拿去给制造芯片的厂家让其加工生成所设计系统,成为新的芯片?对于个体用户来说,采用前者可以省去定制新芯片的费用,只需要将FPGA芯片在各开发板之上移来移去(如果FPGA芯片可以被多次焊接)。但如果是一个公司,需要生产具有所设计系统功能的芯片若干(如用来卖),则第一种方式就不可取:相当于买若干FPGA芯片不说,还要花功夫来编程配置FPGA芯片。所以,需要采用第二种方式,通过EDA产生网表文件,让生产芯片的厂家定制若干本公司所设计的芯片。然后就可以在所定制芯片上下点功夫,开发一个有特定用途的板子(板子的处理器芯片功能刚刚好,比买有功能裕度的芯片划算)卖给有需求的其它小公司,卖出的价格可以由成本外稍加一些劳动、技术费。

1. 使用Quartus II EDA工具 配置FPGA的背景

(1) FPGA与数字电路部分

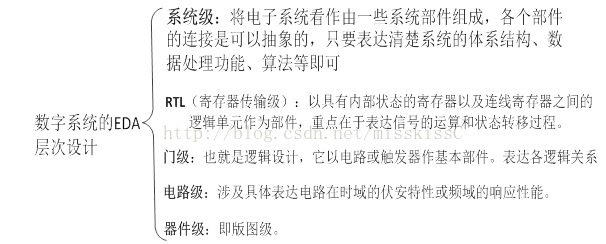

(2) 现代数字系统设计方法

目前,关于数字系统设计的软硬件方面的技术已经较为成熟,数字系统的设计方法称为EDA(Electronic Design Automation, 电子设计自动化)。EDA在数字方面的普及程度比较广泛,而模拟电子的EDA技术正在进入实用阶段。这就是为什么在对数字系统进行设计时会采用如Quartus II、ISE这样的EDA工具软件,进行模电电路设计时会用如AD的工具软件。

2.Quartus II EDA工具设计流程

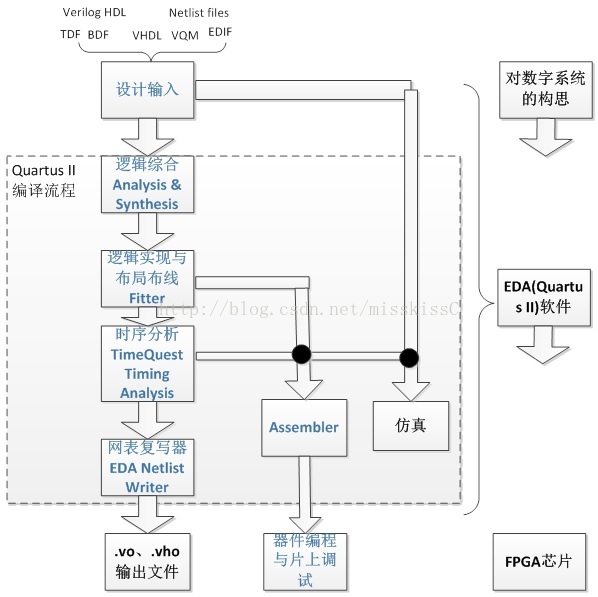

Quartus II EDA工具内部实现了现代数字设计方法中每一级所要求的功能,包含了FPGA和CPLD设计阶段的解决方案。

(1) Quartus II 编程配置FPGA的过程

- 设计输入:所设计的电路以开发要求的某种形式表达出来,并输入到相应的EDA软件中。

- 功能仿真验证:电路设计完毕后,要用专用仿真工具(如ModelSim)对设计进行功能仿真,验证电路是否符合要求。

- 逻辑综合:将设计输入翻译成由与、或、非门、RAM、触发器等基本逻辑单元组成的逻辑连接(网表),并根据目标与要求(约束条件)优化所生成的逻辑连接,输出EDA网表文件,供FPGA厂家的布局布线。

- 逻辑实现与布局布线:逻辑综合的本质是一些由与、或、非门、RAM、触发器等基本逻辑单元组成的逻辑网表,它与实际的配置情况还有较大差距。此时应该用FPGA厂家提供的软件工具,根据所选芯片的型号,将综合输出的逻辑网表适配到具体的FPGA的芯片上。

- 时序仿真与验证:将布局布线的延时信息反标注到设计网表中进行仿真。布局布线后生成的文件不仅包含门延时,还包含实际布线延时,故而布线后的仿真最为准确,能较好的反应芯片的实际工作情况。

- Assembler:产生多种形式的器件编程映像文件,如FPGA芯片的配置文件。

- 器件编程与片上调试:设计开发的最后步骤就是在线调试或者将生成的FPGA配置文件写入芯片中进行测试。示波器和逻辑分析仪是逻辑设计的主要调试工具。

- Netlist Writer:产生用于第三方EDA工具的网表文件及其他输出文件。

每个流程只能接收图示的来自上一层的输出。对每一层的操作都可以提前对它进行操作(Assignments)。

(2) 集成在Quartus II 中的设计工具

现代的EDA软件平台已经突破早期仅能进行PCB版图设计,它集成设计、仿真、测试于一体,配备了系统设计自动化的全部工具。Quartus II软件运行用户在设计流程中的每个阶段使用Quartus II图形界面、EDA工具界面或命令行界面。

[1] Qsys

Qsys集成开发工具是对应于以上提到的系统级设计的工具。实现模块间(遵守协议设计的)的互联。之前要通过手动编码来完成各模块间的互联。

[2] 增量编译

Quartus II的编译过程包含综合、布局布线、时序分析,编程。若是很大的项目,则这个过程会编译几小时甚至是几天。面对大项目只改动一小部分时的编译耗时性,Quartus II提供了增量编译手段(小项目用增量编译反而划不算)。能用上增量编译的前提是项目的设计要为Partition Design,为实现项目的Partition Design,Quartus II也提供了多种方式,也有专门的Partition Design工具。

[3] 功能仿真工具

ModelSim是对应Figure 3中功能仿真,是对设计输入的一个简单仿真,有助于及时纠正设计输入。

[4] 时序分析工具

Quartus II 提供TimeQuest工具来分析时序。为了分析时序,我们需提前了解时序路径、时序约束、sutup、hold等与时序相关的基本概念。

[5] 调试工具

若时序分析得出的结果与设计不符,则就需要对设计进行调试。Quartus II包含的调试工具有SignalTap II, SignalProbe, Chip Planner, RTL Viewer等,不是说使用工具就代表好。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?