2013-12-16

cpu什么时候知道中断产生?

对于51

⑴. 采样

CPU在每个机器周期的S5P2时刻顺序采样每个中断源, 并 置相应标志。 (内部中断请求都发生在芯片内部,直接置位TCON或SCON中的中断请求标志)。

⑵. CPU不能响应中断的条件

下面的任何一个都能封锁CPU对中断的响应:

① CPU正在处理同级的或高一级的中断;

② 现行的机器周期不是当前所执行指令的最后一个机器周期;

③ 当前正在执行的指令是返回(RETI)指令或是对IE或IP寄存器进行读/写的指令。

上述三个条件中,第二条是保证把当前指令执行完,第三条是保证如果在当前执行的是 RETI指令或是对IE、IP进行访问的指令时,必须至少再执行完一条指令之后才会响应中断。

⑶.查询

机器周期S6期间按优先级顺序查询中断标志,如果在前一个机器周期的S5P2有中断标志,则表明有中断请求发生,接着从相邻的下一个机器周期的S1状态开始进行中断响应。

中断查询在每个机器周期中重复执行,所查询到的状态为前一个机器周期的S5P2时采样到的中断标志。

这里要注意的是:如果中断标志被置位,但因上述条件之一的原因而未被响应,或上述封锁条件已撤消,但中断标志位已不 再存在(已不再是置位状态)时;被拖延的中断就不再被响应,CPU将丢弃中断查询的结果。

⑷.中断响应

CPU响应中断时,先置相应的优先级激活触发器,封锁同级和低级的中断。然后根据中断源的类别,在硬件的控制下,程序转向相应的向量入口单元,执行中断服务程序。 硬件调用中断服务程序时,把程序计数器PC的内容压入堆栈(但不能自动保存程序状态字PSW的内容),同时把被响应的中断服务程序的入口地址装入PC中。

⑸. 五个中断源服务程序的入口地址是:

中断源 入口地址

外部中断0 0003H

定时器 0溢出 000BH

外部中断1 0013H

定时器1溢出 001BH

串行口中断 0023H

通常,在中断入口地址处安排一条跳转指令,以跳转到用户的服务程序入口。中断服务程序的最后一条指令必须是中断返回指令 RETI。

CPU执行完这条指令后,把响应中断时所置位的优先级激活触发器清0,然后从堆栈中弹出两个字节内容(断点地址)装入程序计数器PC中;CPU就从原来被中断处重新执行被中断的程序。

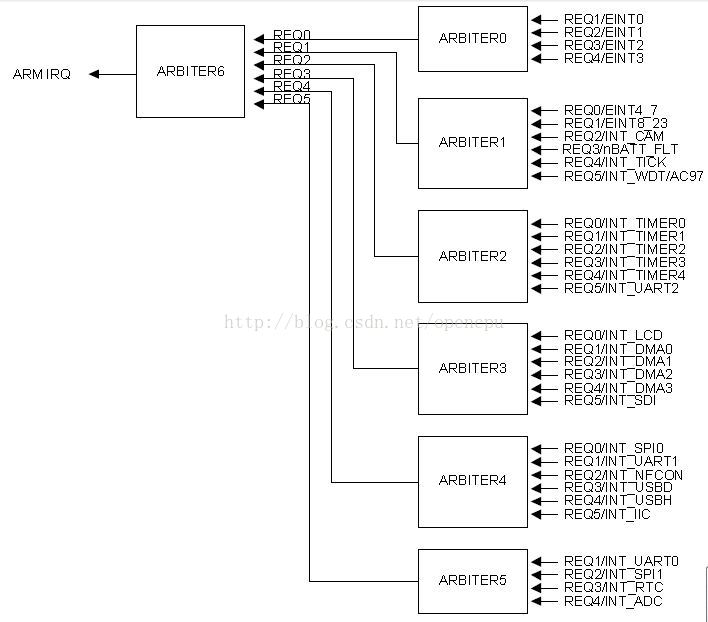

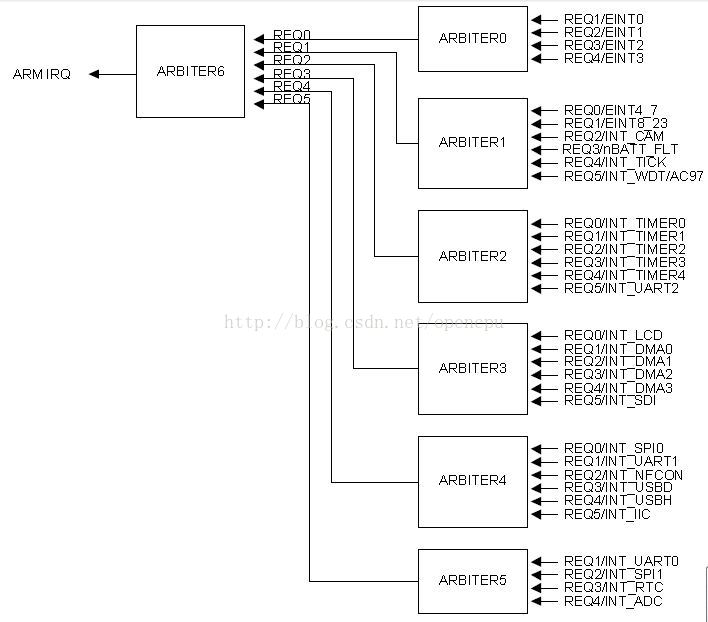

对于arm,与51不同的是,arm(>=9)都有中断控制器来管理大量的中断,所有与中断相关的寄存器都属于中断控制器范围内的。而51呢,相关的那几个中断寄存器都处于51核里面。 arm cpu检测中断的原理与51类似,即每个机器周期去检查一下中断标志寄存器。--待证实。

看来,中断的底层都是用轮询实现的。cpu每个机器周期都在轮询中断标志,只不过是cpu硬件自动的。

refer to

http://blog.sina.com.cn/s/blog_a4cdf30501016n7m.html

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ihi0048a

2013-12-5

1.2440-linux2.6.32

http://blog.csdn.net/ce123_zhouwei/article/details/6940349

arch/arm/mach-s3c2410/include/mach/irqs.h

和2410的7个仲裁器不同,6410分两个,vic0和vic1:

arch/arm/mach-s3c64xx/include/mach/irqs.h

外部中断, 将gpn8配置为为中断为例

1. 将管脚配置为中断

s3c_gpio_cfgpin(S3C64XX_GPN(8), S3C_GPIO_SFN(2));

相当于设置GPN配置寄存器的17:16位,GPNCON 0x7F008830 R/W Port N Configuration Register 0x00

GPN8 [17:16]

00 = Input

01 = Output

10 = Ext. Interrupt[8]

11 = Reserved

2.上拉(可选)

s3c_gpio_setpull(S3C64XX_GPN(8), S3C_GPIO_PULL_UP);

3.申请中断,通过IRQ_EINT(8)获得外部中断8的中断线(号)

ret = request_irq(IRQ_EINT(8), mcp251x_can_irq, /*IRQF_DISABLED |*/ IRQF_TRIGGER_LOW ,DEVICE_NAME, priv);

4.中断处理,里面禁用这个中断(或清除这个中断标志位)

static irqreturn_t mcp251x_can_irq(int irq, void *dev_id)

{

struct mcp251x_priv *priv = dev_id;

disable_irq_nosync(irq);

if (!work_pending(&priv->irq_work))

queue_work(priv->wq, &priv->irq_work);

return IRQ_HANDLED;

}

5.在队列结束时再使能这个中断

enable_irq(irq);

3.mx53-linux2.6.35

arch/arm/plat-mx/include/mach/mx5x.h

外部中断的一个例子

#define MX53_SMD_HEADPHONE_DETECT (5*32 + 16)/* GPIO_6_16 */

//申请gpio

gpio_request(MX53_SMD_HEADPHONE_DETECT, "headphone-dec");

gpio_direction_input(MX53_SMD_HEADPHONE_DETECT);

//申请中断

ret = request_irq(gpio_to_irq(MX53_SMD_HEADPHONE_DETECT), imx_headphone_detect_handler,IRQ_TYPE_EDGE_RISING, pdev->name, priv);

中断处理函数

static irqreturn_t imx_headphone_detect_handler(int irq, void *data)

{

disable_irq(irq);

schedule_delayed_work(&hp_event, msecs_to_jiffies(200));

return IRQ_HANDLED;

}

Chapter 43

IOMUX Controller (IOMUXC)

配置管脚,

比如,对于管脚PATA_DIOR,使用寄存器IOMUXC_SW_MUX_CTL_PAD_PATA_DIOR的第3位来配置:

000 Select mux mode: ALT0 mux port: DIOR of instance: pata.

001 Select mux mode: ALT1 mux port: GPIO[3] of instance: gpio7.

011 Select mux mode: ALT3 mux port: RTS of instance: uart2.

100 Select mux mode: ALT4 mux port: RXCAN of instance: can1.

111 Select mux mode: ALT7 mux port: DATAOUT[7] of instance: usbphy2.

4.hi3518-linux3.0

vgz

5.89c51

fs

cpu什么时候知道中断产生?

对于51

⑴. 采样

CPU在每个机器周期的S5P2时刻顺序采样每个中断源, 并 置相应标志。 (内部中断请求都发生在芯片内部,直接置位TCON或SCON中的中断请求标志)。

⑵. CPU不能响应中断的条件

下面的任何一个都能封锁CPU对中断的响应:

① CPU正在处理同级的或高一级的中断;

② 现行的机器周期不是当前所执行指令的最后一个机器周期;

③ 当前正在执行的指令是返回(RETI)指令或是对IE或IP寄存器进行读/写的指令。

上述三个条件中,第二条是保证把当前指令执行完,第三条是保证如果在当前执行的是 RETI指令或是对IE、IP进行访问的指令时,必须至少再执行完一条指令之后才会响应中断。

⑶.查询

机器周期S6期间按优先级顺序查询中断标志,如果在前一个机器周期的S5P2有中断标志,则表明有中断请求发生,接着从相邻的下一个机器周期的S1状态开始进行中断响应。

中断查询在每个机器周期中重复执行,所查询到的状态为前一个机器周期的S5P2时采样到的中断标志。

这里要注意的是:如果中断标志被置位,但因上述条件之一的原因而未被响应,或上述封锁条件已撤消,但中断标志位已不 再存在(已不再是置位状态)时;被拖延的中断就不再被响应,CPU将丢弃中断查询的结果。

⑷.中断响应

CPU响应中断时,先置相应的优先级激活触发器,封锁同级和低级的中断。然后根据中断源的类别,在硬件的控制下,程序转向相应的向量入口单元,执行中断服务程序。 硬件调用中断服务程序时,把程序计数器PC的内容压入堆栈(但不能自动保存程序状态字PSW的内容),同时把被响应的中断服务程序的入口地址装入PC中。

⑸. 五个中断源服务程序的入口地址是:

中断源 入口地址

外部中断0 0003H

定时器 0溢出 000BH

外部中断1 0013H

定时器1溢出 001BH

串行口中断 0023H

通常,在中断入口地址处安排一条跳转指令,以跳转到用户的服务程序入口。中断服务程序的最后一条指令必须是中断返回指令 RETI。

CPU执行完这条指令后,把响应中断时所置位的优先级激活触发器清0,然后从堆栈中弹出两个字节内容(断点地址)装入程序计数器PC中;CPU就从原来被中断处重新执行被中断的程序。

对于arm,与51不同的是,arm(>=9)都有中断控制器来管理大量的中断,所有与中断相关的寄存器都属于中断控制器范围内的。而51呢,相关的那几个中断寄存器都处于51核里面。 arm cpu检测中断的原理与51类似,即每个机器周期去检查一下中断标志寄存器。--待证实。

看来,中断的底层都是用轮询实现的。cpu每个机器周期都在轮询中断标志,只不过是cpu硬件自动的。

refer to

http://blog.sina.com.cn/s/blog_a4cdf30501016n7m.html

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.ihi0048a

2013-12-5

1.2440-linux2.6.32

http://blog.csdn.net/ce123_zhouwei/article/details/6940349

arch/arm/mach-s3c2410/include/mach/irqs.h

#define S3C2410_CPUIRQ_OFFSET (16)

#define S3C2410_IRQ(x) ((x) + S3C2410_CPUIRQ_OFFSET)

/* main cpu interrupts */

#define IRQ_EINT0 S3C2410_IRQ(0) /* 16 */

#define IRQ_EINT1 S3C2410_IRQ(1)

#define IRQ_EINT2 S3C2410_IRQ(2)

#define IRQ_EINT3 S3C2410_IRQ(3)

#define IRQ_EINT4t7 S3C2410_IRQ(4) /* 20 */

#define IRQ_EINT8t23 S3C2410_IRQ(5)

#define IRQ_RESERVED6 S3C2410_IRQ(6) /* for s3c2410 */

#define IRQ_CAM S3C2410_IRQ(6) /* for s3c2440,s3c2443 */

#define IRQ_BATT_FLT S3C2410_IRQ(7)

#define IRQ_TICK S3C2410_IRQ(8) /* 24 */

#define IRQ_WDT S3C2410_IRQ(9) /* WDT/AC97 for s3c2443 */

#define IRQ_TIMER0 S3C2410_IRQ(10)

#define IRQ_TIMER1 S3C2410_IRQ(11)

#define IRQ_TIMER2 S3C2410_IRQ(12)

#define IRQ_TIMER3 S3C2410_IRQ(13)

#define IRQ_TIMER4 S3C2410_IRQ(14)

#define IRQ_UART2 S3C2410_IRQ(15)

#define IRQ_LCD S3C2410_IRQ(16) /* 32 */

#define IRQ_DMA0 S3C2410_IRQ(17) /* IRQ_DMA for s3c2443 */

#define IRQ_DMA1 S3C2410_IRQ(18)

#define IRQ_DMA2 S3C2410_IRQ(19)

#define IRQ_DMA3 S3C2410_IRQ(20)

#define IRQ_SDI S3C2410_IRQ(21)

#define IRQ_SPI0 S3C2410_IRQ(22)

#define IRQ_UART1 S3C2410_IRQ(23)

#define IRQ_RESERVED24 S3C2410_IRQ(24) /* 40 */

#define IRQ_NFCON S3C2410_IRQ(24) /* for s3c2440 */

#define IRQ_USBD S3C2410_IRQ(25)

#define IRQ_USBH S3C2410_IRQ(26)

#define IRQ_IIC S3C2410_IRQ(27)

#define IRQ_UART0 S3C2410_IRQ(28) /* 44 */

#define IRQ_SPI1 S3C2410_IRQ(29)

#define IRQ_RTC S3C2410_IRQ(30)

#define IRQ_ADCPARENT S3C2410_IRQ(31)

/* interrupts generated from the external interrupts sources */

#define IRQ_EINT4 S3C2410_IRQ(32) /* 48 */

#define IRQ_EINT5 S3C2410_IRQ(33)

#define IRQ_EINT6 S3C2410_IRQ(34)

#define IRQ_EINT7 S3C2410_IRQ(35)

#define IRQ_EINT8 S3C2410_IRQ(36)

#define IRQ_EINT9 S3C2410_IRQ(37)

#define IRQ_EINT10 S3C2410_IRQ(38)

#define IRQ_EINT11 S3C2410_IRQ(39)

#define IRQ_EINT12 S3C2410_IRQ(40)

#define IRQ_EINT13 S3C2410_IRQ(41)

#define IRQ_EINT14 S3C2410_IRQ(42)

#define IRQ_EINT15 S3C2410_IRQ(43)

#define IRQ_EINT16 S3C2410_IRQ(44)

#define IRQ_EINT17 S3C2410_IRQ(45)

#define IRQ_EINT18 S3C2410_IRQ(46)

#define IRQ_EINT19 S3C2410_IRQ(47)

#define IRQ_EINT20 S3C2410_IRQ(48) /* 64 */

#define IRQ_EINT21 S3C2410_IRQ(49)

#define IRQ_EINT22 S3C2410_IRQ(50)

#define IRQ_EINT23 S3C2410_IRQ(51)

#define IRQ_EINT_BIT(x) ((x) - IRQ_EINT4 + 4)

#define IRQ_EINT(x) (((x) >= 4) ? (IRQ_EINT4 + (x) - 4) : (IRQ_EINT0 + (x)))

#define IRQ_LCD_FIFO S3C2410_IRQ(52)

#define IRQ_LCD_FRAME S3C2410_IRQ(53)

/* IRQs for the interal UARTs, and ADC

* these need to be ordered in number of appearance in the

* SUBSRC mask register

*/

#define S3C2410_IRQSUB(x) S3C2410_IRQ((x)+54)

#define IRQ_S3CUART_RX0 S3C2410_IRQSUB(0) /* 70 */

#define IRQ_S3CUART_TX0 S3C2410_IRQSUB(1)

#define IRQ_S3CUART_ERR0 S3C2410_IRQSUB(2)

#define IRQ_S3CUART_RX1 S3C2410_IRQSUB(3) /* 73 */

#define IRQ_S3CUART_TX1 S3C2410_IRQSUB(4)

#define IRQ_S3CUART_ERR1 S3C2410_IRQSUB(5)

#define IRQ_S3CUART_RX2 S3C2410_IRQSUB(6) /* 76 */

#define IRQ_S3CUART_TX2 S3C2410_IRQSUB(7)

#define IRQ_S3CUART_ERR2 S3C2410_IRQSUB(8)

#define IRQ_TC S3C2410_IRQSUB(9)

#define IRQ_ADC S3C2410_IRQSUB(10)

/* extra irqs for s3c2412 */

#define IRQ_S3C2412_CFSDI S3C2410_IRQ(21)

#define IRQ_S3C2412_SDI S3C2410_IRQSUB(13)

#define IRQ_S3C2412_CF S3C2410_IRQSUB(14)

/* extra irqs for s3c2440 */

#define IRQ_S3C2440_CAM_C S3C2410_IRQSUB(11) /* S3C2443 too */

#define IRQ_S3C2440_CAM_P S3C2410_IRQSUB(12) /* S3C2443 too */

#define IRQ_S3C2440_WDT S3C2410_IRQSUB(13)

#define IRQ_S3C2440_AC97 S3C2410_IRQSUB(14)

/* irqs for s3c2443 */

#define IRQ_S3C2443_DMA S3C2410_IRQ(17) /* IRQ_DMA1 */

#define IRQ_S3C2443_UART3 S3C2410_IRQ(18) /* IRQ_DMA2 */

#define IRQ_S3C2443_CFCON S3C2410_IRQ(19) /* IRQ_DMA3 */

#define IRQ_S3C2443_HSMMC S3C2410_IRQ(20) /* IRQ_SDI */

#define IRQ_S3C2443_NAND S3C2410_IRQ(24) /* reserved */

#define IRQ_HSMMC0 IRQ_S3C2443_HSMMC

#define IRQ_S3C2443_LCD1 S3C2410_IRQSUB(14)

#define IRQ_S3C2443_LCD2 S3C2410_IRQSUB(15)

#define IRQ_S3C2443_LCD3 S3C2410_IRQSUB(16)

#define IRQ_S3C2443_LCD4 S3C2410_IRQSUB(17)

#define IRQ_S3C2443_DMA0 S3C2410_IRQSUB(18)

#define IRQ_S3C2443_DMA1 S3C2410_IRQSUB(19)

#define IRQ_S3C2443_DMA2 S3C2410_IRQSUB(20)

#define IRQ_S3C2443_DMA3 S3C2410_IRQSUB(21)

#define IRQ_S3C2443_DMA4 S3C2410_IRQSUB(22)

#define IRQ_S3C2443_DMA5 S3C2410_IRQSUB(23)

/* UART3 */

#define IRQ_S3C2443_RX3 S3C2410_IRQSUB(24)

#define IRQ_S3C2443_TX3 S3C2410_IRQSUB(25)

#define IRQ_S3C2443_ERR3 S3C2410_IRQSUB(26)

#define IRQ_S3C2443_WDT S3C2410_IRQSUB(27)

#define IRQ_S3C2443_AC97 S3C2410_IRQSUB(28)一个外部中断的例子,将GPG(0)配置为外部中断8

1.将管脚配置为中断

s3c2410_gpio_setpin(S3C2410_GPG(0),S3C2410_GPIO_IRQ)

GPG0 [1:0] 00 = 输入 01 = 输出 10 = EINT[8] 11 = 保留

2.申请中断

err = request_irq(IRQ_EINT8, buttons_interrupt, IRQ_TYPE_EDGE_BOTH, “eint8name”, (void *)&button_irqs[i]);

3.中断处理函数

static irqreturn_t buttons_interrupt(int irq, void *dev_id)

{

return IRQ_RETVAL(IRQ_HANDLED);

}

和2410的7个仲裁器不同,6410分两个,vic0和vic1:

arch/arm/mach-s3c64xx/include/mach/irqs.h

define S3C_IRQ_OFFSET (32)

#define S3C_IRQ(x) ((x) + S3C_IRQ_OFFSET)

#define IRQ_VIC0_BASE S3C_IRQ(0)

#define IRQ_VIC1_BASE S3C_IRQ(32)

/* UART interrupts, each UART has 4 intterupts per channel so

* use the space between the ISA and S3C main interrupts. Note, these

* are not in the same order as the S3C24XX series! */

#define IRQ_S3CUART_BASE0 (16)

#define IRQ_S3CUART_BASE1 (20)

#define IRQ_S3CUART_BASE2 (24)

#define IRQ_S3CUART_BASE3 (28)

#define UART_IRQ_RXD (0)

#define UART_IRQ_ERR (1)

#define UART_IRQ_TXD (2)

#define UART_IRQ_MODEM (3)

#define IRQ_S3CUART_RX0 (IRQ_S3CUART_BASE0 + UART_IRQ_RXD)

#define IRQ_S3CUART_TX0 (IRQ_S3CUART_BASE0 + UART_IRQ_TXD)

#define IRQ_S3CUART_ERR0 (IRQ_S3CUART_BASE0 + UART_IRQ_ERR)

#define IRQ_S3CUART_RX1 (IRQ_S3CUART_BASE1 + UART_IRQ_RXD)

#define IRQ_S3CUART_TX1 (IRQ_S3CUART_BASE1 + UART_IRQ_TXD)

#define IRQ_S3CUART_ERR1 (IRQ_S3CUART_BASE1 + UART_IRQ_ERR)

#define IRQ_S3CUART_RX2 (IRQ_S3CUART_BASE2 + UART_IRQ_RXD)

#define IRQ_S3CUART_TX2 (IRQ_S3CUART_BASE2 + UART_IRQ_TXD)

#define IRQ_S3CUART_ERR2 (IRQ_S3CUART_BASE2 + UART_IRQ_ERR)

#define IRQ_S3CUART_RX3 (IRQ_S3CUART_BASE3 + UART_IRQ_RXD)

#define IRQ_S3CUART_TX3 (IRQ_S3CUART_BASE3 + UART_IRQ_TXD)

#define IRQ_S3CUART_ERR3 (IRQ_S3CUART_BASE3 + UART_IRQ_ERR)

/* VIC based IRQs */

#define S3C64XX_IRQ_VIC0(x) (IRQ_VIC0_BASE + (x))

#define S3C64XX_IRQ_VIC1(x) (IRQ_VIC1_BASE + (x))

/* VIC0 */

#define IRQ_EINT0_3 S3C64XX_IRQ_VIC0(0)

#define IRQ_EINT4_11 S3C64XX_IRQ_VIC0(1)

#define IRQ_RTC_TIC S3C64XX_IRQ_VIC0(2)

#define IRQ_CAMIF_C S3C64XX_IRQ_VIC0(3)

#define IRQ_CAMIF_P S3C64XX_IRQ_VIC0(4)

#define IRQ_CAMIF_MC S3C64XX_IRQ_VIC0(5)

#define IRQ_S3C6410_IIC1 S3C64XX_IRQ_VIC0(5)

#define IRQ_S3C6410_IIS S3C64XX_IRQ_VIC0(6)

#define IRQ_S3C6400_CAMIF_MP S3C64XX_IRQ_VIC0(6)

#define IRQ_CAMIF_WE_C S3C64XX_IRQ_VIC0(7)

#define IRQ_S3C6410_G3D S3C64XX_IRQ_VIC0(8)

#define IRQ_S3C6400_CAMIF_WE_P S3C64XX_IRQ_VIC0(8)

#define IRQ_POST0 S3C64XX_IRQ_VIC0(9)

#define IRQ_ROTATOR S3C64XX_IRQ_VIC0(10)

#define IRQ_2D S3C64XX_IRQ_VIC0(11)

#define IRQ_TVENC S3C64XX_IRQ_VIC0(12)

#define IRQ_SCALER S3C64XX_IRQ_VIC0(13)

#define IRQ_BATF S3C64XX_IRQ_VIC0(14)

#define IRQ_JPEG S3C64XX_IRQ_VIC0(15)

#define IRQ_MFC S3C64XX_IRQ_VIC0(16)

#define IRQ_SDMA0 S3C64XX_IRQ_VIC0(17)

#define IRQ_SDMA1 S3C64XX_IRQ_VIC0(18)

#define IRQ_ARM_DMAERR S3C64XX_IRQ_VIC0(19)

#define IRQ_ARM_DMA S3C64XX_IRQ_VIC0(20)

#define IRQ_ARM_DMAS S3C64XX_IRQ_VIC0(21)

#define IRQ_KEYPAD S3C64XX_IRQ_VIC0(22)

#define IRQ_TIMER0_VIC S3C64XX_IRQ_VIC0(23)

#define IRQ_TIMER1_VIC S3C64XX_IRQ_VIC0(24)

#define IRQ_TIMER2_VIC S3C64XX_IRQ_VIC0(25)

#define IRQ_WDT S3C64XX_IRQ_VIC0(26)

#define IRQ_TIMER3_VIC S3C64XX_IRQ_VIC0(27)

#define IRQ_TIMER4_VIC S3C64XX_IRQ_VIC0(28)

#define IRQ_LCD_FIFO S3C64XX_IRQ_VIC0(29)

#define IRQ_LCD_VSYNC S3C64XX_IRQ_VIC0(30)

#define IRQ_LCD_SYSTEM S3C64XX_IRQ_VIC0(31)

/* VIC1 */

#define IRQ_EINT12_19 S3C64XX_IRQ_VIC1(0)

#define IRQ_EINT20_27 S3C64XX_IRQ_VIC1(1)

#define IRQ_PCM0 S3C64XX_IRQ_VIC1(2)

#define IRQ_PCM1 S3C64XX_IRQ_VIC1(3)

#define IRQ_AC97 S3C64XX_IRQ_VIC1(4)

#define IRQ_UART0 S3C64XX_IRQ_VIC1(5)

#define IRQ_UART1 S3C64XX_IRQ_VIC1(6)

#define IRQ_UART2 S3C64XX_IRQ_VIC1(7)

#define IRQ_UART3 S3C64XX_IRQ_VIC1(8)

#define IRQ_DMA0 S3C64XX_IRQ_VIC1(9)

#define IRQ_DMA1 S3C64XX_IRQ_VIC1(10)

#define IRQ_ONENAND0 S3C64XX_IRQ_VIC1(11)

#define IRQ_ONENAND1 S3C64XX_IRQ_VIC1(12)

#define IRQ_NFC S3C64XX_IRQ_VIC1(13)

#define IRQ_CFCON S3C64XX_IRQ_VIC1(14)

#define IRQ_USBH S3C64XX_IRQ_VIC1(15)

#define IRQ_SPI0 S3C64XX_IRQ_VIC1(16)

#define IRQ_SPI1 S3C64XX_IRQ_VIC1(17)

#define IRQ_IIC S3C64XX_IRQ_VIC1(18)

#define IRQ_HSItx S3C64XX_IRQ_VIC1(19)

#define IRQ_HSIrx S3C64XX_IRQ_VIC1(20)

#define IRQ_RESERVED S3C64XX_IRQ_VIC1(21)

#define IRQ_MSM S3C64XX_IRQ_VIC1(22)

#define IRQ_HOSTIF S3C64XX_IRQ_VIC1(23)

#define IRQ_HSMMC0 S3C64XX_IRQ_VIC1(24)

#define IRQ_HSMMC1 S3C64XX_IRQ_VIC1(25)

#define IRQ_HSMMC2 IRQ_SPI1 /* shared with SPI1 */

#define IRQ_OTG S3C64XX_IRQ_VIC1(26)

#define IRQ_IRDA S3C64XX_IRQ_VIC1(27)

#define IRQ_RTC_ALARM S3C64XX_IRQ_VIC1(28)

#define IRQ_SEC S3C64XX_IRQ_VIC1(29)

#define IRQ_PENDN S3C64XX_IRQ_VIC1(30)

#define IRQ_TC IRQ_PENDN

#define IRQ_ADC S3C64XX_IRQ_VIC1(31)

#define S3C64XX_TIMER_IRQ(x) S3C_IRQ(64 + (x))

#define IRQ_TIMER0 S3C64XX_TIMER_IRQ(0)

#define IRQ_TIMER1 S3C64XX_TIMER_IRQ(1)

#define IRQ_TIMER2 S3C64XX_TIMER_IRQ(2)

#define IRQ_TIMER3 S3C64XX_TIMER_IRQ(3)

#define IRQ_TIMER4 S3C64XX_TIMER_IRQ(4)

/* compatibility for device defines */

#define IRQ_IIC1 IRQ_S3C6410_IIC1

/* Since the IRQ_EINT(x) are a linear mapping on current s3c64xx series

* we just defined them as an IRQ_EINT(x) macro from S3C_IRQ_EINT_BASE

* which we place after the pair of VICs. */

#define S3C_IRQ_EINT_BASE S3C_IRQ(64+5)

#define S3C_EINT(x) ((x) + S3C_IRQ_EINT_BASE)

#define IRQ_EINT(x) S3C_EINT(x)

#define IRQ_EINT_BIT(x) ((x) - S3C_EINT(0))

/* Next the external interrupt groups. These are similar to the IRQ_EINT(x)

* that they are sourced from the GPIO pins but with a different scheme for

* priority and source indication.

*

* The IRQ_EINT(x) can be thought of as 'group 0' of the available GPIO

* interrupts, but for historical reasons they are kept apart from these

* next interrupts.

*

* Use IRQ_EINT_GROUP(group, offset) to get the number for use in the

* machine specific support files.

*/

#define IRQ_EINT_GROUP1_NR (15)

#define IRQ_EINT_GROUP2_NR (8)

#define IRQ_EINT_GROUP3_NR (5)

#define IRQ_EINT_GROUP4_NR (14)

#define IRQ_EINT_GROUP5_NR (7)

#define IRQ_EINT_GROUP6_NR (10)

#define IRQ_EINT_GROUP7_NR (16)

#define IRQ_EINT_GROUP8_NR (15)

#define IRQ_EINT_GROUP9_NR (9)

#define IRQ_EINT_GROUP_BASE S3C_EINT(28)

#define IRQ_EINT_GROUP1_BASE (IRQ_EINT_GROUP_BASE + 0x00)

#define IRQ_EINT_GROUP2_BASE (IRQ_EINT_GROUP1_BASE + IRQ_EINT_GROUP1_NR)

#define IRQ_EINT_GROUP3_BASE (IRQ_EINT_GROUP2_BASE + IRQ_EINT_GROUP2_NR)

#define IRQ_EINT_GROUP4_BASE (IRQ_EINT_GROUP3_BASE + IRQ_EINT_GROUP3_NR)

#define IRQ_EINT_GROUP5_BASE (IRQ_EINT_GROUP4_BASE + IRQ_EINT_GROUP4_NR)

#define IRQ_EINT_GROUP6_BASE (IRQ_EINT_GROUP5_BASE + IRQ_EINT_GROUP5_NR)

#define IRQ_EINT_GROUP7_BASE (IRQ_EINT_GROUP6_BASE + IRQ_EINT_GROUP6_NR)

#define IRQ_EINT_GROUP8_BASE (IRQ_EINT_GROUP7_BASE + IRQ_EINT_GROUP7_NR)

#define IRQ_EINT_GROUP9_BASE (IRQ_EINT_GROUP8_BASE + IRQ_EINT_GROUP8_NR)外部中断, 将gpn8配置为为中断为例

1. 将管脚配置为中断

s3c_gpio_cfgpin(S3C64XX_GPN(8), S3C_GPIO_SFN(2));

相当于设置GPN配置寄存器的17:16位,GPNCON 0x7F008830 R/W Port N Configuration Register 0x00

GPN8 [17:16]

00 = Input

01 = Output

10 = Ext. Interrupt[8]

11 = Reserved

2.上拉(可选)

s3c_gpio_setpull(S3C64XX_GPN(8), S3C_GPIO_PULL_UP);

3.申请中断,通过IRQ_EINT(8)获得外部中断8的中断线(号)

ret = request_irq(IRQ_EINT(8), mcp251x_can_irq, /*IRQF_DISABLED |*/ IRQF_TRIGGER_LOW ,DEVICE_NAME, priv);

4.中断处理,里面禁用这个中断(或清除这个中断标志位)

static irqreturn_t mcp251x_can_irq(int irq, void *dev_id)

{

struct mcp251x_priv *priv = dev_id;

disable_irq_nosync(irq);

if (!work_pending(&priv->irq_work))

queue_work(priv->wq, &priv->irq_work);

return IRQ_HANDLED;

}

5.在队列结束时再使能这个中断

enable_irq(irq);

3.mx53-linux2.6.35

arch/arm/plat-mx/include/mach/mx5x.h

/*

* Interrupt numbers

*/

#define MXC_INT_BASE 0

#define MXC_INT_RESV0 0

#define MXC_INT_MMC_SDHC1 1

#define MXC_INT_MMC_SDHC2 2

#define MXC_INT_MMC_SDHC3 3

#define MXC_INT_MMC_SDHC4 4

#define MXC_INT_DAP 5

#define MXC_INT_SDMA 6

#define MXC_INT_IOMUX 7

#define MXC_INT_NFC 8

#define MXC_INT_VPU 9

#define MXC_INT_IPU_ERR 10

#define MXC_INT_IPU_SYN 11

#define MXC_INT_GPU 12

#define MXC_INT_UART4 13

#define MXC_INT_USB_H1 14

#define MXC_INT_EMI 15

#define MXC_INT_USB_H2 16

#define MXC_INT_USB_H3 17

#define MXC_INT_USB_OTG 18

#define MXC_INT_SAHARA_H0 19

#define MXC_INT_DATABAHN 19 /* MX50 */

#define MXC_INT_SAHARA_H1 20

#define MXC_INT_ELCDIF 20 /* MX50 */

#define MXC_INT_SCC_SMN 21

#define MXC_INT_EPXP 21 /* MX50 */

#define MXC_INT_SCC_STZ 22

#define MXC_INT_SCC_SCM 23

#define MXC_INT_SRTC_NTZ 24

#define MXC_INT_SRTC_TZ 25

#define MXC_INT_RTIC 26

#define MXC_INT_CSU 27

#define MXC_INT_EPDC 27 /* MX50 */

#define MXC_INT_SATA 28

#define MXC_INT_SLIM_B 28 /* MX51 */

#define MXC_INT_NIC 28 /* MX50 Perfmon IRQ */

#define MXC_INT_SSI1 29

#define MXC_INT_SSI2 30

#define MXC_INT_UART1 31

#define MXC_INT_UART2 32

#define MXC_INT_UART3 33

#define MXC_INT_RTC 34

#define MXC_INT_PTP 35

#define MXC_INT_CSPI1 36

#define MXC_INT_CSPI2 37

#define MXC_INT_CSPI 38

#define MXC_INT_GPT 39

#define MXC_INT_EPIT1 40

#define MXC_INT_EPIT2 41

#define MXC_INT_GPIO1_INT7 42

#define MXC_INT_GPIO1_INT6 43

#define MXC_INT_GPIO1_INT5 44

#define MXC_INT_GPIO1_INT4 45

#define MXC_INT_GPIO1_INT3 46

#define MXC_INT_GPIO1_INT2 47

#define MXC_INT_GPIO1_INT1 48

#define MXC_INT_GPIO1_INT0 49

#define MXC_INT_GPIO1_LOW 50

#define MXC_INT_GPIO1_HIGH 51

#define MXC_INT_GPIO2_LOW 52

#define MXC_INT_GPIO2_HIGH 53

#define MXC_INT_GPIO3_LOW 54

#define MXC_INT_GPIO3_HIGH 55

#define MXC_INT_GPIO4_LOW 56

#define MXC_INT_GPIO4_HIGH 57

#define MXC_INT_WDOG1 58

#define MXC_INT_WDOG2 59

#define MXC_INT_KPP 60

#define MXC_INT_PWM1 61

#define MXC_INT_I2C1 62

#define MXC_INT_I2C2 63

#define MXC_INT_I2C3 64

#define MXC_INT_HS_I2C 64 /* MX51 */

#define MXC_INT_MLB 65

#define MXC_INT_ASRC 66

#define MXC_INT_SPDIF_MX53 67

#define MXC_INT_SIM_IPB 67

#define MXC_INT_SIM_DAT 68

#define MXC_INT_IIM 69

#define MXC_INT_ANATOP1 66 /* MX50 what's it? */

#define MXC_INT_ANATOP2 67

#define MXC_INT_ANATOP3 68

#define MXC_INT_ANATOP4 69

#define MXC_INT_ATA 70

#define MXC_INT_CCM1 71

#define MXC_INT_CCM2 72

#define MXC_INT_GPC1 73

#define MXC_INT_GPC2 74

#define MXC_INT_SRC 75

#define MXC_INT_NM 76

#define MXC_INT_PMU 77

#define MXC_INT_CTI_IRQ 78

#define MXC_INT_CTI1_TG0 79

#define MXC_INT_CTI1_TG1 80

#define MXC_INT_ESAI 81

#define MXC_INT_CAN1 82

#define MXC_INT_CAN2 83

#define MXC_INT_MCG_ERR 81 /* MX51 */

#define MXC_INT_MCG_TMR 82 /* MX51 */

#define MXC_INT_MCG_FUNC 83 /* MX51 */

#define MXC_INT_GPU2_IRQ 84

#define MXC_INT_GPU2_BUSY 85

#define MXC_INT_UART5 86

#define MXC_INT_FEC 87

#define MXC_INT_OWIRE 88

#define MXC_INT_CTI1_TG2 89

#define MXC_INT_SJC 90

#define MXC_INT_SPDIF_MX51 91

#define MXC_INT_DCP_CHAN1_3 91 /* MX50 */

#define MXC_INT_TVE 92

#define MXC_INT_DCP_CHAN0 92 /* MX50 */

#define MXC_INT_FIRI 93

#define MXC_INT_DCP_CHAN0_3_SEC 93 /* MX50 */

#define MXC_INT_PWM2 94

#define MXC_INT_SLIM_EXP 95

#define MXC_INT_SSI3 96

#define MXC_INT_EMI_BOOT 97

#define MXC_INT_RNGB_BLOCK 97 /* MX50 */

#define MXC_INT_CTI1_TG3 98

#define MXC_INT_SMC_RX 99

#define MXC_INT_VPU_IDLE 100

#define MXC_INT_RAWNAND_BCH 100 /* MX50 */

#define MXC_INT_EMI_NFC 101

#define MXC_INT_GPU_IDLE 102

#define MXC_INT_RAWNAND_GPMI 102 /* MX50 */

#define MXC_INT_GPIO5_LOW 103

#define MXC_INT_GPIO5_HIGH 104

#define MXC_INT_GPIO6_LOW 105

#define MXC_INT_GPIO6_HIGH 106

#define MXC_INT_GPIO7_LOW 107

#define MXC_INT_GPIO7_HIGH 108

#define MXC_INT_MSHC 109 /* MX50 */

#define MXC_INT_APBHDMA_CHAN0 110

#define MXC_INT_APBHDMA_CHAN1 111

#define MXC_INT_APBHDMA_CHAN2 112

#define MXC_INT_APBHDMA_CHAN3 113

#define MXC_INT_APBHDMA_CHAN4 114

#define MXC_INT_APBHDMA_CHAN5 115

#define MXC_INT_APBHDMA_CHAN6 116

#define MXC_INT_APBHDMA_CHAN7 117

#define MXC_INT_APBHDMA_CHAN8 118

#define MXC_INT_APBHDMA_CHAN9 119

#define MXC_INT_APBHDMA_CHAN10 120

#define MXC_INT_APBHDMA_CHAN11 121

#define MXC_INT_APBHDMA_CHAN12 122

#define MXC_INT_APBHDMA_CHAN13 123

#define MXC_INT_APBHDMA_CHAN14 124

#define MXC_INT_APBHDMA_CHAN15 125外部中断的一个例子

#define MX53_SMD_HEADPHONE_DETECT (5*32 + 16)/* GPIO_6_16 */

//申请gpio

gpio_request(MX53_SMD_HEADPHONE_DETECT, "headphone-dec");

gpio_direction_input(MX53_SMD_HEADPHONE_DETECT);

//申请中断

ret = request_irq(gpio_to_irq(MX53_SMD_HEADPHONE_DETECT), imx_headphone_detect_handler,IRQ_TYPE_EDGE_RISING, pdev->name, priv);

中断处理函数

static irqreturn_t imx_headphone_detect_handler(int irq, void *data)

{

disable_irq(irq);

schedule_delayed_work(&hp_event, msecs_to_jiffies(200));

return IRQ_HANDLED;

}

Chapter 43

IOMUX Controller (IOMUXC)

配置管脚,

比如,对于管脚PATA_DIOR,使用寄存器IOMUXC_SW_MUX_CTL_PAD_PATA_DIOR的第3位来配置:

000 Select mux mode: ALT0 mux port: DIOR of instance: pata.

001 Select mux mode: ALT1 mux port: GPIO[3] of instance: gpio7.

011 Select mux mode: ALT3 mux port: RTS of instance: uart2.

100 Select mux mode: ALT4 mux port: RXCAN of instance: can1.

111 Select mux mode: ALT7 mux port: DATAOUT[7] of instance: usbphy2.

4.hi3518-linux3.0

vgz

5.89c51

fs

1701

1701

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?