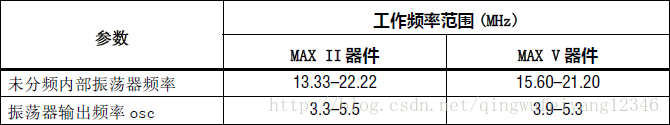

我们在进行CPLD设计时,时钟是一个比不可少的环节,一般使用外部有源振荡器加以实现,这样会占用一定的体积。CPLD的MAX II和V系列带有UFM可以实现内部振荡,其频率如下图所示。其中第1行为内部振荡频率,第2行为4分屏后的输出频率。在这里需要注意的是,振荡频率只是一个范围,并不能确定其精准频率。使用这个频率作为CPLD的工作频率是可以的,但是当做精确定时等频率是不合适的。

本文将介绍在MAX V器件中,使用CPLD内部振荡器的方法,本例程所选的器件为EPM40ZE64C5N,本例程使用的电路图可参看《Verilog学习笔记11》。

1、按照《Verilog学习笔记10》所述的方法,使用工程向导建立工程文件。

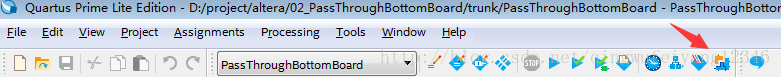

2、点击IP Catalog按钮,打开IP分类。

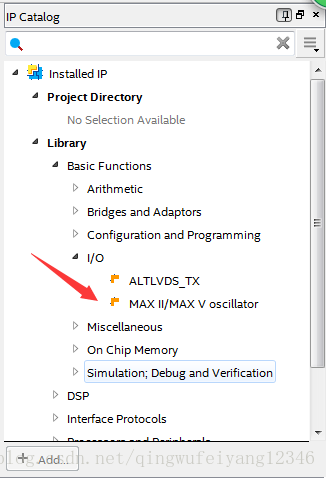

3、在IP Catalog中的Library-Basic Function-I/O-MAX II/MAX V oscillator,双击该选项。

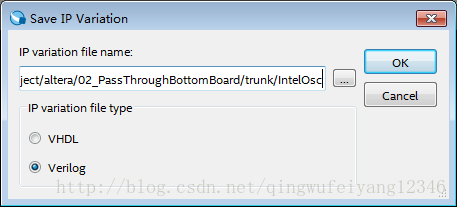

4、在接下来出现的对话框中输入IP核的文件名,本工程取名为IntelOsc,并选择Verilog语言,然后点击OK按钮。

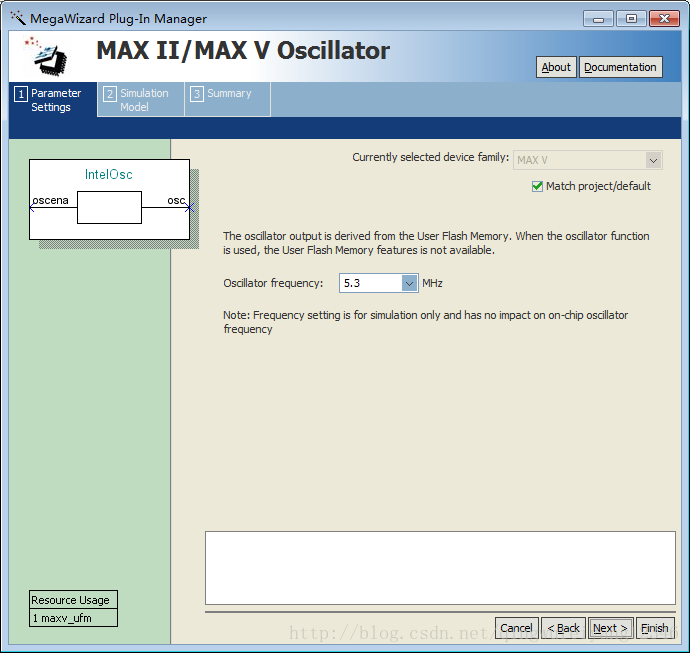

5、在接下来出现的对话框中,我们可以看到该晶振的接线图,由2条外部线组成,oscena为内部晶振使能线,osc为晶振输出线,oscena给1时使能晶振输出。对话框的晶振频率只用于Quartus Prime的仿真,实际的振荡频率由芯片本身决定,和此值无关。以上信息确认后,我们点击Next按钮,进入下一个对话框。

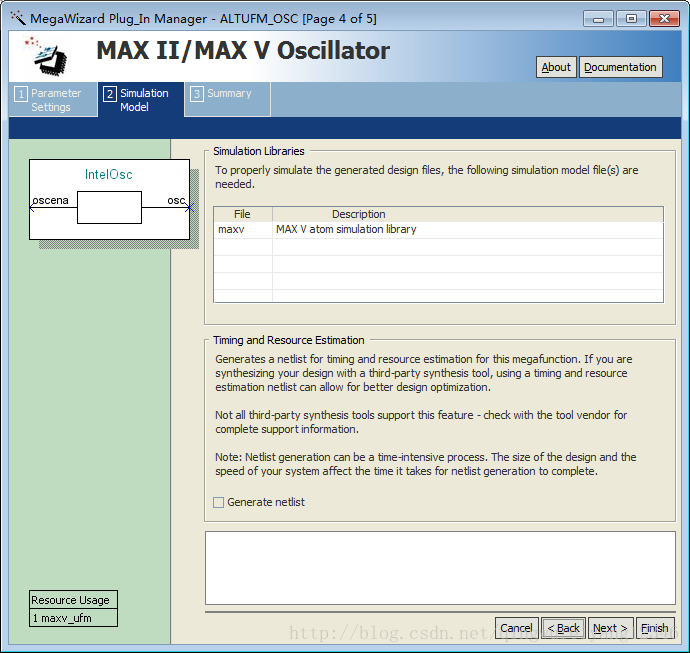

6、下一个对话框用于仿真模式的指定,我们直接点击Next按钮即可。

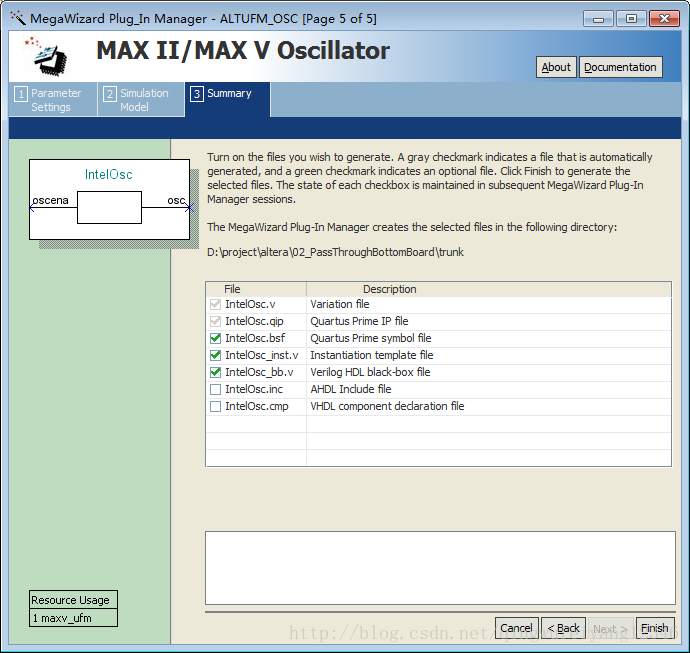

7、下一个对话框用于指定生成的文件,我们选择需要的即可,一切完成后,点击Finish按钮。

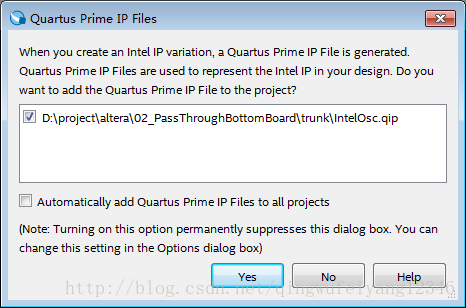

8、在接下来出现的对话框中,询问IP核是否加入工程文件,我们点击Yes按钮。

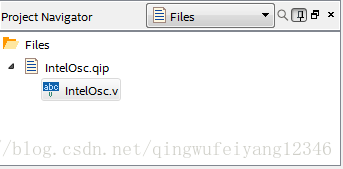

9、以上步骤结束后,我们就完成了内部晶振的设置,我们可以在Project Navigator中看到内部晶振所对应的Verilog文件。

10、接下来,我们进行程序设计,新建Verilog文件,输入如下程序,对程序的讲解,我们稍后进行。

module PassThroughBottomBoard(led);

output[7:1] led;

reg[7:1] led;

reg[19:0] count;

wire cscena = 1'b1;

wire clk;

IntelOsc IntelOsc(cscena, clk);

always @(posedge clk)

begin

count <= count + 1'b1;

if (count == 1'b0)

begin

led <= ~led;

end

end

endmodule 12、编译成功后,需进行引脚设置,一定还要记住设置未使用引脚。

13、进行再次编译后,就可以下载程序了,一切顺利的话,应看到7个led快速闪烁。

程序注释:

1、reg[7:1] led;

reg类型是一种能暂存数据的变量,可以在时序电路中对应具有状态保持作用的电路元件,如触发器、寄存器等,reg类型必须放在过程快(如always、inital)中通过过程赋值语句赋值。此句的作用是将led声明为reg类型,在always中调用,当事件发生时,进行赋值变化,否则,则维持原有的状态。

2、reg[19:0] count;

此句是将count声明为reg类型,位宽是20,用于计数。

3、wire cscena = 1'b1;

wire型使用Verilog中最常用的数据类型,相当于组合逻辑电路中的连接线,其特点是输出值紧随输入值的变化而变化,不能暂存。此句的作用是将cscena变量设置为wire型,并赋值为1,cscena是内部晶振的使能引脚,输入1则使能内部晶振。

4、wire clk;

此句的作用是将clk变量设置为wire型,它是内部晶振的输出引脚,后续程序可以将该引脚的输出信号当作晶振使用,其振荡频率对于MAX V器件爱你来说此句的作用是将clk变量设置为wire型,它是内部晶振的输出引脚,后续程序可以将该引脚的输出信号当作晶振使用,其振荡频率对于MAX V期间来说在3.9M-5.3M之间。

5、IntelOsc IntelOsc(cscena, clk);

调用内部晶振,使能其输出。

6、always @(posedge clk)

使用always语句的程序为行为描述,always具有循环等待的含义,即循环等待小括号中的敏感信号发生变化时,才执行后续begin到end中的语句。posedge为下降沿的意思,整句话的意思当时钟clk的下降沿发生时才执行后续的语句。

7、count <= count + 1'b1;

count变量自加1,每次时钟下降沿发生count变量都加1,由于count变量为20位,所以加到1024*1024时,count会变为0。

8、if (count == 1'b0)

begin

led <= ~led;

end

当count为0时,led反转,也就是count加到1024*1024时,led反转,仔细分析当前程序就可以知道实际上是内部晶振的1024*1024分频程序。由于当前器件的频率为3.9M-5.3M,1024*1024分频后,其频率为3.9-5.3Hz。

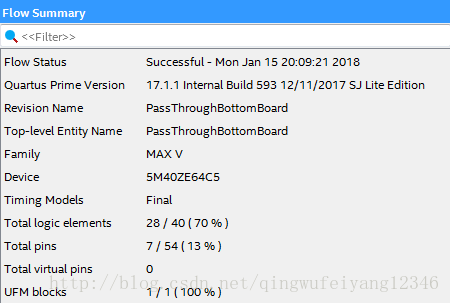

本文介绍了内部晶振的使用方法,该晶振对于快速响应是非常使用的,但是当需要长延时的时候,就需要消耗大量的器件资源,从下图就可以看出,本例程使用的器件为5M40ZE64C5N,仅作1024*1024分频,就消耗了70%的能量。

转载请注明出处:CSDN:http://blog.csdn.net/qingwufeiyang12346。

1827

1827

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?